# 高性能的低电流收发器

### 特点

- 频率范围 = 425-525 MHz

- 接收灵敏度 = -124 dBm

- 调制

- (G)FSK

- OOK

- 最大输出功率

- +20 dBm

- 低活动功耗

- 14 mA RX

- 超低电流断电模式

- 30 nA 关机, 40 nA 待机

- 数据传输率 = 100 bps 到 500 kbps

- 前导探测模式

- 快速唤醒和跳数

- 电源 = 1.8 至 3.8 V

- 出色的选择性能

- 58 dB 相邻通道

- 1 MHz 处阻断增益为 75 dB

- 天线分集和 T/R 开关控制

- 高度可配置的分组处理程序

- TX和RX64字节FIFO

- 自动频率控制 (AFC)

- 自动增益控制 (AGC)

- 低 BOM

- 低电量探测器

- 温度传感器

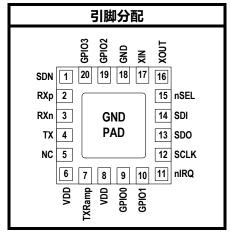

- 20 引脚 QFN 封装

- IEEE 802.15.4g 就绪

- 6 在 1.2kbps 时 mA 平均 Rx 电流 适合中国调控(国家电网)

■ 中国智能仪表

### 说明

Silicon Laboratories 的 Si4438 为高性能的低电流收发器, 可覆盖从 425 至 525 MHz 的次千兆赫频段。Si4438 针对中国智能仪表市场,特别 适合于智能电表。该设备的覆盖区及引脚与 Si446x 无线电兼容,可为全 世界的次千兆赫应用提供行业领先的性能。无线电设备是 EZRadioPRO® 产品系列的一部分,包括全套发射器、接收器和收发器的产品线,涵盖各 种应用。所有零件都具有杰出的灵敏度 —124 dBm , 可同时实现极低的有 效电流和待机电流消耗。12.5kHz 通道 58dB 相邻通道选择性的间距确保 了严苛 RF 条件下的可靠接收操作。Si4438 可提供超常的高达 +20 dBm 具有显著 TX 效率的输出功率。高输出功率和灵敏度实现了业界领先的 144 dB 链路预算,实现了范围扩展和高度可靠的通信链路。

专利申请中

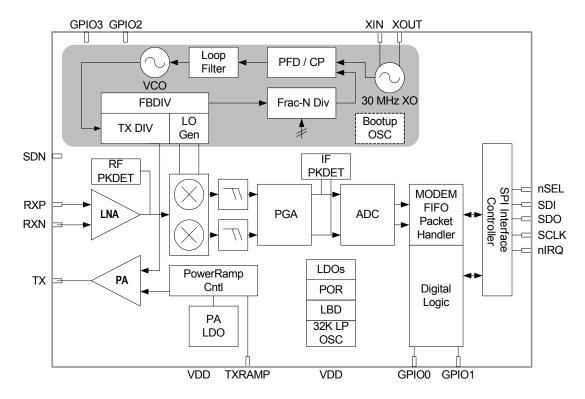

# 功能框图

| Product | Freq. Range | Max Output<br>Power | TX Current | RX Current |

|---------|-------------|---------------------|------------|------------|

| Si4438  | 425–525 MHz | +20 dBm             | 75 mA      | 13.7 mA    |

# 目录

| 章  | <u>5节</u>               | <u>页码</u> |

|----|-------------------------|-----------|

| 1. | 电气规格                    | 4         |

|    | 功能描述                    |           |

|    | 控制器接口                   |           |

| •  | 3.1. 串行外围接口 (SPI)       |           |

|    | 3.2. 快速响应寄存器            |           |

|    | 3.3. 工作模式和计时            |           |

|    | 3.4. 应用程序编程接口           |           |

|    | 3.5. 中断                 |           |

|    | 3.6. GPIO               |           |

| 4. | 调制和硬件配置选项               |           |

|    | 4.1. 调制类型               |           |

|    | 4.2. 硬件配置选项             |           |

|    | 4.3. 前导长度               |           |

| 5. | 内部功能块                   |           |

| -  | 5.1. RX 链               |           |

|    | 5.2. RX 调制解调器           |           |

|    | 5.3. 合成器                |           |

|    | 5.4. 发送器(TX)            |           |

|    | 5.5. 晶体振荡器              |           |

| 6. | 数据处理和分组处理程序             |           |

|    | 6.1. RX 和 TX FIFO       | 31        |

|    | 6.2. 分组处理程序             | 32        |

| 7. | . RX 调制解调器配置            | 33        |

| 8. | 辅助块                     |           |

|    | 8.1. 唤醒定时器和 32 kHz 时钟源  | 33        |

|    | 8.2. 低占空比模式 (自动 RX 唤醒 ) |           |

|    | 8.3. 温度、电池电压和辅助 ADC     |           |

|    | 8.4. 低电量探测器             |           |

|    | 8.5. 天线分集               |           |

|    | 8.6. 前导探测模式             |           |

|    | . 引脚描述:Si4438-C         |           |

|    | D. 订购信息                 |           |

|    | 1. 封装外形:Si4438          |           |

|    | 2. PCB 焊盘图案:Si4438      |           |

| 13 | 3. 顶部标记                 | 43        |

|    | 13.1. Si4438 顶部标记       | 43        |

|    | 13.2. 顶部标记说明            |           |

| 田土 | 玄信自                     | 11        |

# 1. 电气规格

Table 1. DC Characteristics\*

| Parameter                      | Symbol                   | Test Condition                                                                    | Min | Тур  | Max | Unit |

|--------------------------------|--------------------------|-----------------------------------------------------------------------------------|-----|------|-----|------|

| Supply Voltage<br>Range        | V <sub>DD</sub>          |                                                                                   | 1.8 | 3.3  | 3.8 | V    |

| Power Saving Modes             | I <sub>Shutdown</sub>    | RC Oscillator, Main Digital Regulator, and Low Power Digital Regulator OFF        |     | 30   | _   | nA   |

|                                | I <sub>Standby</sub>     | Register values maintained and RC oscillator/WUT OFF                              |     | 40   | _   | nA   |

|                                | I <sub>SleepRC</sub>     | RC Oscillator/WUT ON and all register values maintained, and all other blocks OFF |     | 740  | _   | nA   |

|                                | I <sub>SleepXO</sub>     | Sleep current using an external 32 kHz crystal.                                   | _   | 1.7  | _   | μΑ   |

|                                | I <sub>Sensor -LBD</sub> | Low battery detector ON, register values maintained, and all other blocks OFF     | _   | 1    |     | μΑ   |

|                                | I <sub>Ready</sub>       | Crystal Oscillator and Main Digital Regulator ON, all other blocks OFF            |     | 1.8  | _   | mA   |

| Preamble Sense<br>Mode Current | I <sub>psm</sub>         | Duty cycling during preamble search,<br>1.2 kbps, 4 byte preamble                 |     | 6    |     | mA   |

|                                | I <sub>psm</sub>         | Fixed 1 s wakeup interval, 50 kbps, 5 byte preamble                               |     | 10   |     | μΑ   |

| TUNE Mode Current              | I <sub>Tune_RX</sub>     | RX Tune                                                                           | _   | 7.6  |     | mA   |

|                                | I <sub>Tune_TX</sub>     | TX Tune                                                                           |     | 7.8  | _   | mA   |

| RX Mode Current                | I <sub>RXH</sub>         |                                                                                   | _   | 13.7 |     | mA   |

| TX Mode Current<br>(Si4438)    | I <sub>TX_+20</sub>      | +20 dBm output power, class-E match, 490 MHz, 3.3 V                               | _   | 75   | —   | mA   |

\*Note: All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

Table 2. Synthesizer AC Electrical Characteristics<sup>1</sup>

| Parameter                                        | Symbol               | Test Condition                                                                                  | Min | Тур  | Max | Unit   |

|--------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------|-----|------|-----|--------|

| Synthesizer Frequency<br>Range (Si4438)          | F <sub>SYN</sub>     |                                                                                                 | 425 | _    | 525 | MHz    |

| Synthesizer Frequency<br>Resolution <sup>2</sup> | F <sub>RES-525</sub> | 425–525 MHz                                                                                     |     | 14.3 | _   | Hz     |

| Synthesizer Settling Time                        | t <sub>LOCK</sub>    | Measured from exiting Ready mode with XOSC running to any frequency. Including VCO Calibration. |     | 50   |     | μs     |

| Phase Noise                                      | L $\phi(f_M)$        | ΔF = 10 kHz, 460 MHz                                                                            | _   | -109 | _   | dBc/Hz |

|                                                  |                      | ΔF = 100 kHz, 460 MHz                                                                           | _   | -111 | _   | dBc/Hz |

|                                                  |                      | ΔF = 1 MHz, 460 MHz                                                                             | _   | -131 | _   | dBc/Hz |

|                                                  |                      | ΔF = 10 MHz, 460 MHz                                                                            | _   | -141 | _   | dBc/Hz |

<sup>1.</sup> All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

**<sup>2.</sup>** Default API setting for modulation deviation resolution is double the typical value specified.

Table 3. Receiver AC Electrical Characteristics<sup>1</sup>

| Parameter                                         | Symbol              | Test Condition                                                                                                                                                                                                                                          | Min | Тур        | Max | Unit |

|---------------------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|------|

| RX Frequency<br>Range (Si4438)                    | F <sub>RX</sub>     |                                                                                                                                                                                                                                                         | 425 | _          | 525 | MHz  |

| RX Sensitivity <sup>2</sup>                       | P <sub>RX_0.5</sub> | (BER < 0.1%)<br>(500 bps, GFSK, BT = 0.5,<br>$\Delta f = \pm 250 \text{Hz})^2$                                                                                                                                                                          | _   | -124       | _   | dBm  |

|                                                   | P <sub>RX_40</sub>  | (BER < 0.1%)<br>(40 kbps, GFSK, BT = 0.5,<br>$\Delta f = \pm 20 \text{ kHz})^2$                                                                                                                                                                         | _   | -108       | _   | dBm  |

|                                                   | P <sub>RX_100</sub> | (BER < 0.1%)<br>(100 kbps, GFSK, BT = 0.5,<br>$\Delta f = \pm 50 \text{ kHz})^1$                                                                                                                                                                        | _   | -104       | _   | dBm  |

|                                                   | P <sub>RX_9.6</sub> | (BER < 0.1%)<br>(9.6 kbps, GFSK, BT = 0.5,<br>$\Delta f = \pm 4.8 \text{ kHz})^2$                                                                                                                                                                       |     | -114       |     | dBm  |

|                                                   | P <sub>RX_OOK</sub> | (BER < 0.1%, 4.8 kbps, 350 kHz BW, OOK, PN15 data) <sup>2</sup>                                                                                                                                                                                         | _   | -108       | _   | dBm  |

|                                                   |                     | (BER < 0.1%, 40 kbps, 350 kHz BW,<br>OOK, PN15 data) <sup>2</sup>                                                                                                                                                                                       | _   | -102       | _   | dBm  |

|                                                   |                     | (BER < 0.1%, 120 kbps, 350 kHz BW, OOK, PN15 data) <sup>2</sup>                                                                                                                                                                                         | _   | -98        | _   | dBm  |

| RX Channel Bandwidth                              | BW                  |                                                                                                                                                                                                                                                         | 1.1 | _          | 850 | kHz  |

| RSSI Resolution                                   | RES <sub>RSSI</sub> |                                                                                                                                                                                                                                                         | _   | ±0.5       |     | dB   |

| ±1-Ch Offset Selectivity,<br>450 MHz <sup>2</sup> | C/I <sub>1-CH</sub> | Desired Ref Signal 3 dB above sensitivity, BER < 0.1%. Interferer is CW, and desired is modulated with 2.4 kbps $\Delta F = 1.2 \text{ kHz GFSK with BT} = 0.5, RX $ $\text{channel BW} = 4.8 \text{ kHz},$ $\text{channel spacing} = 12.5 \text{ kHz}$ | _   | -60        | _   | dB   |

| Blocking 1 MHz Offset <sup>2</sup>                | 1M <sub>BLOCK</sub> | Desired Ref Signal 3 dB above                                                                                                                                                                                                                           | _   | <b>–77</b> | _   | dB   |

| Blocking 8 MHz Offset <sup>2</sup>                | 8M <sub>BLOCK</sub> | sensitivity, BER = 0.1%. Interferer is CW, and desired is modulated with 2.4 kbps, ΔF = 1.2 kHz GFSK with BT = 0.5, RX channel BW = 4.8 kHz                                                                                                             | _   | -84        | _   | dB   |

| Image Rejection                                   | Im <sub>REJ</sub>   | Rejection at the image frequency.  IF = 468 kHz                                                                                                                                                                                                         | _   | 40         | _   | dB   |

6

- 1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

- 2. Measured over 50000 bits using PN9 data sequence and data and clock on GPIOs. Sensitivity is expected to be better if reading data from packet handler FIFO especially at higher data rates.

Table 4. Transmitter AC Electrical Characteristics<sup>1</sup>

| Parameter                                       | Symbol                | Test Condition                                                              | Min | Тур  | Max | Unit |

|-------------------------------------------------|-----------------------|-----------------------------------------------------------------------------|-----|------|-----|------|

| TX Frequency<br>Range                           | F <sub>TX</sub>       |                                                                             | 425 | _    | 525 | MHz  |

| (G)FSK Data Rate <sup>2</sup>                   | DR <sub>FSK</sub>     |                                                                             | 0.1 |      | 500 | kbps |

| OOK Data Rate <sup>2</sup>                      | DR <sub>OOK</sub>     |                                                                             | 0.1 |      | 120 | kbps |

| Modulation Deviation<br>Range                   | Δf <sub>525</sub>     | 425–525 MHz                                                                 | _   | 750  | _   | kHz  |

| Modulation Deviation<br>Resolution <sup>3</sup> | F <sub>RES-525</sub>  | 425–525 MHz                                                                 |     | 14.3 | _   | Hz   |

| Output Power Range <sup>4</sup>                 | P <sub>TX</sub>       | Typical range at 3.3 V with class E match optimized for best PA efficiency. | -20 | _    | +20 | dBm  |

| TX RF Output Steps                              | ΔP <sub>RF_OUT</sub>  | Using Class E match within 6 dB of max power                                | _   | 0.25 | _   | dB   |

| TX RF Output Level<br>Variation vs. Temperature | ΔP <sub>RF_TEMP</sub> | –40 to +85 °C                                                               | _   | 2.3  | _   | dB   |

| TX RF Output Level<br>Variation vs. Frequency   | ΔP <sub>RF_FREQ</sub> |                                                                             | _   | 0.6  | _   | dB   |

| Transmit Modulation Filtering                   | B*T                   | Gaussian Filtering Bandwith Time<br>Product                                 | _   | 0.5  | _   |      |

- 1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

- 2. The maximum data rate is dependent on the XTAL frequency and is calculated as per the formula: Maximum Symbol Rate = Fxtal/60, where Fxtal is the XTAL frequency (typically 30 MHz).

- 3. Default API setting for modulation deviation resolution is double the typical value specified.

- 4. Output power is dependent on matching components and board layout.

Table 5. Auxiliary Block Specifications<sup>1</sup>

| Parameter                                                    | Symbol                | Test Condition                                                                                                                                             | Min     | Тур  | Max   | Unit                |

|--------------------------------------------------------------|-----------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|---------------------|

| Temperature Sensor<br>Sensitivity                            | TS <sub>S</sub>       |                                                                                                                                                            | _       | 4.5  |       | ADC<br>Codes/<br>°C |

| Low Battery Detector<br>Resolution                           | LBD <sub>RES</sub>    |                                                                                                                                                            | _       | 50   | _     | mV                  |

| Microcontroller Clock<br>Output Frequency Range <sup>2</sup> | F <sub>MC</sub>       | Configurable to Fxtal or Fxtal divided by 2, 3, 7.5, 10, 15, or 30 where Fxtal is the reference XTAL frequency. In addition, 32.768 kHz is also supported. | 32.768K | _    | Fxtal | Hz                  |

| Temperature Sensor<br>Conversion                             | TEMP <sub>CT</sub>    | Programmable setting                                                                                                                                       | _       | 3    | _     | ms                  |

| XTAL Range <sup>3</sup>                                      | XTAL <sub>Range</sub> |                                                                                                                                                            | 25      | _    | 32    | MHz                 |

| 30 MHz XTAL Start-Up Time                                    | t <sub>30M</sub>      | Using XTAL and board layout in reference design. Start-up time will vary with XTAL type and board layout.                                                  | _       | 300  | _     | μs                  |

| 30 MHz XTAL Cap<br>Resolution                                | 30M <sub>RES</sub>    |                                                                                                                                                            | _       | 70   | _     | fF                  |

| 32 kHz XTAL Start-Up Time                                    | t <sub>32k</sub>      |                                                                                                                                                            | _       | 2    | _     | sec                 |

| 32 kHz Accuracy using<br>Internal RC Oscillator              | 32KRC <sub>RES</sub>  |                                                                                                                                                            | _       | 2500 | _     | ppm                 |

| POR Reset Time                                               | t <sub>POR</sub>      |                                                                                                                                                            | _       | _    | 6     | ms                  |

- 1. All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from –40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

- 2. Microcontroller clock frequency tested in production at 1 MHz, 30 MHz, 32 MHz, and 32.768 kHz. Other frequencies tested in bench characterization.

- 3. XTAL Range tested in production using an external clock source (similar to using a TCXO).

Table 6. Digital IO Specifications (GPIO\_x, SCLK, SDO, SDI, nSEL, nIRQ, SDN)<sup>1</sup>

| Parameter                            | Symbol              | Test Condition                                                                                | Min                   | Тур  | Max                   | Unit |

|--------------------------------------|---------------------|-----------------------------------------------------------------------------------------------|-----------------------|------|-----------------------|------|

| Rise Time <sup>2,3</sup>             | T <sub>RISE</sub>   | 0.1 x $V_{DD}$ to 0.9 x $V_{DD}$ ,<br>$C_L = 10 \text{ pF}$ ,<br>DRV<1:0> = LL                | _                     | 2.3  | _                     | ns   |

| Fall Time <sup>3,4</sup>             | T <sub>FALL</sub>   | $0.9 \times V_{DD}$ to $0.1 \times V_{DD}$ ,<br>$C_{L} = 10 \text{ pF}$ ,<br>DRV < 1:0 > = LL | _                     | 2    | _                     | ns   |

| Input Capacitance                    | C <sub>IN</sub>     |                                                                                               | _                     | 2    | _                     | pF   |

| Logic High Level Input Voltage       | V <sub>IH</sub>     |                                                                                               | V <sub>DD</sub> x 0.7 | _    | _                     | V    |

| Logic Low Level Input Voltage        | $V_{IL}$            |                                                                                               | _                     |      | V <sub>DD</sub> x 0.3 | V    |

| Input Current                        | I <sub>IN</sub>     | 0 <v<sub>IN&lt; V<sub>DD</sub></v<sub>                                                        | -1                    | _    | 1                     | μA   |

| Input Current If Pullup is Activated | I <sub>INP</sub>    | $V_{IL} = 0 V$                                                                                | 1                     |      | 4                     | μA   |

| Drive Strength for Output Low        | I <sub>OmaxLL</sub> | $DRV[1:0] = LL^3$                                                                             | _                     | 6.66 | _                     | mA   |

| Level                                | I <sub>OmaxLH</sub> | $DRV[1:0] = LH^3$                                                                             | _                     | 5.03 |                       | mA   |

|                                      | I <sub>OmaxHL</sub> | $DRV[1:0] = HL^3$                                                                             | _                     | 3.16 |                       | mA   |

|                                      | $I_{OmaxHH}$        | $DRV[1:0] = HH^3$                                                                             | _                     | 1.13 |                       | mA   |

| Drive Strength for Output High       | I <sub>OmaxLL</sub> | $DRV[1:0] = LL^3$                                                                             | _                     | 5.75 | _                     | mA   |

| Level                                | I <sub>OmaxLH</sub> | $DRV[1:0] = LH^3$                                                                             | _                     | 4.37 |                       | mA   |

|                                      | I <sub>OmaxHL</sub> | $DRV[1:0] = HL^3$                                                                             | _                     | 2.73 | _                     | mA   |

|                                      | $I_{OmaxHH}$        | $DRV[1:0] = HH^3$                                                                             | _                     | 0.96 | _                     | mA   |

| Drive Strength for Output High       | I <sub>OmaxLL</sub> | $DRV[1:0] = LL^3$                                                                             | _                     | 2.53 | _                     | mA   |

| Level for GPIO0                      | I <sub>OmaxLH</sub> | $DRV[1:0] = LH^3$                                                                             | _                     | 2.21 | _                     | mA   |

|                                      | I <sub>OmaxHL</sub> | $DRV[1:0] = HL^3$                                                                             | _                     | 1.7  | _                     | mA   |

|                                      | I <sub>OmaxHH</sub> | $DRV[1:0] = HH^3$                                                                             | _                     | 0.80 | _                     | mA   |

| Logic High Level Output Voltage      | $V_{OH}$            | DRV[1:0] = HL                                                                                 | V <sub>DD</sub> x 0.8 |      | _                     | V    |

| Logic Low Level Output Voltage       | $V_{OL}$            | DRV[1:0] = HL                                                                                 | _                     | _    | V <sub>DD</sub> x 0.2 | V    |

- All minimum and maximum values are guaranteed across the recommended operating conditions of supply voltage and from -40 to +85 °C unless otherwise stated. All typical values apply at VDD = 3.3 V and 25 °C unless otherwise stated.

- **2.** 6.7 ns is typical for GPIO0 rise time.

- 3. Assuming VDD = 3.3 V, drive strength is specified at Voh (min) = 2.64 V and Vol(max) = 0.66 V at room temperature.

- 4. 2.4 ns is typical for GPIO0 fall time.

**Table 7. Thermal Operating Characteristics**

| Parameter                                          | Value       | Unit |

|----------------------------------------------------|-------------|------|

| Operating Ambient Temperature Range T <sub>A</sub> | -40 to +85  | °C   |

| Thermal Impedance $\theta_{JA}$                    | 25          | °C/W |

| Junction Temperature T <sub>JMAX</sub>             | +105        | °C   |

| Storage Temperature Range T <sub>STG</sub>         | -55 to +150 | °C   |

Table 8. Absolute Maximum Ratings\*

| Parameter                                                  | Value                       | Unit |

|------------------------------------------------------------|-----------------------------|------|

| V <sub>DD</sub> to GND                                     | -0.3, +3.8                  | V    |

| Instantaneous V <sub>RF-peak</sub> to GND on TX Output Pin | -0.3, +8.0                  | V    |

| Sustained V <sub>RF-peak</sub> to GND on TX Output Pin     | -0.3, +6.5                  | V    |

| Voltage on Digital Control Inputs                          | -0.3, V <sub>DD</sub> + 0.3 | V    |

| Voltage on Analog Inputs                                   | -0.3, V <sub>DD</sub> + 0.3 | V    |

| Voltage on XIN Input when using a TCXO                     | -0.7, V <sub>DD</sub> + 0.3 | V    |

| RX Input Power                                             | +10                         | dBm  |

\*Note: Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only and functional operation of the device at or beyond these ratings in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Power Amplifier may be damaged if switched on without proper load or termination connected. TX matching network design will influence TX V<sub>RF-peak</sub> on TX output pin. Caution: ESD sensitive device.

# 2. 功能描述

Si4438 设备为高性能低电流的无线 ISM 收发器,可覆盖次干兆赫波段。 $1.8-3.8\,V$  的宽工作电压范围和低电流消耗使 Si4438 成为电池供电应用的理想之选。Si4438 工作时为时分双工收发器 (TDD),可交替发射和接收数据包。该设备采用单向转换混频器实现 2 级 FSK/GFSK 或 OOK 调制的接收信号改变为较低的 IF 频率。跟随一可编程增益放大器 (PGA),信号通过高性能的  $\Delta\Sigma$  ADC 被转换为数字域,实现了在内置 DSP 中的滤波、反调制、消波及数据包处理,相对于基于模拟的框架,增强了接收器的性能和灵活度。通过可编程的 GPIO 或通过解读 64 字节 RX FIFO 的标准 SPI 总线,已调制的信号可被输出到 MCU 系统。

由于发射器和接收器不能同时工作,因此单个的高精度本机振荡器 (LO) 同时用于发射和接收模式。LO 由集成 VCO 和  $\Delta\Sigma$  Fractional-N PLL 合成器制成。合成器用来支持可配置的从 100 bps 到 500 kbps 的数据传输率。传输的 FSK 数据被直接调制进入 $\Delta\Sigma$ 数据流并可被高斯低通滤波器塑造以降低多余的频谱含量。

Si4438 包含一功率放大器 (PA),可在极高的效率下支持输出功率高达 +20 dBm,仅消耗 75 mA 的电流。集成的 +20 dBm 功率放大器也可被用于补偿成本较低性能较低天线或由于小体积受尺寸限制的天线的性能损耗。有竞争力 的其他解决方案需要较大较昂贵的外功率放大器以达到可比性能。单端的功率放大器实现了易于天线搭配及低原材料成本。功率放大器包含自动倾斜上升和倾斜下降控制以减少多余的频谱扩展。Si4438 产品系列支持 TX/RX 开关控制和天线分集开关控制以扩展链路范围和提高性能。内置天线分集可用于进一步扩展范围和提高性能。天线分集完全集成到 Si4438 中并可使系统链路预算提高 8-10 dB,从而实现在不利的环境条件下大幅范围的增加。高度可配置的分组处理程序可实现几乎任何数据包结构的自主编码和解码。诸如自动唤醒定时器、低电量探测器、64 字节 TX/RX FIFO,及前导检测等附加系统功能等,可减少整体电流消耗并可使用较低成本的系统 MCU。集成温度传感器、加电复位 (POR)及 GPIO 可进一步减少总体系统成本和尺寸。Si4438 可与 MCU、晶体和一些无源元件共同工作以创建成本极低的系统。

# 3. 控制器接口

# 3.1. 串行外围接口 (SPI)

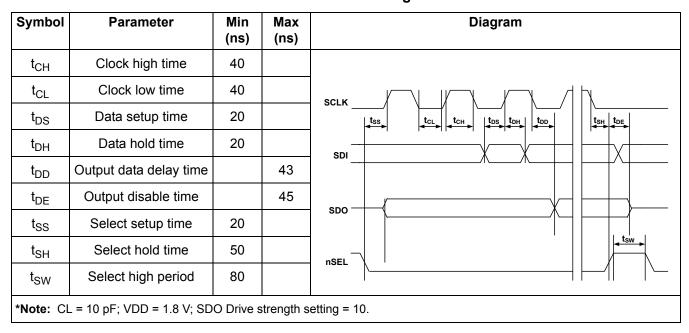

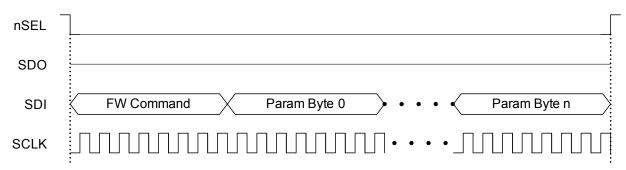

Si4438 通过一标准 4 线外围接口 (SPI) 与主机 MCU 进行通讯。SCLK、SDI、SDO 和 nSEL。SPI 接口可在最大 10 MHz 下工作运行。SPI 定时参数在 表 9 中有所说明。主机 MCU 通过 SDI 引脚写入数据并可从 SDO 输出引脚上的设备读取数据。图 1 展示了 SPI 书写命令。nSEL 引脚应降低以启动 SPI 命令。SDI 数据的第一个字节会成为后面紧接 n 个参数数据的字节固件命令其中之一,这些参数数据字节会根据具体命令进行变化。SCLK 的上升沿应与 SDI 数据的中心对齐。

**Table 9. Serial Interface Timing Parameters**

Figure 1. SPI Write Command

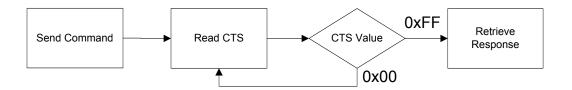

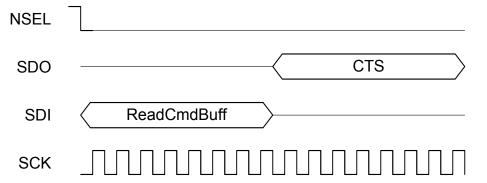

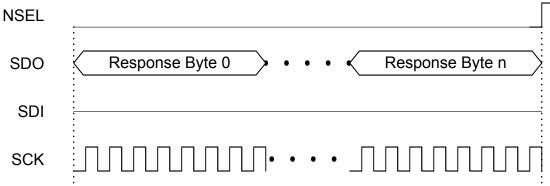

Si4438 包含一内部 MCU,可控制无线电的所有内部功能。对于 SPI 读取命令,一般的 MCU 检测清除发送流程用来确保内部 MCU 已执行命令,并已将数据准备好通过 SDO 引脚输出。图 2展示了 SPI 读取命令的一般流程。一旦 CTS 值显示 FFh 那么读出的数据就即将会时钟输出到主机 MCU。一个有效 FFh CTS 读数一般用时为 20 µs。图 3 展示了在 CTS 被设置为 FFh 后的读取周期。内部 MCU 会在下降沿时钟输出 SDO 数据以便主机 MCU 能够在 SCLK 的上升沿处理 SDO 数据。

# Firmware Flow

Figure 2. SPI Read Command—Check CTS Value

Figure 3. SPI Read Command—Clock Out Read Data

## 3.2. 快速响应寄存器

快速响应寄存器是无需监控和检测 CTS 就可立即被读取的寄存器。 有四个快速响应寄存器可被编程为具有特定的功能。快速响应寄存器可通过 API 命令被读取,0x50 代表快速响应 A,0x51 代表快速响应 B,0x53 代表快速响应 C,0x57 代表快速响应 D。快速响应寄存器可通过"FRR\_CTL\_X\_MODE"属性进行配置。

快速响应寄存器也可能以突发脉冲的方式被读取。在初始的 16 个时钟循环后,每增加的 8 个时钟循环将会以循环的方式时钟输出下一个快速响应寄存器的内容。只有 NSEL 被触发后 FRR 值才会被更新。

# 3.3. 工作模式和计时

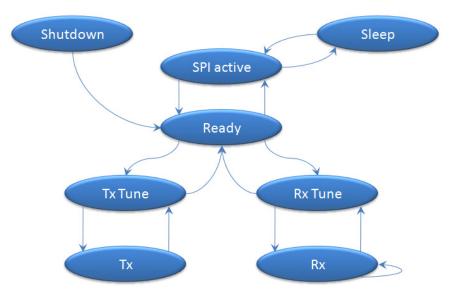

Si4438 的初始状态在 图 4 中显示。关机状态会彻底关闭无线电以最小化电流消耗。对于某一特定的应用,可启用待机/睡眠、SPI 活动、准备、TX 调谐和 RX 调谐以最优化电流消耗和 RX/TX 的响应时间。API 命令 START\_RX、START\_TX 和 CHANGE\_STATE ,除关机由 SDN 引脚 1 控制外,控制所有工作状态。表 10说明了每种工作模式及达到 RX 或 TX 模式所需的时间和每种模式下的电流消耗。表 9 里的次数是从 nSEL 的上升沿开始直至芯片到达期望状态时间内测量得到的。注意这些次数表明的是状态转换计时但并不受保证,因此只能作为参考数据点。自动测序仪会使芯片从其他任何状态进入 RX 或 TX 状态。无必要手动单步调试所有状态。为简化图表,虽无显示但在RX 或 TX 后可自动恢复到任何低电量状态。

Figure 4. State Machine Diagram

| State/Mode       | Respons | Current in State |                 |

|------------------|---------|------------------|-----------------|

| State/Mode       | TX      | RX               | /Mode           |

| Shutdown State   | 15 ms   | 15 ms            | 30 nA           |

| Standby State    | 504 μs  | 516 µs           | 40 nA           |

| Sleep State      | 504 µs  | 516 µs           | 740 nA          |

| SPI Active State | 288 µs  | 296 µs           | 1.35 mA         |

| Ready State      | 108 µs  | 120 µs           | 1.8 mA          |

| TX Tune State    | 60 µs   | _                | 7.8 mA          |

| RX Tune State    | _       | 84 µs            | 7.6 mA          |

| TX State         | _       | 132 µs           | 75 mA @ +20 dBm |

| RX State         | 120 µs  | 75 µs            | 13.7 mA         |

**Table 10. Operating State Response Time and Current Consumption**

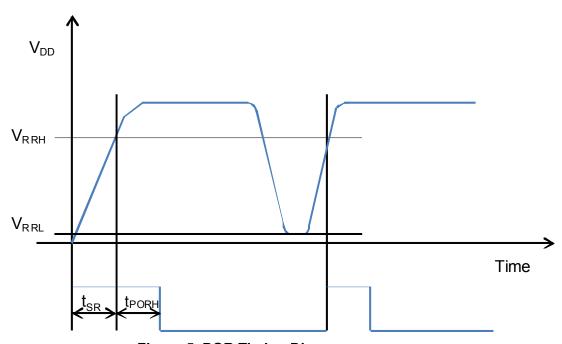

图 5 显示了 POR 计时和电压要求。功耗(电池寿命)取决于应用的占空比或该部件处于 Rx 或 Tx 的频率。在大多数应用中使用待机状态时对电池寿命是最有利的,但对于低占空比的应用来说关机会有优势。对最快的计时来说下一个状态可在 START\_RX 或 START\_TX API 命令中进行选择以最小化 SPI 事务和内部 MCU 处理。

## 3.3.1. 加电复位 (POR)

加电复位 (POR) 序列用于将设备从完全关闭或关机状态启动。为完成这一过程, VDD 必须在 1ms 内斜升并保持应用于设备至少 10ms。如果移除了 VDD,则在再次使用前须保持在 0.15V 下至少 10ms。详细信息请参阅 图 5 和表 11。

Figure 5. POR Timing Diagram

Table 11. POR Timing

| Variable          | Description                                   | Min     | Тур | Max | Units |

|-------------------|-----------------------------------------------|---------|-----|-----|-------|

| t <sub>PORH</sub> | High time for VDD to fully settle POR circuit | 10      |     |     | ms    |

| t <sub>PORL</sub> | Low time for VDD to enable POR                | 10      |     |     | ms    |

| $V_{RRH}$         | Voltage for successful POR                    | 90%*Vdd |     |     | V     |

| $V_{RRL}$         | Starting Voltage for successful POR           | 0       |     | 150 | mV    |

| t <sub>SR</sub>   | Slew rate of VDD for successful POR           |         |     | 1   | ms    |

#### 3.3.2. 关机状态

关机状态是设备电流消耗最低的状态,电流消耗标称为 30 nA。可通过驱动 SDN 引脚(引脚 1)至高处进入关机状态。除在关机状态下,其他状态时 SDN 引脚均应处于低处。在关机状态下,寄存器内容丢失并且无 SPI 接入。当解除关机状态时加电复位 (POR) 就会与内定标一起被启动。POR 后需要 POWER\_UP 命令来初始化无线电。SDN 引脚在再次降低之前需至少保持在高位 10 us 以便内部电容器能够放电。若 SDN 没有在高位保持满这段时间,则可能导致错失 POR 和设备不正确启动。如果不能满足 POR 时间和电压的要求,则强烈建议使用主机处理器控制 SDN,而不是将其系在板上的 GND 上。

#### 3.3.3. 待机状态

待机状态是除关机状态外电流消耗最低的状态,但对 RX 或 TX 有较快的响应时间。在大多数情况下待机状态应作为低功耗状态使用。在该状态下维持寄存器值,禁用其他所有块。在该模式下 SPI 是可接入的,但任何 SPI 事件包括 FIFO R/W,会启用内部启动振荡器并自动将该部件移至 SPI 活动状态。在 SPI 事件后主机会需要通过"改变状态"API 命令重新命令设备回到待机状态以达到 40 nA 的电流消耗。如果发生中断(如 nIRQ pin = 0)则中断寄存器必须被读取以达到该模式下的最低电流消耗。

#### 3.3.4. 睡眠状态

睡眠状态与待机状态相同,但是唤醒定时器和 32 kHz 的时钟源会被启用。32 kHz 的时钟源可以是内部定期校准的 32 kHz RC 振荡器,也可以是使用外部 XTAL 的 32 kHz 振荡器。在该模式下 SPI 是可接入的,但 SPI 时间会启用内部启动振荡器并自动将该部件移至 SPI 活动模式。在 SPI 事件后主机需再次命令设备进入睡眠。如果发生中断(如 nIRQ pin = 0)则中断寄存器必须被读取以达到该模式下的最低电流消耗。

#### 3.3.5. SPI 活动状态

在 SPI 活动状态下 SPI 和启动振荡器会被启用。在 SPI 事务之后在待机或睡眠期间设备将不会自动回到这些状态。 需要使用"改变状态"API 命令回到待机或睡眠模式。

#### 3.3.6. 就绪状态

就绪状态可在合适的电流消耗下提供较快转换到 TX 或 RX 状态的时间。在该模式下晶体振荡器保持启用状态,通过消除晶体启动时间减少了转换到 TX 或 RX 模式所需的时间。

#### 3.3.7. TX 状态

16

TX 状态可通过 "启动 TX" 或 "改变状态" API 命令从任何状态进入。内置定序器可控制所有从启用晶体振荡器到增强功率放大器在内的各状态间转换所需的命令。 当从待机状态转换为 TX 状态时以下序列的事件就会发生。

- 1. 启用内部 LDO。

- 2. 启动晶体振荡器并等待至就绪(由内部定时器控制)。

- 3. 启用 PLL。

- 4. 校准 VCO/PLL。

- 5. 等待至 PLL 达到要求的发射频段 (由内部定时器控制)。

- 6. 激活功率放大器并等待至功率增大完成(有内部定时器控制)。

- 7. 传输数据包。

根据在发送命令给 TX 之前芯片配置的状态,本序列中的步骤可省略。默认情况下,每次启用 PLL 时都会对 VCO 和 PLL 进行校准。当使用 START TX API 命令时,可定义下一状态以保证最佳计时和周转。

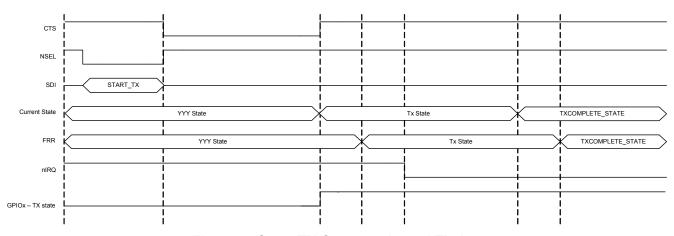

图 6 例举了一个 START\_TX 命令下的命令和计时的例子。一旦定序器使部件进入 TX 状态 CTS 就会走高。当定序器单步调试以上列出的事件,CTS 就会走低并将不会允许有新的命令或属性变化。如果快速响应 (FRR) 或 nIRQ 被用于监控电流状态,则会出现轻微的延迟,该延迟由从事件实际发生的时间到 FRR 或 nIRQ 上转换发生的时间的内部硬件引起。从进入 TX 状态到 FRR 更新的时间为 5 µs,到 nIRQ 转换的时间为 13 µs。如果为 TX 状态编程GPIO 或 GPIO 被作为传输/接收开关(TR 开关)控制,则不会出现延迟。

Figure 6. Start\_TX Commands and Timing

#### 3.3.8. RX 状态

RX 状态可通过"启动 RX"或"改变状态"API 命令从任何状态进入。内置定序器控制所有在各状态间转换所需的命令。当从待机状态转换到RX 状态时,以下序列的事件就会自动发生,使芯片进入RX 状态。

- 1. 启用数字 LDO 和模拟 LDO。

- 2. 启动晶体振荡器并等待至就绪(由内部定时器控制)。

- 3. 启用 PLL。

- 4. 校准 VCO

- 5. 等待至 PLL 达到要求的接收频率 (由内部定时器控制)。

- 6. 启用接收器电路:LNA、混频器、及ADC。

- 7. 启用数字调制解调器的接收模式。

基于无线电的配置,下面所有或部分功能通过数字调制解调器自动执行:AGC、AFC(可选择)、更新状态寄存器、位同步、分组处理(可选),包括同步字、报头检测及 CRC。与 TX 状态相同,RX 后的下一个状态可能会在"Start RX"API 命令中说明。START\_RX 命令和计时会和 图 6 中所示的计时相等。

## 3.4. 应用程序编程接口

主机 MCU 与设备内嵌应用程序编程接口 (API) 进行通信。API 分两个部分,命令和属性。命令用于控制芯片和检索其状态。属性是很少发生改变的一般配置。如需了解 API 详细信息,请参阅 www.silabs.com 上的 EZRadioPRO API Documentation.zip 文件。

## 3.5. 中断

当特定事件发生时 Si4438 可发出中断信号。芯片通过将 nIRQ 输出引脚设为 LOW = 0 通知微控制器中断事件已发生。 当任一(或多个)中断事件(与中断状态位相对应)发生时中断信号就会发出。在微控制器清除所有中断之前 nIRQ 引脚会一直处于低位。检测到状态发生下次改变时 nIRQ 输出信号会复位。

中断源分为三组。分组处理程序、芯片状态、调制解调器。可在中断属性寄存器内启用/停用这些分组的独立中断。必须启用中断才能在 nIRQ 上引发事件。必须启用中断组和 API 文件内所描述的 API 属性中的独立中断。一旦中断事件发生,且 nIRQ 引脚处于低位,有两种方法读取并清除中断。所有中断都可在"GET\_INT\_STATUS" API 命令中进行读取和清除。在默认情况下所有中断一旦读取就会被清除。若只想以最快的方式读取特定中断,则独立中断组(分组处理程序、芯片状态、调制解调器)可通过"GET\_MODEM\_STATUS"、"GET\_PH\_STATUS"(分组处理程序)和"GET\_CHIP\_STATUS"API 命令进行读取和清除。如果特定中断被启用或停用,则特定功能的即时状态可被读取。在中断后状态结果会被提供并以与中断相同的命令被读取。无论启用中断与否,状态位会提供功能的当前状态。快速响应寄存器也可提供中断组的信息,但读取快速响应寄存器不会清除中断和使 nIRQ 引脚复位。

#### 3.6. **GPIO**

18

在应用中有四个一般用途的 IO 引脚可供使用。GPIO 通过地址 13h 中的 GPIO\_PIN\_CFG 命令进行配置。如需了解 GPIO 选项完整清单,请参阅 API 指南。GPIO 引脚 0 和 1 应用于如数据或时钟等的有效信号。与引脚 0 和 1 相比,GPIO 引脚 2 和 3 对合成器内产生杂散具有更高的敏感性。 GPIO 的驱动强度可通过 GPIO\_PIN\_CFG 命令中的 GEN\_CONFIG 参数进行调整。在默认情况下驱动强度设置为最小值。GPIO 的默认配置和 SDN 下的状态在下面 表 12 中有显示。关机时 IO 的状态也在下面 表 12 中有显示。如之前 表 6 中说明,与其他 GPIO 相比,GPIO 0 具有更低的驱动强度。

Table 12. GPIOs

| Pin   | SDN State             | POR Default |

|-------|-----------------------|-------------|

| GPIO0 | 0                     | POR         |

| GPIO1 | 0                     | CTS         |

| GPIO2 | 0                     | POR         |

| GPIO3 | 0                     | POR         |

| nIRQ  | resistive VDD pull-up | nIRQ        |

| SDO   | resistive VDD pull-up | SDO         |

| SDI   | High Z                | SDI         |

| SCLK  | High Z                | SCLK        |

| NSEL  | High Z                | NSEL        |

# 4. 调制和硬件配置选项

Si4438 支持三种不同的调制选项并可用于不同的配置中,以使设备适用于任何特定的应用或替代传统系统。调制和配置选项在属性 MODEM\_MOD\_TYPE 中进行设置。详情请参阅 www.silabs.com 上的 EZRadioPRO API Documentation.zip 文件。

## 4.1. 调制类型

Si4438 支持五种不同的调制选项。高斯频移键控 (GFSK)、频移键控 (FSK)、开关键控 (OOK)。也可使用 GFSK 设置来构建最小频移键控 (MSK)。GFSK 为推荐使用的调制类型,因其可提供最佳性能和最洁净的调制频谱。通过 "MODEM\_MOD\_TYPE" API 属性中的 "MOD\_TYPE[2:0]" 寄存器设置调制类型。也可选择连续波 (CW) 载波以达到 RF 评估目的。也可选择调制源为伪随机源,以达到评估目的。

### 4.2. 硬件配置选项

有不同的接收调解器选项以最优化性能,并有 RX/TX 数据如何由主机 MCU 转移至 RF 设备的互斥选项。

#### 4.2.1. 接收解调器选项

设备中集成了多个解调器,以为不同应用、调制格式和数据包结构最优化性能。WDS 内置计算器会根据输入标准选择最佳的解调器。

#### 4.2.1.1. 同步解调器

同步解调器的内部频率误差估计器基于 101010 前导结构获取频率误差。位时钟恢复电路会在"10"或"01"比特流的四个事务处理内对输入的数据流进行锁定。同步解调器会对调制指数低于 2 的 2 级 FSK 或 GFSK 调制提供最佳性能。

#### 4.2.1.2. 异步解调器

异步解调器用于 OOK 调制和 FSK/GFSK,应满足以下一个或多个条件:

- 调制指数≥2

- 非标准前导码(非 1010101...模式)

当调制指数超过 2 时,异步解调器比同步解调器拥有更好的灵敏度。内部抗尖峰脉冲电路可提供无障碍数据输出和数据时钟信号以简化与主机的接口。无需在主机 MCU 中执行抗尖峰脉冲。对传统系统一般会使用异步解调器,异步解调器与传统设计中的设备相比具有很多性能优势。与用于非标准数据包结构的 Si4432/31 解决方案不同,无需对主机 MCU 中的数据执行抗尖峰脉冲。无障碍数据从 Si4438 设备输出,且可提供用于非同步数据的采样时钟给主机 MCU;因此主机 MCU 无需过采样或位时钟恢复。在异步解调器块中有多个检测器选项,会基于输入 WDS 计算器的选项选择检测器。异步解调器的内部频率误差估计器可根据任何前导结构获取频率误差。

#### 4.2.2. 与 MCU 的 RX/TX 数据接口

有两种不同的将数据从 RF 设备传输到主机 MCU 的选项。FIFO 模式使用 SPI 接口传输数据,而直接模式通过 GPIO 实时传输数据。

### 4.2.2.1. FIFO 模式

在 FIFO 模式中,传输和接收的数据储存在集成的 FIFO 寄存器存储器中。写命令 66h 并在其后直接紧跟主机想要写进 TXFIFO 的数据/时钟,以访问 TXFIFO。写命令 77h 并在其后紧跟主机想要从 RXFIFO 中读取的数据时钟周期数,以访问 RXFIFO。RX 数据会被时钟输出到 SDO 引脚上。

在 TX FIFO 模式中,储存在 FIFO 存储器中的数据字节会和其他字段和字节信息一同被"打包"以构建最终的传输数据包结构。这些其他潜在的字段包括前导码、同步字、和 CRC 校验和。在 TX 模式中,可通过启用或禁用单独的字段以高度定制数据包结构;例如,可通过禁用前导和同步字字段以将整个数据包结构导入 FIFO 存储器。如需了解更多特定应用或数据包大小的 FIFO 配置信息,请参阅"6. 数据处理和分组处理程序"页 31。在 RX 模式下,必须启用分组处理程序,方可使存储的已接收数据字节传输至 RX FIFO 存储器。分组处理程序需要检测同步字,需要恰当的同步字检测来确定有效荷载的开始。除 CRC 校验和(可选)可变数据包长度字节外,在同步字后的所有字节都会存储到 RX FIFO 存储器中。当在 RX 模式下使用 FIFO 时,可通过恰当编程 GPIO 引脚为 RXDATA 输出引脚仍可直接(实时)观察所有接收到的数据;这在应用开发中会非常有用。在 FIFO 模式下,当 PACKET\_SENT或 PACKET\_RX 中断发生时芯片会自动退出 TX 或 RX 状态。芯片会回到在"START TX"参数或"START RX"API命令、TXCOMPLETE\_STATE[3:0]或 RXVALID\_STATE[3:0]中编程的状态。例如,在 TX 数据包后,通过发送"START TX"命令和将 30h 写进 TXCOMPLETE\_STATE[3:0]参数中,芯片可处于就绪模式。芯片会传输FIFO 的所有内容,并且 PACKET\_SENT 中断会发生。当这样的情况发生时,芯片会按TXCOMPLETE STATE[3:0] = 30h 的规定回到就绪状态。

### 4.2.2.2. FIFO 直接模式 ( 无限接收 )

在一些应用中,有必要借助来源于芯片上的分组处理程序上前导和同步字检测接收极长的数据包(大于 40 kB)。在这些情况下,数据包长度未知,设备会将同步字后的字节永久导入 FIFO。其他特点,如数据白化、CRC、曼彻斯特码等在本模式下是支持的,但不支持 CRC 计算,因为数据包终端对于设备是未知的。RX 数据和时钟在 GPIO引脚上也是可用的。主机 MCU 需要通过发出 START RX 来开始搜索新的数据包以重置分组处理程序。

#### 4.2.2.3. 直接模式

对于在主机 MCU 内或其他基带芯片内执行数据包处理的传统系统,不适合使用 FIFO。对于这种情况,提供可完全绕过 FIFO 的直接模式。在 TX 直接模式下, TX 调制数据被应用于芯片的输入引脚并进行"实时"处理(即,不会存储在寄存器中稍后发送)。任何 GPIO 可被配置成 TX 数据输入功能来使用。而且,如果需要 GFSK 调制,则 TX 时钟输出功能需要一个额外的引脚(FSK 只需要 TX 数据输入引脚)。为达到直接模式,GPIO 必须在"GPIO\_PIN\_CFG"API 命令和"MODEM\_MOD\_TYPE"API 属性中进行配置。对于 GFSK,"TX\_DIRECT\_MODE\_TYPE"必须设置到同步。对于 2FSK 或 OOK,类型可设置为异步或同步。对于所有的直接模式配置,MOD\_SOURCE[1:0] 应设置为01h。在 RX 直接模式下,RX 数据和 RX 时钟可被编程以实现直接(实时)输出到 GPIO 引脚。然后微控制器可以在不使用 FIFO 或 RFIC 分组处理程序功能的情况下处理 RX 数据。

# 4.3. 前导长度

## 4.3.1. 数字信号到达检测器

传统前导检测需 20 个字节以检测前导。该设备引进了一种检测信号的新方法,可在一个字节内检测到前导模式。如果启用 AFC,则两个字节长度的前导足够可靠地检测信号到达和确定一次性的 AFC。因其减少了接收器检测前导所需的活动时间,所以其影响对低功率解决方案很重要。该特点与前导码检测模式(详见 "8.6. 前导探测模式" 页35)、最新的 WMBus N 模式及诸如跳频等特点一起使用,可使用信号到达作为跳频条件。也可使用传统前导检测器维持反向兼容性。注意 DSA 使用的是 RSSI 转移检测器。当用于碰撞检测时,RSSI 转移检测器需要在前导检测后进行重新配置。欲了解更多如何使用信号到达检测器对设备进行配置的详细信息,请参阅 API 文件。

#### 4.3.2. 传统前导检测

在继续接收数据包剩余部分(例如,同步字和有效荷载)之前,通过限定有效前导模式的接收可获得芯片的最佳性能。当接收到最小数量的连续位 101010... 模式时,前导接收才会视为有效;前导检测的要求阈值由PREAMBLE\_CONFIG\_STD\_1 中的 RX\_THRESH[6:0] 字段规定。检测阈值的适当值取决于系统应用并可在一般情况下权衡错误检测的可能性下的获取速度。如果检测阈值设的太低,芯片会容易检测到噪声内的较短模式;然后芯片会继续尝试检测不存在的数据包的剩余部分,导致错过实际的有效数据包的到达。如果检测阈值设的太高,传输的前导码位数要求数量必须相应地增加,导致更长的数据包长度和更短的电池寿命。20 位的前导检测阈值适用于绝大多数应用。传输的前导字段总长度必须至少与接收的前导检测阈值相等,加上额外的位数以获得位计时和 AFC演算的结算。推荐的多种操作模式下的前导检测阈值和前导长度已在 表 13 中列出。只有对于标准前导模式(例如,101010... 模式)的接收,才需在 RX\_THRESH[6:0] 字段中配置前导检测阈值。芯片也可支持重复性但非标准的前导模式的接收,通过 PREAMBLE CONFIG NSTD 和 PREAMBLE PATTERN 属性进行配置。

**Table 13. Recommended Preamble Length**

| Mode   | AFC      | Antenna<br>Diversity | Preamble Type | Recommended<br>Preamble Length | Recommended Preamble<br>Detection Threshold |

|--------|----------|----------------------|---------------|--------------------------------|---------------------------------------------|

| (G)FSK | Disabled | Disabled             | Standard      | 4 Bytes                        | 20 bits                                     |

| (G)FSK | Enabled  | Disabled             | Standard      | 5 Bytes                        | 20 bits                                     |

| (G)FSK | Disabled | Disabled             | Non-standard  | 2 Bytes                        | 0 bits                                      |

| (G)FSK | Enabled  |                      | Non-standard  | Not                            | Supported                                   |

| (G)FSK | Disabled | Enabled              | Standard      | 7 Bytes                        | 24 bits                                     |

| (G)FSK | Enabled  | Enabled              | Standard      | 8 Bytes                        | 24 bits                                     |

| OOK    | Disabled | Disabled             | Standard      | 4 Bytes                        | 20 bits                                     |

| OOK    | Disabled | Disabled             | Non-standard  | 2 Bytes                        | 0 bits                                      |

| OOK    | Enabled  |                      |               | Not                            | Supported                                   |

- **1.** The recommended preamble length and preamble detection thresholds listed above are to achieve 0% PER. They may be shortened when occasional packet errors are tolerable.

- 2. All recommended preamble lengths and detection thresholds include AGC and BCR settling times.

- 3. "Standard" preamble type should be set for an alternating data sequence at the max data rate (...10101010...)

- **4.** "Non-standard" preamble type can be set for any preamble type including ...10101010...

- **5.** When preamble detection threshold = 0, sync word needs to be 3 Bytes to avoid false syncs. When only a 2 Byte sync word is available the sync word detection can be extended by including the last preamble Byte into the RX sync word setting.

# 5. 内部功能块

以下部分提供了对关键内部块和特点的综述。

### 5.1. RX 链

内部低噪声放大器 (LNA) 用作一个宽频带 LNA,可与三个外部离散元件匹配,以覆盖次干兆赫段的任何普通范围的频率。LNA 具有极低的噪声以抑制以下阶段的噪声并达到最佳灵敏度;因此,无需外部增益或前端模块。LNA 具有增益控制,通过内部自动增益控制 (AGC) 演算进行控制。LNA 后紧随 I-Q 混频器、滤波器、可编程增益放大器 (PGA) 和 ADC。I-Q 混频器可把信号频率改变为中频。PGA 增大增益使其处于 ADC 的动态范围内。ADC 拒绝频带外的阻断物并可将信号转换到数字域,进行滤波、解调和处理。峰值检测器在 LNA 和 PGA 输出时进行集成以在 AGC 演算中使用。

## 5.2. RX 调制解调器

使用高性能 ADC 可实现数字域内的通道过滤、镜像抑制和解调,实现在特定应用中最优化设备的灵活性。数字调制解调器具有以下功能:

- 诵道选择滤波器

- TX 调制

- RX 解调

- 自动增益控制 (AGC)

- 前导检测

- 无效前导检测

- 无线电信号强度指示器 (RSSI)

- 自动频率补偿 (AFC)

- 循环冗余校验 (CRC)

数字通道滤波器和解调器已进行最优化以实现超低功率消耗和高度可配置性。支持的调制类型有 GFSK、FSK、GMSK 和 OOK。通道滤波器可被配置为支持 850 到低至 1.1 kHz 的频宽。支持从 100 bps 到高至 500 kbps 的多种数据传输率。可配置的前导检测器可与同步解调器一同使用以提高同步字检测的可靠性。可只使用同步检测跳过前导检测,这是当协议里使用长度很短的前导码如 Mbus 时异步解调器的一个很宝贵的特点。接收信号强度指示器(RSSI)可检测调谐通道上接收到信号的强度。RSSI 的分辨率为 0.5 dB。该高分辨率 RSSI 可实现精确通道功率检测以达到空闲通道评估(CCA)、载波检测(CS)、和读取之前先查询监听(LBT)功能。对包括 Silicon Labs 的 EZMAC 的主要特征在内的综合可编程分组处理程序进行了集成,以构建多种从对等网到网状网的通信拓扑结构。数据包报头的广泛可编程性实现了高级包过滤,反过来又可实现广播、群组、和点对点通信的混合。噪音和干扰可破坏无线通信信道,因此了解接收到的数据是否有误差是很重要的。循环冗余校验(CRC)用于检测每个数据包内是否存在错误位。在每个传输的数据包末端对 CRC 进行计算和追加,并由接收器确认无错误发生。分组处理程序和 CRC 可极大地减少系统微控制器上的负荷,使微控制器更为简单和成本更低。数字调制解调器包括 TX 调制器,可将 TX 数据位转换至相应的数字调制值流中,并与小数输入一同归入三角积分调制器。该调制方式会极大提高频率偏移的精确分辨率。使用高斯滤波器支持 GFSK,极大地减少了相邻信道的能量。

#### 5.2.1. 自动增益控制 (AGC)

使用为实现较快响应时间最优化的先进控制回路实现 AGC 的数字演算。AGC 可在单个位或少于 2 μs 内发生。 LNA 和 PGA 输出端的峰值检测器可实现 LNA 增益和 PGA 增益的最佳调整,以达到最优化 IM3、选择性和敏感度性能。

## 5.2.2. 自动频率校正(AFC)

因晶体非精确性引起的频率失谐可通过启用接收模式中的数字自动频率控制 (AFC)进行补偿。有两种类型的集成频率补偿:调制解调器频率补偿,和通过调整 PLL 频率的 AFC。AFC 禁用时,调制解调器补偿可对高达 IF 带宽的±0.25倍的频率偏置进行校正。当 AFC 启用时,接收到的信号会集中在 IF 滤波器的通带,通过较宽范围的高达 IF 带宽±0.35 倍的频率偏置提供最佳灵敏度和选择性。当 AFC 启用时,前导码长度需足够长以使 AFC 稳定。如 第22 页的表 13 中所示,一般需要多一个字节的前导码才可使 AFC 稳定。

#### 5.2.3. 接收信号强度指示器

接收信号强度指示器 (RSSI) 是对接收器调谐信道中信号强度的估量。RSSI 测量在信道滤波器之后完成,因此RSSI 仅是对期望的或非期望的带内信号功率的测量。有两种不同读取 RSSI 数值的方法和几种不同的方法来配置返回的 RSSI 数值。读取 RSSI 最快的方法是配置四个快速响应寄存器(FRR)其中之一,以返回锁存的 RSSI 数值。每个数据包对锁存的 RSSI 数值进行一次测量,在进入 RX 模式后在可配置的时间内对 RSSI 数值进行锁存。无需等待 CTS 即可在 16 个 SPI 时钟周期内读取快速响应寄存器。 也可通过 GET\_MODEM\_STATUS 命令读取 RSSI 数值。在该命令中,当前 RSSI 和锁存的 RSSI 都可获取。当前 RSSI 数值代表的是处理 GET\_MODEM\_STATUS 命令时的信号强度,因此每个数据包可被读取多次。与从快速响应寄存器中读取 RSSI 数值相比,在 GET\_MODEM\_STATUS 命令中读取 RSSI 数值要花更多时间。在执行初始命令之后,CTS 需要 33 µs 完成设置,然后需要四个或五个字节的 SPI 时钟周期读取当前的或锁存的 RSSI 数值。

RSSI 配置选项在 MODEM\_RSSI\_CONTROL API 属性中进行设置。基于以下事件对锁存的 RSSI 数值进行锁存和存储:在启动 RX 模式之后对前导检测、同步检测、或可配置数量的位时间进行测量(最少 4 个位时间)。四个位时间的要求是由通过调制解调器和数字信道滤波器的处理延迟和稳定过程决定的。在 MODEM\_RSSI\_CONTROL中,定义 RSSI 以对每个位周期进行更新,或对每四个位周期进行平均和更新。如果 RSSI 平均四位组被启用,那么在启动 RX 模式以实现平均法之后,锁存的 RSSI 数值会延迟至最少 7 位。当进入 RX 模式时锁存的 RSSI 数值就会被清除,因此在接收到数据包或回到待机模式后方可读取锁存的 RSSI 数值。如果在启动 RX 时 RSSI 数值已经被清除而没有被锁存,那么试图读取时数值会返回显示为 0。

API 读取的 RSSI 数值会通过下面的线性方程式转化为 dBm。

$$RF\_Input\_Level\_dBm = \left(\frac{RSSI\_value}{2}\right) - MODEM\_RSSI\_COMP - 70$$

MODEM\_RSSI\_COMP 属性可为实际 RF 输入位准(单位为 dBm)和返回的 RSSI 数值之间的关联提供微调整。即,该属性的调整可使用户上下移位 RSSI 对 RF 输入功率曲线。这适合用来补偿多种设计(例如,由于具有 SAW 预选滤波器、或 RF 开关)间的前端插入损耗差异。MODEM\_RSSI\_COMP = 0x40 = 64d 的数值适用于大多数应 田

也可使用空闲通道评估(CCA)或 RSSI 阈值检测。RSSI 阈值可在 MODEM\_RSSI\_THRESH API 属性中进行设置。如果当前 RSSI 数值在阈值之上,那么中断或 GPIO 就会通知主机。该阈值的锁存版本和异步版本可在任何 GPIO 上获得。基于 RSSI 的自动快速跳频可用。请参见 "5.3.1.2. 自动 RX 跳频和跳频表" 页 26。也可使用空闲通道评估(CCA)或 RSSI 阈值检测。RSSI 阈值可在 MODEM\_RSSI\_THRESH API 属性中进行设置。如果 RSSI 数值在阈值之上,那么中断或GPIO 就会通知主机。

该阈值的锁存版本和异步版本可在任何 GPIO 上获得。基于 RSSI 的自动快速跳频可用。请参见 "5.3.1.2. 自动 RX 跳频和跳频表"。

### 5.2.4. RSSI 转移指示器 (碰撞检测)

芯片可检测到任一方向的 RSSI 的转移(例如,信号增强或信号减弱)。转移检测的两个极性会同时启用,引起对上转移或下转移事件的检测。这可用于检测二次干扰信号(预期的或非预期的)是否已经和当前数据包的接收发生"碰撞"。可对中断标志或 GPIO 引脚进行配置以通知主机 MCU 发生了转移事件。可通过MODEM RSSI JUMP THRESH API 属性对引发转移事件所需的 RSSI 水平变化进行编程。

一旦检测到 RSSI 发生转移,可对芯片进行配置来重置 RX 状态,这样可即可自动开始数据包的重新获取。也可以 对芯片进行配置来产生中断。该功能是用于检测 RSSI 水平的突然变化而不是 RSSI 水平的缓慢渐变的。这是通过 在可编程的时间内对比 RSSI 水平的变化来实现的。芯片可通过这种方式有效评估 RSSI 水平变化的斜率。

预期数据包(例如,从接收噪音到接收有效信号的过渡)的到达很可能会被检测为 RSSI 转移事件。因为这个原因,建议在中间包中启用该功能(例如,在确认信号后,如 PREAMBLE VALID)。请参阅 API 文件了解配置选项。

## 5.3. 合成器

集成积分三角( $\Sigma\Delta$ )Fractional-N PLL 合成器可在 425–525 MHz 范围内工作。使用  $\Sigma\Delta$  合成器有很多优势;SD 合成器在选择数据传输率、偏差、信道频率、和信道间距时有较大的灵活性。发射调制通过小数分频器可直接应用于数字域的环路,实现非常高的精确度和对发射偏差的控制。425–525 MHz 频段内的频率分辨率是 14.3 Hz,在其他频段内的分辨率会更高。PLL 的标称参考频率是 30 MHz,但是也可以使用任何从 25 到 32 MHz 的 XTAL 频率。WDS 内的调制解调器配置计算器会自动说明正在使用的 XTAL 频率。PLL 使用的是带有集成片式电感器的差分 LC VCO。VCO 的输出端紧接着可配置的分频器,可以将信号分频降到需要的输出频率频段。

#### 5.3.1. 合成器频率控制

通过改变合成器的整数和小数设置来改变频率。WDS 计算器会自动提供这些设置,但为方便起见合成器的方程式在下面有所说明。设置频率的 API 有 FREQ\_CONTROL\_INTE、FREQ\_CONTROL\_FRAC2、FREQ\_CONTROL\_FRAC1、和 FREQ\_CONTROL\_FRAC0。

RF\_channel =

$$\left(\text{fc\_inte} + \frac{\text{fc\_frac}}{2^{19}}\right) \times \frac{2 \times \text{freq\_xo}}{8}(\text{Hz})$$

注意:上面公式中的 fc\_frac/2<sup>19</sup> 值必须是 1 和 2 之间的一个数字。

#### 5.3.1.1. EZ 频率编程

在使用多频率或多通道的应用中,每次需要改变频率时不建议写进四个 API 寄存器中。提供 EZ 频率编程,只需要单个寄存器写入(通道编号)来改变频率。首先通过编程合成器的整数和小数部分来首次设置基础频率。该基础频率对应通道 0。 下一步,通道步长被编程至 FREQ\_CONTROL\_CHANNEL\_STEP\_SIZE\_1 和 FREQ\_CONTROL\_CHANNEL\_STEP\_SIZE\_0 API 寄存器中。产生的频率将为:

START\_RX 或 START\_TX 的第二个自变量是通道,可以为 EZ 频率编程设置通道编号。例如,如果通道步长设为 1 MHz, INTE 和 FRAC API 寄存器的基础频率均设置为 490 MHz, 并在 START\_TX 命令中对编号为 5 的通道进行了编程,产生的频率为 495 MHz。如果通道自变量未作为 START\_RX/TX 命令的一部分写入,那么通道自变量会默认回到之前的数值。通道的初始值为 0;因此,如果没有写入通道值,那么会写入已编程好的基础频率。

#### 5.3.1.2. 自动 RX 跳频和跳频表

收发器支持自动跳频功能,可通过 API 进行完全配置。该功能为 RX 跳频而设计,设备必须在信道间进行跳频并寻找数据包。一旦设备进入 RX 状态,设备就会在功能启用的情况下开始自动在跳频表内跳频。

跳频表可容纳 64 条条目,并在固件内维持。每个条目都是一个通道编号;因此,跳频表可容纳 64 个通道。通过 RX HOP TABLE\_SIZE API 来设置表内的条目数量。

指定的通道和编程频率的 EZ 频率编程方法相一致。接收器从基极通道启动并按照从跳频表顶部跳到底部的顺序进行跳频。一旦到达跳频表的底部,跳频表就会折回到基极通道。跳频表的 OxFF 条目表明应跳过该条目。设备会跳频至下一个非 OxFF 条目。

有三个条件可用来判断设备是否继续跳频还是停留在某一特定通道。这些条件是:

- RSSI 阈值

- 前导码超时(无效前导模式)

- 同步字超时(前导码后无效同步字或未检测到同步字)

这些条件可以单独使用,或者也可通过配置 RX\_HOP\_CONTROL API 一起启用这些条件。但是,固件会通过满足的第一个条件来决定是否进行跳频。

监控的 RSSI 读数为当前的 RSSI 数值。该值与阈值相比较,如果高于阈值,那么该值会停留在通道上。如果 RSSI 读数低于阈值,那么 RSSI 会继续跳频。在通道间自动跳频时,不会对 RSSI 数值进行平均值计算。由于前导码超时和同步字超时功能需要数据包处理,因此如果用户处于未使用数据包处理功能的 "直接"或"原始"模式,则 RSSI 阈值是唯一可使用的条件。

注意 RSSI 阈值不是绝对的 RSSI 数值;相反,该阈值只是相对值,应该进行验证以确定特定应用的最佳阈值。

使用此方法在不同通道上从 RX 到 RX 的周转时间为 115 μs。接收模式所需花费的时间由跳频条件的配置来决定。 手动 RX 跳频具有最快的周转时间,但是需要更多主机 MCU 系统开销和管理。

#### 下面是使用自动跳频的示范步骤:

- 1. 设置基础频率 (inte + frac) 和通道步长。

- 2. 确定跳频表上的条目数量(RX\_HOP\_TABLE\_SIZE)。

- 3. 将通道写入跳频表(RX\_HOP\_TABLE\_ENTRY\_n)。

- 4. 对跳频条件进行配置并启用自动跳频-RSSI、前导码、或同步(RX\_HOP\_CONTROL)。

- 5. 启用后设置前导码和同步参数。

- 6. 使用 "MODEM\_RSSI\_THRESH"在调制解调器中编程 RSSI 阈值属性。

- 7. 使用 "PREAMBLE\_CONFIG\_STD\_1"设置前导阈值。

- 8. 使用 "PREAMBLE\_CONFIG\_STD\_2" 编程前导码超时属性。

- 9. 启用后设置同步检测参数。

- 10. 如果需要,使用"GPIO\_PIN\_CFG"对GPIO进行配置,以切换跳频和跳频表折回。

- 11. 使用 "START\_RX" API, 通道编号设置为跳频表的第一个有效条目(即,第一个非 0xFF 条目)。

- 12. 设备应该现在已处于自动跳频模式。

#### 5.3.1.3. 手动 RX 跳频

26

RX\_HOP 命令可为 RX 到 RX 间的跳频提供最快的方法,但它需要更多主机 MCU 的系统开销和管理。使用 RX\_HOP 命令时,周转时间为 75 µs。与 Start\_RX 或 RX 跳频相比,使用该方法时计时更快,因为合成器校准所需的计算之一被分给了主机,并必须由主机、VCO\_CNTO 来计算/存储。欲获取更多使用快速手动跳频的信息,请联系客户支持中心。

# 5.4. 发送器(TX)

Si4438 包含一个集成的 +20 dBm 发送器或功率放大器,可发送 –20 到 +20 dBm 的功率。在最大功率 6 dB 内的输出功率步幅低于 0.25 dB,但接近最低输出功率时,输出功率步幅会变大并变得更加非线性。Si4438 PA 可提供最高的效率和最低的电流消耗。PA 选项为单端型设计以易于和天线相匹配和实现低 BOM 成本。可自动实现自动倾斜上升和倾斜下降以减少不需要的频谱分散。

在芯片上的 PA 需要驱动天线的情况下,芯片的 TXRAMP 引脚会被默认禁用,以节省电流。在芯片上的 PA 需要驱动外部 PA、且外部 PA 需要斜升信号的情况下,TXRAMP 是需要使用的信号。设置 API 属性 PA\_MODE[7] = 1 以启动 TXRAMP。 随着在内部芯片上的 PA 上升或下降,TXRAMP 也会同时开始上升和下降。

升降速度通过 PA RAMP EX API 属性中的 TC[3:0] 进行编程,并具有以下特点:

Table 14. Ramp Times as a Function of TC[3:0] Value

| TC | Ramp Time (µs) |

|----|----------------|

| 0  | 1.25           |

| 1  | 1.33           |

| 2  | 1.43           |

| 3  | 1.54           |

| 4  | 1.67           |

| 5  | 1.82           |

| 6  | 2.00           |

| 7  | 2.22           |

| 8  | 2.50           |

| 9  | 2.86           |

| 10 | 3.33           |

| 11 | 4.00           |

| 12 | 5.00           |

| 13 | 6.67           |

| 14 | 10.00          |

| 15 | 20.00          |

当接近 Vhi 和 Vlo 时,升降曲线接近于线性升降曲线,具有平滑角。TXRAMP 引脚可在无需电压下降的情况下上升到 1 mA。TXRAMP 引脚的沉降能力相当于一个 10 kΩ 的下拉电阻。

当 Vdd > 3.3 V 时, Vhi = 3 V。当 Vdd < 3.3 V 时, Vhi 会紧随 Vdd, 并且升降时间也会减少。

当无需电流沉降到 TXRAMP 引脚时 , VIo = 0 V。如果需要 10uA 的电流沉降到芯片 , 则 VIo 为 10  $\mu$ A x 10k = 100 mV。

| Number | Command    | Summary                                                                           |

|--------|------------|-----------------------------------------------------------------------------------|

| 0x2200 | PA_MODE    | Sets PA type.                                                                     |

| 0x2201 | PA_PWR_LVL | Adjust TX power in fine steps.                                                    |

| 0x2202 |            | Adjust TX power in coarse steps and optimizes for different match configurations. |

| 0x2203 | PA_TC      | Changes the ramp up/down time of the PA.                                          |

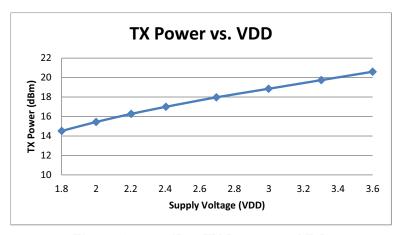

## 5.4.1. Si4438: +20 dBm PA

$+20~{

m dBm}$  配置使用 E 级的匹配配置。在表  $7-9~{

m phi}$  中给出了输出功率步幅、电压和温度的典型性能。输出功率通过  $PA_PWR_LVL$  API 分 128 个步幅进行改变。如需了解其他频率时匹配值、BOM 和性能的详细信息,请参阅 PA 匹配应用说明。

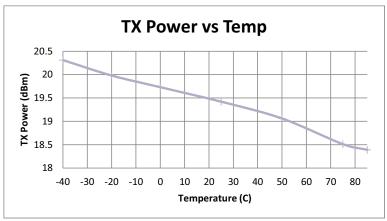

Figure 7. +20 dBm TX Power vs. PA\_PWR\_LVL

Figure 8. +20 dBm TX Power vs. VDD

Figure 9. +20 dBm TX Power vs. Temp

# 5.5. 晶体振荡器

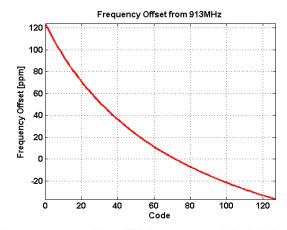

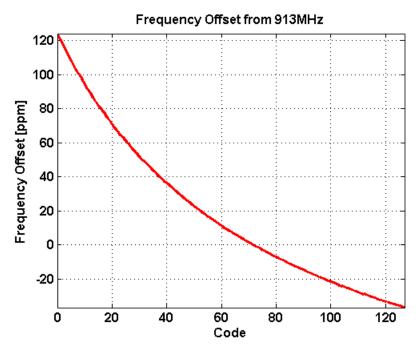

Si4438 包含一个具有快速启动时间低于 250 μs 的集成晶体振荡器。该设计的特别之处在于将要求的晶体负载电容集成在芯片上,以使外部部件的数量减少到最低。在默认情况下,晶体是唯一需要的芯片外部件。默认晶体为 30 MHz,但是电路可对任何 25 到 32 MHz 范围内的 XTAL 进行处理。如果使用非 30 MHz 的晶体,则必须对 POWER\_UP API 启动命令进行修改。也必须改变 WDS 计算器晶体频率字段以反映使用的频率。可对晶体负载电容进行数字编程以容纳具有各种负载电容的晶体和调整晶体振荡器的频率。通过 GLOBAL\_XO\_TUNE API 属性对晶体负载电容进行编程。总内部电容为 11 pF 并且可在 127 步幅(70 fF/步幅)内进行调整。晶体频率调整可以用于补偿晶体制造公差。电容器组的频率偏置特性在 图 10 中有说明。

Figure 10. Capacitor Bank Frequency Offset Characteristics

使用芯片上的温度传感器和合适的控制软件可以取消晶体的温度依存性。

# Si4438-C

可很容易地使用 TCXO 和外部信号源代替传统的 XTAL,并且应该连接到 XIN 引脚上。建议使用收到的时钟信号作为 600 mV 到 1.4 V 间的峰值间的摆动,并交流耦合到 XIN 引脚上。如果 TCXO 峰值间的摆动超过 1.4 V,则应使用直流耦合连接到 XIN 引脚。XIN 上允许的最大摆动为峰间 1.8 V。

只要 XIN 引脚上使用外部驱动时, XO 电容器组均应设置为 0。另外, 只要使用外部驱动时, POWER\_UP 命令就应该与 TCXO 选项一起被启用。

# 6. 数据处理和分组处理程序

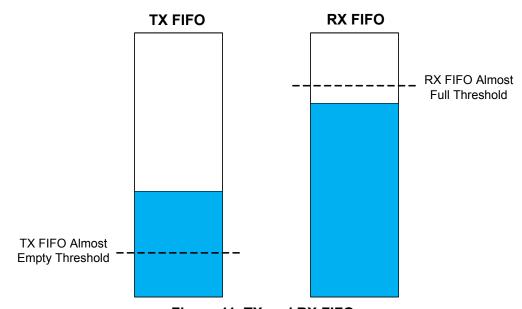

### 6.1. RX 和 TX FIFO

芯片中集成了两个 64 字节的 FIFO, 一个用于 RX, 一个用于 TX, 这在 图 11 中有说明。当写入命令寄存器 66h 时,数据导入 TX FIFO, 而从命令寄存器 77h 读取时,从 RX FIFO 中读取数据。当 FIFO 几乎清空时,TX FIFO 会出现阈值,该阈值通过 "TX\_FIFO\_EMPTY"属性进行设置。当 TX FIFO 中的数据达到近乎空阈值时,会发生中断事件。如果没有更多数据导入 FIFO,在 PACKET\_SENT 中断发生后芯片会自动退出 TX 状态。RX FIFO 有一个可编程的阈值,通过设置 "RX\_FIFO\_FULL"属性进行编程。当收到的 RX 数据穿越近乎满阈值时,就会通过 nIRQ 引脚对微控制器产生中断。微控制器然后需要从 RX FIFO 读取数据。RX 近乎满阈值读数说明主机可从当时的 RX FIFO 至少读取字节的阈值的数量。通过 "FIFO RESET"命令可清除或重置 TX 和 RX FIFO。

Figure 11. TX and RX FIFOs

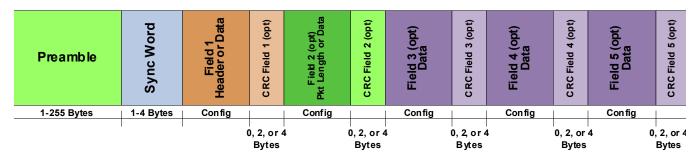

## 6.2. 分组处理程序

当使用 FIFO 时,自动分组处理可以用 TX 模式、RX 模式或两种模式进行启动。网络通信的一般字段,如前导码、同步字、报头、数据包长度和 CRC,可以进行自动配置添加到数据有效荷载中。产生数据包所需的字段很少发生改变,因此可以被存储到寄存器中。在 TX 模式下将这些字段自动添加到数据有效荷载中,并在 RX 模式下对其进行自动检测,这可大限度地减少微控制器和 Si4438 之间的通讯交流。也可大限度地减少微控制器所需的计算功率。数据包的一般结构在 图 12 中有说明。内部分组处理程序可启用和检测任何或所有字段。

Figure 12. Packet Handler Structure

这些字段都是可高度编程的并且可用来检测数据包结构中的任何一种模式。分组处理程序的一般功能包括:

- RX 模式下的前导码质量检测/验证 (PREAMBLE\_VALID 信号)

- RX 模式下的同步字检测 (SYNC\_OK 信号)

- RX 模式下的有效数据包检测 (PKT VALID 信号)

- RX 模式下的 CRC 错误检测 (CRC ERR 信号)

- RX 模式下的数据反白化和/或曼彻斯特解码(如果已启用)

- RX 模式下的匹配/报头检测

- RX 模式下将数据字段字节存储到 FIFO 存储器中

- TX 模式下的前导码字段构建

- TX 模式下的同步字构建

- TX 模式下从 FIFO 存储器中构建数据字段

- TX 模式下的 CRC 字段 (如果已启用)构建

- TX 模式下的数据白化和/或曼彻斯特编码(如果已启用)

如需了解如何配置分组处理程序的详细信息,请参见"AN626:用于 Si4438 RFIC 的分组处理程序操作"

# 7. RX 调制解调器配置

通过使用 WDS 设置计算器可以很容易地对 Si4438 进行配置,以适合不同的数据传输率、偏移、频率等,并可生成可供主机 MCU 使用的初始化文件。

# 8. 辅助块

# 8.1. 唤醒定时器和 32 kHz 时钟源

芯片包含一个集成的唤醒定时器,可用来定期从睡眠模式中唤醒芯片。唤醒定时器从内部 32 kHz RC 振荡器或外部 32 kHz XTAL 进行运行。

在睡眠模式时可对唤醒定时器进行配置。在进入睡眠模式之前,如果 GLOBAL\_WUT\_CONFIG 属性中的WUT\_EN = 1 ,唤醒定时器会按照 GLOBAL\_WUT\_R 和 GLOBAL\_WUT\_M 属性中定义的时间内进行计数。如果该中断在 INT\_CTL\_CHIP\_ENABLE 属性中被启用,在这个周期结束时,会在 nIRQ 引脚上产生中断。微控制器会通过 GET\_INT\_STATUS 或快速响应寄存器读取芯片中断状态来确认中断。计算唤醒周期的公式如下:

$$WUT = WUT\_M \times \frac{4 \times 2^{WUT\_R}}{32.768} [ms]$$

RC 振荡器频率会随温度而变化;因此,需要定期进行再校准。在 POWER\_UP 命令中 RC 振荡器会自动校准并从关机状态退出。为启用再校准功能,须在 GLOBAL\_WUT\_CONFIG 属性中设置 CAL\_EN,并且通过相同 API 属性中的 WUT\_CAL\_PERIOD[2:0] 选择想要的校准周期。在校准期间,32 kHz RC 振荡器频率会与 30 MHz XTAL 进行比较然后做相应的调整。校准需要启动 30 MHz XTAL,增加平均电流消耗;因此,较长的 CAL\_PERIOD 会导致较低的平均电流消耗。32 kHz XTAL 精确度由 XTAL 参数和内部电路组成。XTAL 精确度定义为 XTAL 初始误差 + XTAL 老化 + XTAL 温度漂移 + 内部振荡器电路的失谐。由内部电路引起的误差一般低于 10 ppm。请参阅 API 文件了解 WUT 相关的命令和属性详细信息。

# 8.2. 低占空比模式(自动 RX 唤醒)

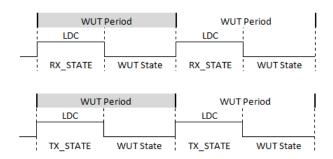

开启低占空比(LDC)模式是为了自动唤醒接收器,以检测是否存在有效信号,或启动发送器发送数据包。这实现了使用唤醒定时器(WUT)的 Si4438 的低电流轮询操作。当设置 WUT 时须通过 GLOBAL\_WUT\_CONFIG 属性设置 RX 和 TX LDC 操作。LDC 唤醒周期由以下公式决定:

LDC = WUT\_LDC

$$\times \frac{4 \times 2^{\text{WUT}_R}}{32.768}$$

[ms]

通过 GLOBAL\_WUT\_LDC 属性设置 WUT\_LDC 参数。WUT 周期的设置须与 LDC 模式持续时间相一致;如需了解相关 API 属性,请参见唤醒定时器(WUT)部分。

Figure 13. RX and TX LDC Sequences

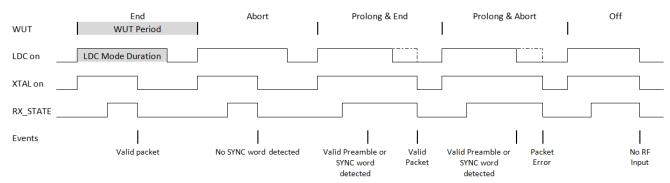

RX LDC 模式的基本操作在 图 14 中有说明。在 LDC 模式持续期间接收器会定期自我唤醒,以维持 RX\_STATE。如果未检测到有效前导码,而检测到接收错误,或者未接收到整个数据包,接收器会在 LDC 模式持续时间结束时恢复到 WUT 状态(即,就绪或睡眠)并维持至下个唤醒周期的开始。如果检测到有效前导码或同步字,接收器会延迟 LDC 模式持续时间以接收整个数据包。如果在两个 LDC 模式持续期间都未接收到数据包,则接收器会在最后一个 LDC 模式持续时间结束时恢复到 WUT 状态并维持到下一个唤醒周期。

Figure 14. Low Duty Cycle Mode for RX

在 TX LDC 模式下,发送器会定期自我唤醒,以发送数据缓冲器内的数据包。如果数据包已经发送,在INT\_CTL\_ENABLE 属性中设置选项后 nIRQ 就会走低。在发送后,发送器会立即恢复到 WUT 状态并维持至下个唤醒周期的结束。

## 8.3. 温度、电池电压和辅助 ADC

34

Si4438 产品系列包含一个用于测量内部电池电压的辅助 ADC、一个内部温度传感器或一个 GPIO 上的外部部件。 ADC 采用 SAR 体系结构并可达到 11 位的分辨率。有效位数(ENOB)为 9 位。当测量外部部件时,输入电压范围是 1 V,转换率在 300 Hz 到 2.44 kHz 之间。通过首先发送 GET\_ADC\_READING 命令和启用希望被读取的输入数据来读取 ADC 值。GPIO、电池或温度。25 °C 时的温度传感器精确度一般为 ±2 °C。如需了解 API 详细信息,请参阅 www.silabs.com 上的 EZRadioPRO API Documentation.zip 文件。

## 8.4. 低电量探测器

低电量探测器(LBD)作为唤醒定时器的一部分启用和使用。只有启用 WUT 时 LBD 功能方可使用,但是主机MCU可使用辅助 ADC 手动检测任何时间的电池电压。LBD 功能在 GLOBAL\_WUT\_CONFIG API 属性中启用。每次 WUT 结束时电池电压会与阈值进行比较。LBD 功能的阈值在 GLOBAL\_LOW\_BATT\_THRESH 中设置。阈值以50 mV 的步幅进行增加,范围在最低 1.5 V 到最高 3.05 V。LBD 的精确度为 ±3%。LBD 通知可作为 nIRQ 引脚上的中断进行配置,或作为 GPIO 之一上的直接功能启用。

## 8.5. 天线分集

为减轻因多径传播引起的频率选择性衰落,一些收发器系统采用天线分集的设计方案。在该设计方案中,使用两个天线。每次收发器进入 RX 模式时,每个天线中接收信号强度就会被评估。评估过程在数据包的前导部分进行。具有最强接收信号的天线就会用来接收 RX 数据包的剩余部分。同一个天线也会用来接收下一个相应的 TX 数据包。因具有集成的天线分集控制演算法,因此芯片完全支持天线多样性GPIOx 引脚上具有需要控制外部 SPDT RF 开关(如 PIN 二极管或 GaAs 开关)所需的信号。这些 GPIO 信号的操作是可以编程的,以适合不同的天线分集体系结构和配置。在 MODEM\_ANT\_DIV\_CONTROL API 属性描述中可发现 antdiv[2:0] 位,并可启动天线分集模式。GPIO 引脚可得到高达 5 mA 的电流;因此,如果有需要,GPIO 引脚可直接用来正向偏置 PIN 二极管。天线分集演算会在天线之间自动来回切换直至数据包开始到达。推荐的最佳天线选择前导码长度为 8 字节。

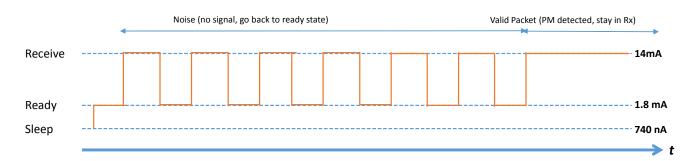

## 8.6. 前导探测模式

该操作模式适用于极低功率的应用中,在这些应用中功耗多少很重要。前导探测模式(PSM)利用数字信号达到检测器(DSA),数字信号到达检测器可实现在不降低敏感度的情况下在 8 个位时间内检测到前导。在设备通过无线寻找数据包期间,接收到的信号的快速检测可与接收器的工作周期相结合。当使用该模式时平均接收电流会大大降低。在接收到的信号计时未知的应用中,由于 RX 的非活动时间由数据传输率和前导码长度决定,因此节省的功率量主要取决于数据传输率和前导码长度。在睡眠时间固定和接收到的信号计时已知的应用中,平均电流也取决于睡眠时间。PSM 模式与低占空比模式相似,但具有更快的信号检测和接收器的自主工作周期,以达到更低的平均接收电流。该模式可与活跃 RX 电流为 10 mA 的低功率模式(LP)一起使用,或可与活跃电流 RX 电流为 13 mA 的高性能(HP)模式一起使用。

Figure 15. Preamble Sense Mode

# Table 15. Data Rates\*

|                     | Data Rate |          |         |          |    |

|---------------------|-----------|----------|---------|----------|----|

|                     | 1.2 kbps  | 9.6 kbps | 50 kbps | 100 kbps |    |

| PM length = 4 bytes | 6.48      | 6.84     | 8.44    | 10.43    | mA |

| PM length = 8 bytes | 3.83      | 3.96     | 4.57    | 5.33     | mA |

36

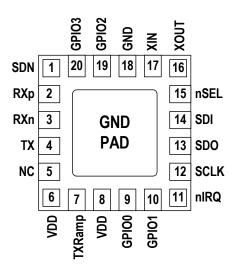

# 9. 引脚描述:Si4438-C

| Pin | Pin Name | 1/0 | Description                                                                                                                                                                                          |

|-----|----------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | SDN      | I   | Shutdown Input Pin. 0-VDD V digital input. SDN should be = 0 in all modes except Shutdown mode. When SDN = 1, the chip will be completely shut down, and the contents of the registers will be lost. |

| 2   | RXp      | I   | Differential RF Input Pins of the LNA.                                                                                                                                                               |

| 3   | RXn      | I   | See application schematic for example matching network.                                                                                                                                              |

| 4   | TX       | 0   | Transmit Output Pin.  The PA output is an open-drain connection, so the L-C match must supply VDD (+3.3 VDC nominal) to this pin.                                                                    |

| 5   | NC       |     | It is recommended to connect this pin to GND per the reference design schematic. Not connected internally to any circuitry.                                                                          |

| 6   | VDD      | VDD | +1.8 to +3.8 V Supply Voltage Input to Internal Regulators. The recommended VDD supply voltage is +3.3 V.                                                                                            |

| 7   | TXRAMP   | 0   | Programmable Bias Output with Ramp Capability for External FET PA. See "5.4. 发送器(TX)" 页 27.                                                                                                          |

| 8   | VDD      | VDD | +1.8 to +3.8 V Supply Voltage Input to Internal Regulators. The recommended VDD supply voltage is +3.3 V.                                                                                            |

| 9   | GPIO0    | I/O | General Purpose Digital I/O.                                                                                                                                                                         |

| 10  | GPIO1    | I/O | May be configured through the registers to perform various functions including: Microcontroller Clock Output, FIFO status, POR, Wake-Up timer, Low Battery Detect, TRSW, AntDiversity control, etc.  |

| Pin | Pin Name   | 1/0 | Description                                                                                                                                                                                                                                                                                                                                                   |  |

|-----|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 11  | nIRQ       | 0   | General Microcontroller Interrupt Status Output.  When the Si4438 exhibits any one of the interrupt events, the nIRQ pin will be set low = 0. The Microcontroller can then determine the state of the interrupt by reading the interrupt status. No external resistor pull-up is required, but it may be desirable if multiple interrupt lines are connected. |  |

| 12  | SCLK       | I   | Serial Clock Input.  0-VDD V digital input. This pin provides the serial data clock function for the 4-line serial data bus. Data is clocked into the Si4438 on positive edge transitions.                                                                                                                                                                    |  |

| 13  | SDO        | 0   | <b>0–VDD V Digital Output.</b> Provides a serial readback function of the internal control registers.                                                                                                                                                                                                                                                         |  |

| 14  | SDI        | I   | Serial Data Input.  0-VDD V digital input. This pin provides the serial data stream for the 4-line serial data bus.                                                                                                                                                                                                                                           |  |

| 15  | nSEL       | I   | Serial Interface Select Input.  0-VDD V digital input. This pin provides the Select/Enable function for the 4-line serial data bus.                                                                                                                                                                                                                           |  |

| 16  | XOUT       | 0   | Crystal Oscillator Output.  Connect to an external 25 to 32 MHz crystal, or leave floating when driving with an external source on XIN.                                                                                                                                                                                                                       |  |

| 17  | XIN        | I   | Crystal Oscillator Input.  Connect to an external 25 to 32 MHz crystal, or connect to an external source.                                                                                                                                                                                                                                                     |  |

| 18  | GND        | GND | When using a XTAL, leave floating per the reference design schematic. When using a TCXO, connect to TCXO GND which should be separate from the board reference ground plane.                                                                                                                                                                                  |  |

| 19  | GPIO2      | I/O | General Purpose Digital I/O.                                                                                                                                                                                                                                                                                                                                  |  |

| 20  | GPIO3      | I/O | May be configured through the registers to perform various functions, including Microcontroller Clock Output, FIFO status, POR, Wake-Up timer, Low Battery Detect, TRSW, AntDiversity control, etc.                                                                                                                                                           |  |

| PKG | PADDLE_GND | GND | The exposed metal paddle on the bottom of the Si4438 supplies the RF and circuit ground(s) for the entire chip. It is very important that a good solder connection is made between this exposed metal paddle and the ground plane of the PCB underlying the Si4438.                                                                                           |  |

38

# 10. 订购信息

| Part Number*          | Description                                                     | Package Type      | Operating<br>Temperature |

|-----------------------|-----------------------------------------------------------------|-------------------|--------------------------|

| Si4438-C2A-GM         | ISM EZRadioPRO Transceiver                                      | QFN-20<br>Pb-free | –40 to 85 °C             |

| *Note: Add an "(R)" a | t the end of the device part number to denote tape and reel opt | ion.              |                          |

# 11. 封装外形: Si4438

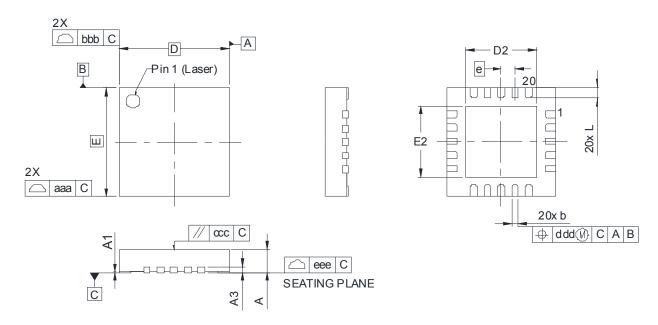

图 16 说明了 Si4438 的封装详细信息。表 16 列出了插图中外形尺寸值。

Figure 16. 20-Pin Quad Flat No-Lead (QFN)

**Table 16. Package Dimensions**

| Dimension | Min      | Nom      | Max  |

|-----------|----------|----------|------|

| Α         | 0.80     | 0.85     | 0.90 |

| A1        | 0.00     | 0.02     | 0.05 |

| A3        |          | 0.20 REF |      |

| b         | 0.18     | 0.25     | 0.30 |

| D         | 4.00 BSC |          |      |

| D2        | 2.45     | 2.60     | 2.75 |

| е         | 0.50 BSC |          |      |

| Е         |          | 4.00 BSC |      |

| E2        | 2.45     | 2.60     | 2.75 |

| L         | 0.30     | 0.40     | 0.50 |

| aaa       | 0.15     |          |      |

| bbb       | 0.15     |          |      |

| ccc       | 0.10     |          |      |

| ddd       | 0.10     |          |      |

| eee       | 0.08     |          |      |

#### Notes:

- 1. All dimensions are shown in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and tolerancing per ANSI Y14.5M-1994.

- This drawing conforms to the JEDEC Solid State Outline MO-220, Variation VGGD-8.

- **4.** Recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for Small Body Components.

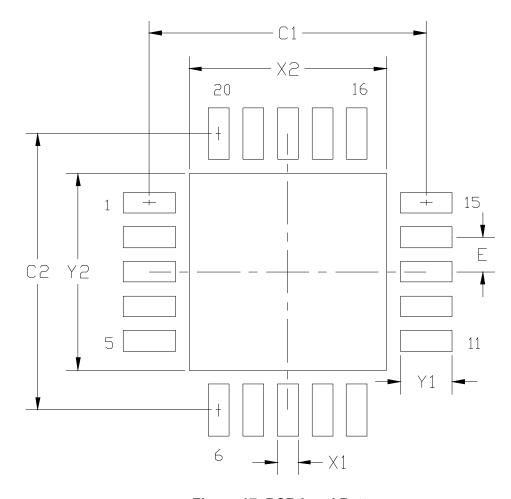

# 12. PCB 焊盘图案: Si4438

图 17说明了 Si4438 的 PCB 焊盘图案详细信息。表 17 列出插图中的外形尺寸值。

Figure 17. PCB Land Pattern

**Table 17. PCB Land Pattern Dimensions**

| Symbol | Millimeters |       |

|--------|-------------|-------|

|        | Min         | Max   |

| C1     | 3.90        | 4.00  |

| C2     | 3.90        | 4.00  |

| E      | 0.50        | ) REF |

| X1     | 0.20        | 0.30  |

| X2     | 2.55        | 2.65  |

| Y1     | 0.65        | 0.75  |

| Y2     | 2.55        | 2.65  |

#### General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. This land pattern design is based on IPC-7351 guidelines.

#### Solder Mask Design

3. All metal pads are to be non-solder mask defined (NSMD). Clearance between the solder mask and the metal pad is to be 60  $\mu$ m minimum, all the way around the pad.

#### Stencil Design

- **4.** A stainless steel, laser-cut and electro-polished stencil with trapezoidal walls should be used to assure good solder paste release.

- 5. The stencil thickness should be 0.125 mm (5 mils).

- **6.** The ratio of stencil aperture to land pad size should be 1:1 for the perimeter pads.

- 7. A 2x2 array of 1.10 x 1.10 mm openings on 1.30 mm pitch should be used for the center ground pad.

# **Card Assembly**

- 8. A No-Clean, Type-3 solder paste is recommended.

- **9.** The recommended card reflow profile is per the JEDEC/IPC J-STD-020 specification for small body components.

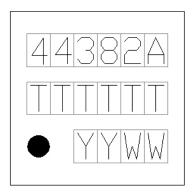

# 13. 顶部标记

# 13.1. Si4438 顶部标记

# 13.2. 顶部标记说明

| Mark Method    | YAG Laser                                       |                                                                                                                      |  |

|----------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| Line 1 Marking | Part Number 44382A = Si4438 Rev 2A <sup>1</sup> |                                                                                                                      |  |

| Line 2 Marking | TTTTTT = Internal Code                          | Internal tracking code. <sup>2</sup>                                                                                 |  |

| Line 2 Marking | YY = Year<br>WW = Workweek                      | Assigned by the Assembly House. Corresponds to the last significant digit of the year and workweek of the mold date. |  |

#### Notes:

- 1. The first letter after the part number is part of the ROM revision. The last letter indicates the firmware revision.

- 2. The first letter of this line is part of the ROM revision.

# 联系信息

Silicon Laboratories Inc.

400 West Cesar Chavez

Austin, TX 78701

电话:1+(512) 416-8500 传真:1+(512) 416-9669 免费电话:1+(877) 444-3032

请访问 Silicon Labs 技术支持网页:

https://www.silabs.com/support/pages/contacttechnicalsupport.aspx

并注册提交技术支持请求。

#### 专利通告

Silicon Labs 通过研究和开发方面的投资为我们的客户提供低功耗、小型、模拟敏感混合信号解决方案,让我们的客户在市场上脱颖而出。 Silicon Labs 广泛的专利组合是我们独特的方法和世界一流工程团队的证明。

本文信息在出版时准确无误,但如有更改,恕不另行通知。Silicon Laboratories 对于错误和遗漏不承担任何责任,且不对因使用此处信息而导致的任何后果负责。另外,Silicon Laboratories 对于未阐述的功能或参数的正常使用不承担责任。Silicon Laboratories 保留修改文中信息的权利,恕不另行通知。Silicon Laboratories 对其产品用于任何特定用途的合适性不作任何担保、声明或保证,亦不承担因应用或使用其任何产品或电路而产生的任何责任,特别对包括但不限于间接损坏或附带损坏的任何和所有后果概不负责。Silicon Laboratories 产品未设计、计划或授权用于旨在支持或维持生命的用途,或由于 Silicon Laboratories 产品故障可能造成人身伤亡情形的任何其他应用中。如果买方购买或将 Silicon Laboratories 的产品用于任何非设计用途或未经授权的应用中,买方应保证 Silicon Laboratories 不会受到任何索赔和损害。

Silicon Laboratories 和 Silicon Labs 均为 Silicon Laboratories Inc. 的商标。 本文提及的其他产品或品牌名称均为其相应持有人的商标或者注册商标。