# WT41-A / WT41-N

DATA SHEET Wednesday, 21 January 2015 Version 1.45

### **VERSION HISTORY**

| Version | Comment                                                                         |

|---------|---------------------------------------------------------------------------------|

| 0.1     | First draft                                                                     |

| 0.2     | Description and product codes added                                             |

| 0.21    | Dimensions updated, layout guide added, UART and USB chapters added             |

| 0.22    | Pin descriptions, PCM, USB, UART, SPI                                           |

| 0.3     | Physical dimensions corrected                                                   |

| 0.31    | Product codes corrected                                                         |

| 0.32    | Recommendation for a power-up reset circuitry added to chapter 10               |

| 0.4     | Pins 1 and 52 (GND) removed. Dimensions updated, recommended land pattern added |

| 0.5     | Certification information added                                                 |

| 0.6     | Physical dimensions and recommended PCB land pattern updated                    |

| 0.7     | Figure 7 recommended land pattern corrected                                     |

| 1.0     | Radio and antenna characteristics, layout guide for WT41-N                      |

| 1.1     | Japan certification info added                                                  |

| 1.2     | FCC RF radiation exposure statement updated                                     |

| 1.3     | Layout guide updated                                                            |

| 1.31    | VDD added to table 1                                                            |

| 1.32    | FCC and IC statements updated                                                   |

| 1.33    | PIO current drive capability added. List of approved antennas added.            |

| 1.34    | IC statements in French added                                                   |

| 1.35    | Information about Japan compliance updated                                      |

| 1.36    | Absolute maximum supply voltage 3.7V                                            |

| 1.37    | MIC Japan information updated                                                   |

| 1.4  | FCC C2PC to remove 20 cm restriction                      |

|------|-----------------------------------------------------------|

| 1.41 | MIC Japan ID corrected                                    |

| 1.42 | MSL information updated                                   |

| 1.43 | TXP vs VDD_PA figure added                                |

| 1.44 | Minor changes                                             |

| 1.45 | Monopole chip antenna added to prequalified antennas list |

### TABLE OF CONTENTS

| 1 | Or  | dering Information                                                     | 8    |

|---|-----|------------------------------------------------------------------------|------|

| 2 | Pir | nout and Terminal Description                                          | 9    |

| 3 | Ele | ectrical Characteristics                                               | . 12 |

|   | 3.1 | Absolute Maximum Ratings                                               | . 12 |

|   | 3.2 | Recommended Operating Conditions                                       | . 12 |

|   | 3.3 | PIO Current Sink and Source Capability                                 | . 12 |

|   | 3.4 | Transmitter Performance For BDR                                        | . 13 |

|   | 3.5 | Radiated Spurious Emissions                                            | . 14 |

|   | 3.6 | Receiver Performance                                                   | . 15 |

|   | 3.7 | Current Consumption                                                    | . 15 |

|   | 3.8 | Antenna Performance and Radiation Patterns                             | . 16 |

| 4 | Ph  | ysical Dimensions                                                      | . 20 |

| 5 | La  | yout Guidelines                                                        | . 22 |

|   | 5.1 | WT41-A                                                                 | . 22 |

|   | 5.2 | WT41-N                                                                 | . 23 |

|   | 5.2 | 2.1 Layout for WT41-N with u.fl connector close to RF pin              | . 23 |

|   | 5.2 | 2.2 Layout for WT41-N with 50 ohm trace from RF pin to a SMA connector | . 23 |

| 6 | UA  | ART Interface                                                          | . 25 |

|   | 6.1 | UART Bypass                                                            | . 27 |

|   | 6.2 | UART Configuration While Reset is Active                               | . 27 |

|   | 6.3 | UART Bypass Mode                                                       | . 27 |

| 7 | US  | SB Interface                                                           | . 28 |

|   | 7.1 | USB Data Connections                                                   | . 28 |

|   | 7.2 | USB Pull-Up resistor                                                   | . 28 |

|   | 7.3 | USB Power Supply                                                       | . 28 |

|   | 7.4 | Self-Powered Mode                                                      | . 28 |

|   | 7.5 | Bus-Powered Mode                                                       | . 29 |

|   | 7.6 | USB Suspend Current                                                    | . 30 |

|   | 7.7 | USB Detach and Wake-Up Signaling                                       | . 30 |

|   | 7.8 | USB Driver                                                             | . 31 |

|   | 7.9 | USB v2.0 Compliance and Compatibility                                  | . 31 |

| 8 | Se  | rial Peripheral Interface (SPI)                                        | . 32 |

| 9 | PC  | CM Codec Interface                                                     | . 33 |

|   | 9.1 | PCM Interface Master/Slave                                             | . 33 |

|   | 9.2 | Long Frame Sync                                                        | . 34 |

|   | 9.3 | Short Frame Sync                                                       | . 34 |

|   | 9.4 | Multi-slot Operation                                                   | . 35 |

| 9.5  | GC      | I Interface                        | 35 |

|------|---------|------------------------------------|----|

| 9.6  | Slot    | ts and Sample Formats              | 36 |

| 9.7  | Add     | litional Features                  | 37 |

| 9.8  | PC      | M_CLK and PCM_SYNC Generation      | 37 |

| 9.9  | PC      | M Configuration                    | 38 |

| 10   | I/O Pa  | arallel Ports                      | 40 |

| 10.1 | l       | PIO Defaults                       | 40 |

| 11   | Reset   |                                    | 41 |

| 11.1 | l       | Pin States on Reset                | 42 |

| 12   | Certifi | cations                            | 43 |

| 12.1 | l       | Bluetooth                          | 43 |

| 12.2 | 2       | FCC                                | 43 |

| 12.3 | 3       | IC (Industry Canada)               | 44 |

| 1:   | 2.3.1   | IC                                 | 45 |

| 12.4 | 1       | CE                                 |    |

| 12.5 | 5       | Japan                              | 47 |

| 12.6 | 6       | Qualified Antenna Types for WT41-N | 47 |

| 12.7 | 7       | Moisture Sensitivity Level (MSL)   | 48 |

| 13   | Conta   | ct Information                     | 49 |

### WT41 Bluetooth® Module

### DESCRIPTION

WT41 is a long range class 1, Bluetooth® 2.1 + EDR module. WT41 is a highly integrated and sophisticated Bluetooth® module, containing all the necessary elements from Bluetooth® radio to antenna and a fully implemented protocol stack. Therefore WT41 provides an ideal solution for developers who want to integrate Bluetooth® wireless technology into their design with limited knowledge of Bluetooth® and RF technologies. WT41 is optimized for long range applications and since it contains a RF power amplifier, low noise amplifier and a highly efficient chip antenna. With 115 dB radio budget WT41 can reach over 1 km range in line off sight.

By default WT41 module is equipped with powerful and easy-to-use iWRAP firmware. iWRAP enables users to access Bluetooth® functionality with simple ASCII commands delivered to the module over serial interface - it's just like a Bluetooth® modem.

#### **APPLICATIONS:**

- Hand held terminals

- Industrial devices

- Point-of-Sale systems

- PCs

- Personal Digital Assistants (PDAs)

- Computer Accessories

- Access Points

- Automotive Diagnostics Units

### FEATURES:

- Fully Qualified Bluetooth v2.1 + EDR end product,

- CE, FCC, IC and MIC Japan

- TX power : 19 dBm

- RX sensitivity : -92 dBm

- Higly efficient chip antenna, U.FL connector or RF pin

- Class 1, range up to 800 meters

- Industrial temperature range from -40°C to  $+85^{\circ}\text{C}$

- RoHS Compliant

- USB interface (USB 2.0 compatible)

- UART with bypass mode

- 6 x GPIO

- 1 x 8-bit AIO

- Support for 802.11 Coexistence

- Integrated iWRAP<sup>TM</sup> Bluetooth stack or HCI firmware

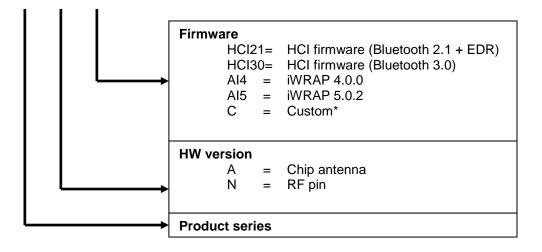

# **1** Ordering Information

### WT41-A-HCI

### **Dinaut and Terminal Description**

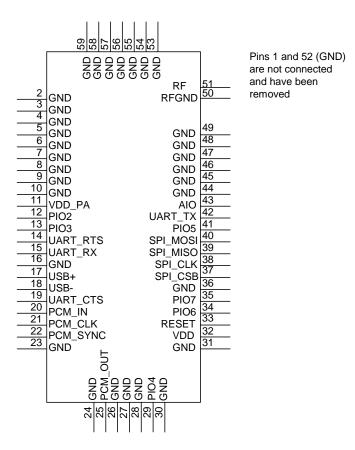

2

Figure 1: WT41 pin out

|        | PIN<br>NUMBER                                  | PAD TYPE                         | DESCRIPTION                                                                            |

|--------|------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------------|

| NC     | 1, 52                                          | Not connected                    | Pins 1 and 52 (GND) have been removed from the module.                                 |

| RESET  | 33                                             | Input, weak internal pull-<br>up | Active low reset. Keep low for >5 ms to cause a reset                                  |

| GND    | 2-10, 16,<br>23,24,26-<br>28, 30,<br>31,36,44- | GND                              | GND                                                                                    |

| RF     | 51                                             | RF output                        | RF output for WT41-N. For WT41-A<br>and WT41-E this pin is not connected               |

| RFGND  | 50                                             | GND                              | RF ground. Connected to GND internally to the module.                                  |

| VDD_PA | 11                                             | Supply voltage                   | Supply voltage for the RF power amplifier<br>and the low noise amplifier of the module |

| VDD    | 32                                             | Supply voltage                   | Supply voltage for BC4 and the flash<br>memory                                         |

Table 1: Supply and RF Terminal Descriptions

Silicon Labs

| PIO PORT | PIN<br>NUMBER | PAD TYPE                                                          | DESCRIPTION                               |

|----------|---------------|-------------------------------------------------------------------|-------------------------------------------|

| PIO[2]   | 12            | Bi-directional, programmamble strength internal pull-down/pull-up | Programmamble input/output<br>line        |

| PIO[3]   | 13            | Bi-directional, programmamble strength internal pull-down/pull-up | Programmamble input/output<br>line        |

| PIO[4]   | 29            | Bi-directional, programmamble strength internal pull-down/pull-up | Programmamble input/output<br>line        |

| PIO[5]   | 41            | Bi-directional, programmamble strength internal pull-down/pull-up | Programmamble input/output<br>line        |

| PIO[6]   | 34            | Bi-directional, programmamble strength internal pull-down/pull-up | Programmamble input/output<br>line        |

| PIO[7]   | 35            | Bi-directional, programmamble strength internal pull-down/pull-up | Programmamble input/output<br>line        |

| AIO[1]   | 43            | Bi-directional                                                    | Programmamble analog<br>input/output line |

### **Table 2: GPIO Terminal Descriptions**

| SPI<br>INTERFACE | PIN<br>NUMBER | PAD TYPE                                           | DESCRIPTION             |

|------------------|---------------|----------------------------------------------------|-------------------------|

| PCM_OUT          | 25            | CMOS output, tri-state,<br>weak internal pull-down | Synchronous data output |

| PCM_IN           | 20            | CMOS input, weak<br>internal pull-down             | Synchronous data input  |

| PCM_SYNC         | 22            | Bi-directional, weak<br>internal pull-down         | Synchronous data sync   |

| PCM_CLK          | 21            | Bi-directional, weak<br>internal pull-down         | Synchronous data clock  |

### **Table 3: PCM Terminal Descriptions**

| UART<br>Interfaces | PIN<br>NUMBER | PAD TYPE                                                   | DESCRIPTION                      |  |  |

|--------------------|---------------|------------------------------------------------------------|----------------------------------|--|--|

| UART_TX            | 42            | CMOS output, tri-<br>state, with weak<br>internal pull-up  | UART data output, active high    |  |  |

| UART_RTS#          | 14            | CMOS output, tri-<br>state, with weak<br>internal pull-up  | UART request to send, active low |  |  |

| UART_RX            | 15            | CMOS input, tri-<br>state, with weak<br>internal pull-down | UART data input, active high     |  |  |

| UART_CTS#          | 19            | CMOS input, tri-<br>state, with weak<br>internal pull-down | UART clear to send, active low   |  |  |

**Table 4: UART Terminal Descriptions**

| USB Interfaces | PIN<br>NUMBER | PAD TYPE      | DESCRIPTION                                 |

|----------------|---------------|---------------|---------------------------------------------|

| USB+           | 17            | Bidirectional | USB data plus with selectable internal 1.5k |

| 030+           |               |               | pull-up resistor                            |

| USB-           | 18            | Bidirectional | USB data minus                              |

Table 5: USB Terminal Descriptions

| SPI<br>INTERFACE | PIN<br>NUMBER | PAD TYPE                                                  | DESCRIPTION                                                |

|------------------|---------------|-----------------------------------------------------------|------------------------------------------------------------|

| SPI_MOSI         | 40            | CMOS input with weak<br>internal pull-down                | SPI data input                                             |

| SPI_CS#          | 37            | CMOS input with weak<br>internal pull-up                  | Chip select for Serial Peripheral<br>Interface, active low |

| SPI_CLK          | 38            | CMOS input with weak<br>internal pull-down                | SPI clock                                                  |

| SPI_MISO         | 39            | CMOS output, tristate,<br>with weak internal pull<br>down | SPI data output                                            |

Table 6: Terminal Descriptions

# 3 Electrical Characteristics

## 3.1 Absolute Maximum Ratings

| Rating                  | Min     | Max     | Unit |

|-------------------------|---------|---------|------|

| Storage Temperature     | -40     | 85      | °C   |

| VDD_PA, VDD             | -0.4    | 3.7     | V    |

| Other Terminal Voltages | VSS-0.4 | VDD+0.4 | V    |

Table 7: Absolute Maximum Ratings

## 3.2 Recommended Operating Conditions

| Rating                      | Min | Max | Unit |

|-----------------------------|-----|-----|------|

| Operating Temperature Range | -40 | 85  | С°   |

| VDD_PA, VDD <sup>*)</sup>   | 3.0 | 3.6 | V    |

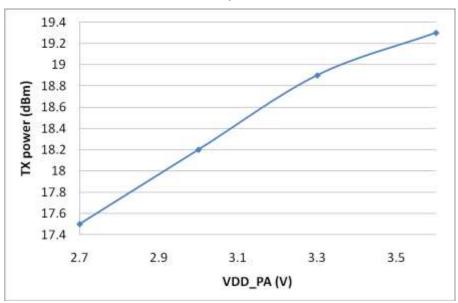

\*) VDD\_PA has an effect on the RF output power.

Table 8: Recommended Operating Conditions

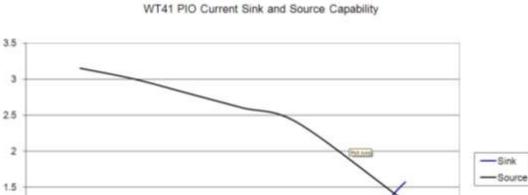

## 3.3 PIO Current Sink and Source Capability

Dutput voltage (V)

1

0.5

0

0

5

10

15

20

1 (mA)

Figure 2: WT41 PIO Current Drive Capability

25

30

35

40

# 3.4 Transmitter Performance For BDR

| RF Characetristics, VDD = 3.3V @ room<br>temperature unless otherwise specified |                                | Min | Тур | Max | Bluetooth<br>Specification | Unit |

|---------------------------------------------------------------------------------|--------------------------------|-----|-----|-----|----------------------------|------|

| maximum RF                                                                      | Transmit Power                 | 17  | 19  | 20  | 20                         | dBm  |

| RF power variation o                                                            | ver temperature range          |     |     | 4   | -                          | dB   |

| RF power variation ove                                                          | er supply voltage range (*     |     |     | 1.5 | -                          | dB   |

| RF power variation over BT band                                                 |                                | 0.1 | 1   | 2   | -                          | dB   |

| RF power co                                                                     | RF power control range (*      |     |     | 19  |                            |      |

| 20dB band width f                                                               | or modulated carrier           |     | 942 |     | 1000                       | kHz  |

|                                                                                 | $F = F_0 \pm 2MHz$             |     |     | -20 | -20                        |      |

| ACP (1                                                                          | $F = F_0 \pm 3MHz$             |     |     | -40 | -40                        |      |

|                                                                                 | $F = F_0 > 3MHz$               |     |     | -40 | -40                        |      |

| Drift rate                                                                      |                                |     | 7   |     | +/-25                      | kHz  |

| $\Delta F_{1avg}$                                                               |                                |     | 169 |     | 140<175                    | kHz  |

| ΔF1 <sub>max</sub>                                                              |                                |     | 161 |     | 140<175                    | kHz  |

|                                                                                 | $_{\rm g}/\Delta F_{\rm 1avg}$ |     | 1.1 |     | >=0.8                      |      |

Antenna gain 2.3dBi taken into account

### Table 9: Transmitter performance for BDR

Figure 3: Typical TX power as a function of VDD\_PA

# 3.5 Radiated Spurious Emissions

| Standard                       | Band / Frequency                      | Min<br>(AVG /<br>PEAK) | Typ<br>(AVG /<br>PEAK) | Max<br>(AVG /<br>PEAK) | Limit by the Standard<br>(AVG / PEAK) | Unit   |

|--------------------------------|---------------------------------------|------------------------|------------------------|------------------------|---------------------------------------|--------|

|                                | 2nd harmonic                          |                        | 52                     | 54/58                  | 54 / 74                               | dBuV/m |

|                                | 3rd harmonic                          |                        | 51                     | 54/58                  | 54 / 74                               | dBuV/m |

|                                | Band edge<br>2390MHz                  |                        | 50/60                  | 52/63                  | 54 / 74                               | dBuV/m |

| FCC part 15<br>transmitter     | Band edge<br>2483.5MHz                |                        | 52/65                  | 54/67                  | 54 / 74                               | dBuV/m |

| spurious<br>emissions          | Band edge<br>2400MHz<br>(conducted)   |                        | -50                    |                        | -20                                   | dBc    |

|                                | Band edge<br>2483.5MHz<br>(conducted) |                        | -58                    |                        | -20                                   | dBc    |

| ETSI EN 300 328<br>transmitter | Band edge<br>2400MHz                  |                        | -39                    | -36                    | -30                                   | dBm    |

| spurious                       | 2nd harmonic                          |                        | -41                    |                        | -30                                   | dBm    |

| emissions                      | 3rd harmonic                          |                        | -41                    |                        | -30                                   | dBm    |

| ETSI EN 300 328                | (2400 - 2479) MHz                     |                        | -                      |                        | -47                                   | dBm    |

| receiver spurious              | (1600 - 1653) MHz                     |                        | -52                    |                        | -47                                   | dBm    |

Table 10:Radiated spurious emission for WT41-A

| Standard                   |                                       | Min<br>(AVG /<br>PEAK) | Typ (AVG<br>/ PEAK) | Max<br>(AVG /<br>PEAK) | Limit by the Standard<br>(AVG / PEAK) | Unit   |

|----------------------------|---------------------------------------|------------------------|---------------------|------------------------|---------------------------------------|--------|

|                            | 2nd harmonic                          |                        | <48/55              | 50/56                  | 54 / 74                               | dBuV/m |

|                            | 3rd harmonic                          |                        | <48/51              | 48/52                  | 54 / 74                               | dBuV/m |

|                            | Band edge<br>2390MHz                  |                        | 50/60               | 52/63                  | 54 / 74                               | dBuV/m |

| FCC part 15<br>transmitter | Band edge<br>2483.5MHz                |                        | 52/65               | 54/67                  | 54 / 74                               | dBuV/m |

| spurious emissions         | Band edge 2400<br>MHz (conducted)     |                        | -50                 |                        | -20                                   | dBc    |

|                            | Band edge<br>3483.5MHz<br>(conducted) |                        | -58                 |                        | -20                                   | dBc    |

| ETSI EN 300 328            | Band edge<br>2400MHz                  |                        | -39                 | -36                    | -30                                   | dBm    |

| transmitter                | 2nd harmonic                          |                        |                     |                        | -30                                   | dBm    |

| spurious emissions         | 3rd harmonic                          |                        |                     |                        | -30                                   | dBm    |

| ETSI EN 300 328            | (2400 - 2479) MHz                     |                        |                     |                        | -47                                   | dBm    |

| receiver spurious          | (1600 - 1653) MHz                     |                        |                     |                        | -47                                   | dBm    |

Table 11: Radiated spurious emission for WT41-N

## 3.6 Receiver Performance

Antenna gain not taken into account

| RF characteristis, VDD = 3.3V,<br>room temperature (** | Packet type | Min | Тур | Max | Bluetooth<br>Spefication | Unit |

|--------------------------------------------------------|-------------|-----|-----|-----|--------------------------|------|

|                                                        | DH1         |     | -92 |     | -70                      | dBm  |

|                                                        | DH3         |     | -92 |     |                          | dBm  |

|                                                        | DH5         |     | -91 |     |                          | dBm  |

|                                                        | 2-DH1       |     | -94 |     |                          | dBm  |

| Sensitivity for 0.1% BER                               | 2-DH3       |     | -93 |     |                          | dBm  |

|                                                        | 2-DH5       |     | -93 |     |                          | dBm  |

|                                                        | 3-DH1       |     | -88 |     |                          | dBm  |

|                                                        | 3-DH3       |     | -85 |     |                          | dBm  |

|                                                        | 3-DH5       |     | -84 |     |                          | dBm  |

| Sensitivity variation over                             |             |     |     |     |                          |      |

| temperature range                                      |             |     | TBD |     |                          |      |

### Table 12: Receiver sensitivity

# 3.7 Current Consumption

| Opearation mode       | Peak (mA) | AVG (mA) |

|-----------------------|-----------|----------|

| Stand-by, page mode 0 | -         | 2.1      |

| TX 3DH5               | 100.5     | 77.6     |

| TX 2DH5               | 99.3      | 77.6     |

| TX 3DH3               | 98.1      | 71.1     |

| TX 2DH3               | 98.1      | 71.2     |

| TX 2DH1               | 98.7      | 51.6     |

| TX DH5                | 164       | 120      |

| TX DH1                | 166       | 67.3     |

| RX                    | 56.8      | 52.6     |

| Deep sleep            |           | 0.36     |

| Inquiry               | 169.3     | 58.7     |

Table 13: Current consumption

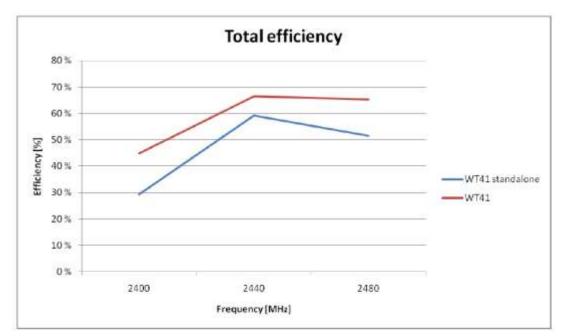

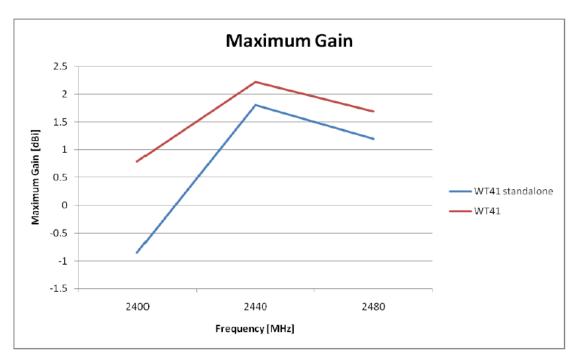

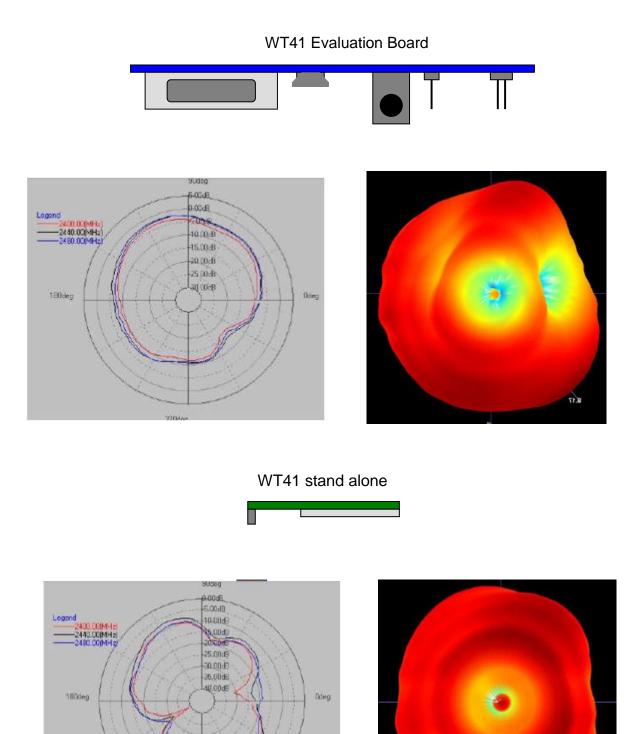

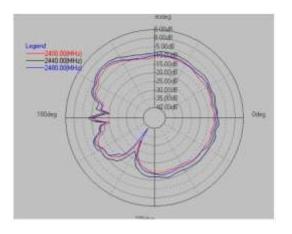

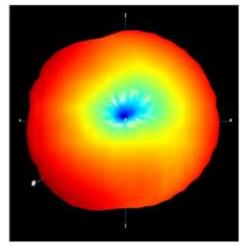

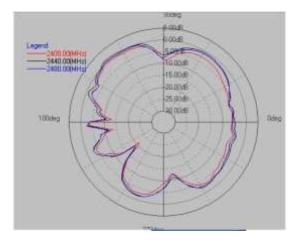

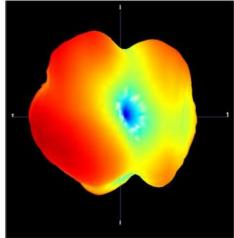

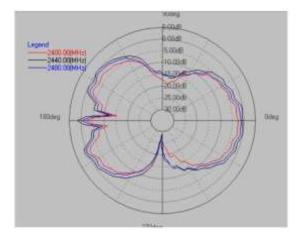

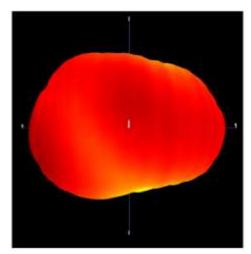

## 3.8 Antenna Performance and Radiation Patterns

Antenna performance measured from the module as a standalone and as mounted to the evaluation board.

Table 14: Total efficiency of the chip antenna

Table 15: Peak gain of the chip antenna

22114

WT41 stand alone

Back side of WT41-A

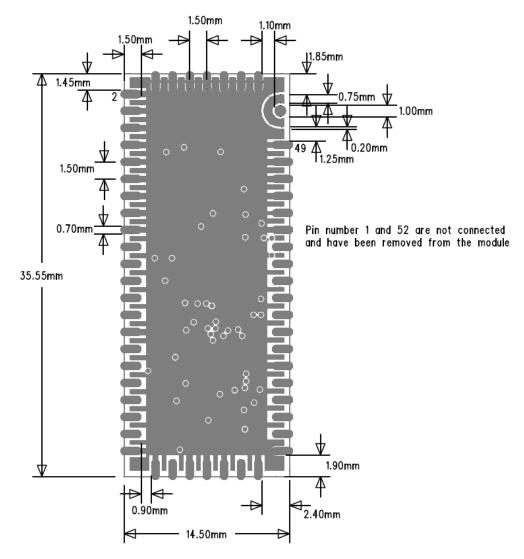

# 4 Physical Dimensions

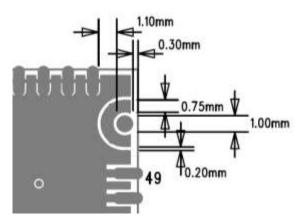

Figure 4: Physical dimensions (top view)

Figure 5: Dimensions for the RF pin (top view)

Silicon Labs

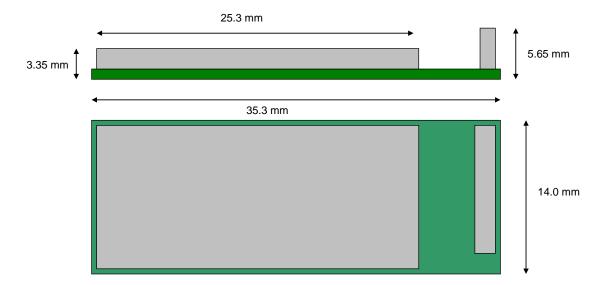

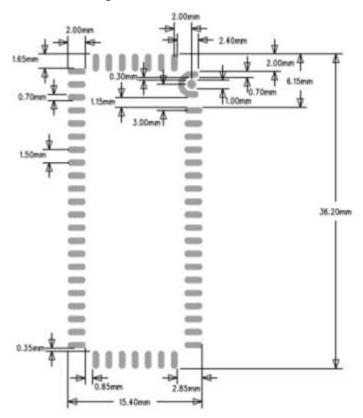

Figure 6: Dimensions of WT41

Figure 7: Recommended land pattern

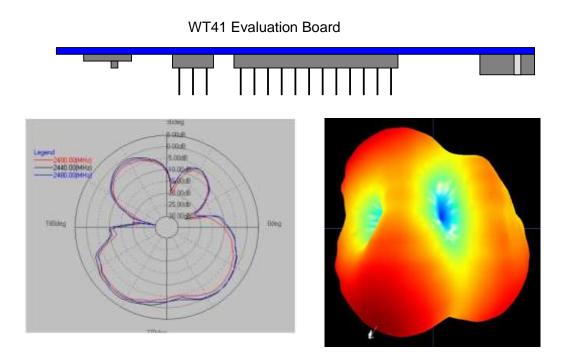

# 5 Layout Guidelines

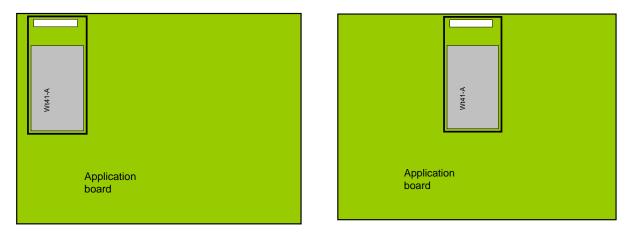

### 5.1 WT41-A

WT41-A should be mounted directly over a solid GND plane. The best performance can be achieved when placing the module to the left corner or to a middle edge of the mother board, as shown in the figure below. Components can be mounted directly under the module and the antenna. The antenna is extremely robust for environment in close proximity to the antenna. Any dielectric material has minor effect on the resonant frequency of the antenna. Metal objects with physical height less than 2 mm can be placed freely anywhere around the module within the area of the mother board without significantly effecting on the radiation characteristics. It is important to place the module to the edge of the mother board and not to place metal objects in front of the antenna.

Figure 8: Recommended positions for WT41-A

Figure 9: Do not place the module so that the GND plane reaches in front of the antenna

### 5.2 WT41-N

### 5.2.1 Layout for WT41-N with u.fl connector close to RF pin

If the trace from the RF pin to u.fl connector is very short there is no need to use impedance controlled trace. Figure 10 shows an example layout where the u.fl connector is placed right next to the RF pin.

Figure 10: Layout of WT41-N with U.FL connector placed next to the RF pin

### 5.2.2 Layout for WT41-N with 50 ohm trace from RF pin to a SMA connector

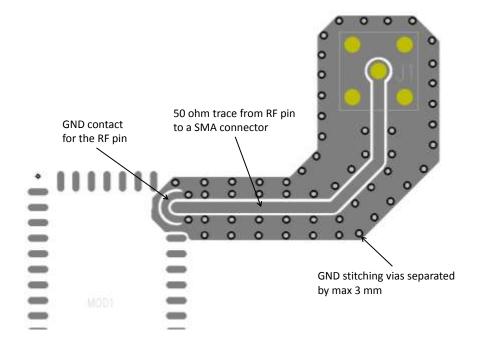

Use 50 ohm transmission line to trace the signal from RF pin to an external RF connector. Figure 11 shows a layout example for WT41-N with an external SMA connector.

Figure 11: Example RF trace for WT41-N

Silicon Labs

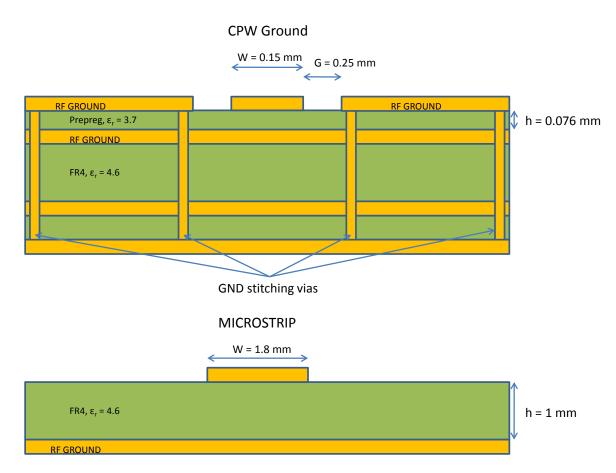

A transmission line impedance calculator, such as TX-Line made by AWR, can be used to approximate the dimensions for the 50 ohm transmission line. Figure 12 shows an example for two different 50 ohm transmission lines.

Figure 12: Example cross section of two different 50 ohm transmission line

# 6 UART Interface

This is a standard UART interface for communicating with other serial devices.WT41 UART interface provides a simple mechanism for communicating with other serial devices using the RS232 protocol.

Four signals are used to implement the UART function. When WT41 is connected to another digital device, UART\_RX and UART\_TX transfer data between the two devices. The remaining two signals, UART\_CTS and UART\_RTS, can be used to implement RS232 hardware flow control where both are active low indicators. All UART connections are implemented using CMOS technology and have signalling levels of 0V and VDD.

UART configuration parameters, such as data rate and packet format, are set using WT41 software.

Note:

In order to communicate with the UART at its maximum data rate using a standard PC, an accelerated serial port adapter card is required for the PC.

| Parameter           | Possible Values   |                       |  |  |

|---------------------|-------------------|-----------------------|--|--|

| Data Rate           | Minimum           | 1200 bits/s (2%Error) |  |  |

|                     |                   | 9600 bits/s (1%Error) |  |  |

|                     | Maximum           | 3M bit/s (1%Error)    |  |  |

| Flow Control        | RTS/CTS or None   |                       |  |  |

| Parity              | None, Odd or Even |                       |  |  |

| Number of Stop Bits | 1 or 2            |                       |  |  |

| Bits per Channel    | 8                 |                       |  |  |

### Table 16: Possible UART Settings

The UART interface is capable of resetting WT41 upon reception of a break signal. A break is identified by a continuous logic low (0V) on the UART\_RX terminal, as shown in Figure 13. If tBRK is longer than the value, defined by PSKEY\_HOST\_IO\_UART\_RESET\_TIMEOUT, (0x1a4), a reset will occur. This feature allows a host to initialise the system to a known state. Also, WT41 can emit a break character that may be used to wake the host.

|         | t <sub>BRK</sub> | 1 |

|---------|------------------|---|

| UART RX | \                |   |

### Figure 13: Break Signal

Table 17 shows a list of commonly used data rates and their associated values for PSKEY\_UART\_BAUD\_RATE (0x204). There is no requirement to use these standard values. Any data rate within the supported range can be set in the PS Key according to the formula in Equation XXX

# PSKEY\_UART\_BAUDRATE

## 0.004096

### Equation 1: Data Rate

| Data Rate (bits/s) | Persistent Store Value | Error | Dec    |

|--------------------|------------------------|-------|--------|

|                    | Hex                    |       |        |

| 1200               | 0x0005                 | 5     | 1.73%  |

| 2400               | 0x000a                 | 10    | 1.73%  |

| 4800               | 0x0014                 | 20    | 1.73%  |

| 9600               | 0x0027                 | 39    | -0.82% |

| 19200              | 0x004f                 | 79    | 0.45%  |

| 38400              | 0x009d                 | 157   | -0.18% |

| 57600              | 0x00ec                 | 236   | 0.03%  |

| 76800              | 0x013b                 | 315   | 0.14%  |

| 115200             | 0x01d8                 | 472   | 0.03%  |

| 230400             | 0x03b0                 | 944   | 0.03%  |

| 460800             | 0x075f                 | 1887  | -0.02% |

| 921600             | 0x0ebf                 | 3775  | 0.00%  |

| 1382400            | 0x161e                 | 5662  | -0.01% |

| 1843200            | 0x1d7e                 | 7550  | 0.00%  |

| 2764800            | 0x2c3d                 | 11325 | 0.00%  |

Table 17: Standard Data Rates

## 6.1 UART Bypass

Figure 14: UART Bypass Architecture

## 6.2 UART Configuration While Reset is Active

The UART interface for WT41 while the chip is being held in reset is tristate. This will allow the user to daisy chain devices onto the physical UART bus. The constraint on this method is that any devices connected to this bus must tristate when WT41 reset is de-asserted and the firmware begins to run.

## 6.3 UART Bypass Mode

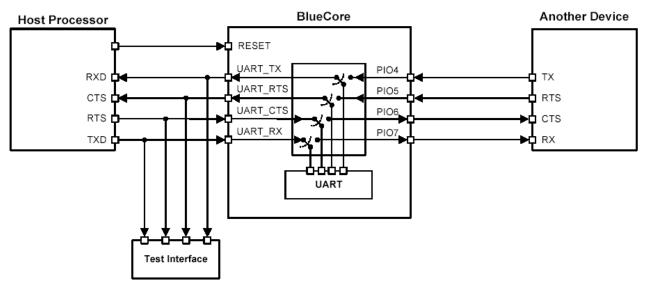

Alternatively, for devices that do not tristate the UART bus, the UART bypass mode on BlueCore4-External can be used. The default state of BlueCore4-External after reset is de-asserted; this is for the host UART bus to be connected to the BlueCore4-External UART, thereby allowing communication to BlueCore4-External via the UART. All UART bypass mode connections are implemented using CMOS technology and have signalling levels of 0V and VDD.

In order to apply the UART bypass mode, a BCCMD command will be issued to BlueCore4-External. Upon this issue, it will switch the bypass to PIO[7:4] as Figure 14 indicates. Once the bypass mode has been invoked, WT41 will enter the Deep Sleep state indefinitely.

In order to re-establish communication with WT41, the chip must be reset so that the default configuration takes effect.

It is important for the host to ensure a clean Bluetooth disconnection of any active links before the bypass mode is invoked. Therefore, it is not possible to have active Bluetooth links while operating the bypass mode.

The current consumption for a device in UART bypass mode is equal to the values quoted for a device in standby mode.

# 7 USB Interface

This is a full speed (12Mbits/s) USB interface for communicating with other compatible digital devices. WT41 acts as a USB peripheral, responding to requests from a master host controller such as a PC.

The USB interface is capable of driving a USB cable directly. No external USB transceiver is required. The device operates as a USB peripheral, responding to requests from a master host controller such as a PC. Both the OHCI and the UHCI standards are supported. The set of USB endpoints implemented can behave as specified in the USB section of the Bluetooth v2.1 + EDR specification or alternatively can appear as a set of endpoints appropriate to USB audio devices such as speakers.

As USB is a master/slave oriented system (in common with other USB peripherals), WT41 only supports USB Slave operation.

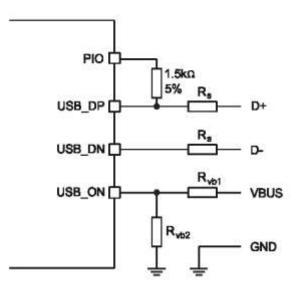

### 7.1 USB Data Connections

The USB data lines emerge as pins USB\_DP and USB\_DN. These terminals are connected to the internal USB I/O buffers of the BlueCore4-External, therefore, have a low output impedance. To match the connection to the characteristic impedance of the USB cable, resistors must be placed in series with USB\_DP/USB\_DN and the cable.

### 7.2 USB Pull-Up resistor

WT41 features an internal USB pull-up resistor. This pulls the USB\_DP pin weakly high when WT41 is ready to enumerate. It signals to the PC that it is a full speed (12Mbits/s) USB device.

The USB internal pull-up is implemented as a current source, and is compliant with section 7.1.5 of the USB specification v1.2. The internal pull-up pulls USB\_DP high to at least 2.8V when loaded with a 15k 5% pull-down resistor (in the hub/host) when VDD\_PADS = 3.1V. This presents a Thevenin resistance to the host of at least 900. Alternatively, an external 1.5k pull-up resistor can be placed between a PIO line and D+ on the USB cable. The firmware must be alerted to which mode is used by setting PSKEY\_USB\_PIO\_PULLUP appropriately. The default setting uses the internal pull-up resistor.

## 7.3 USB Power Supply

The USB specification dictates that the minimum output high voltage for USB data lines is 2.8V. To safely meet the USB specification, the voltage on the VDD supply terminal must be an absolute minimum of 3.1V. Bluegiga recommends 3.3V for optimal USB signal quality.

### 7.4 Self-Powered Mode

In self-powered mode, the circuit is powered from its own power supply and not from the VBUS (5V) line of the USB cable. It draws only a small leakage current (below 0.5mA) from VBUS on the USB cable. This is the easier mode for which to design, as the design is not limited by the power that can be drawn from the USB hub or root port. However, it requires that VBUS be connected to WT41 via a resistor network (Rvb1 and Rvb2), so WT41 can detect when VBUS is powered up. BlueCore4-External will not pull USB\_DP high when VBUS is off.

Self-powered USB designs (powered from a battery or PSU) must ensure that a PIO line is allocated for USB pullup purposes. A 1.5k 5% pull-up resistor between USB\_DP and the selected PIO line should be fitted to the design. Failure to fit this resistor may result in the design failing to be USB compliant in self-powered mode. The internal pull-up in BlueCore is only suitable for bus-powered USB devices, e.g., dongles.

Figure 15: USB Connections for Self-Powered Mode

The terminal marked USB\_ON can be any free PIO pin. The PIO pin selected must be registered by setting PSKEY\_USB\_PIO\_VBUS to the corresponding pin number.

| Identifier       | Value      | Function                        |

|------------------|------------|---------------------------------|

| R <sub>s</sub>   | 27 nominal | Impedance matching to USB cable |

| R <sub>vb1</sub> | 22k 5%     | VBUS ON sense divider           |

| R <sub>vb2</sub> | 47k 5%     | VBUS ON sense divider           |

### Figure 16: USB Interface Component Values

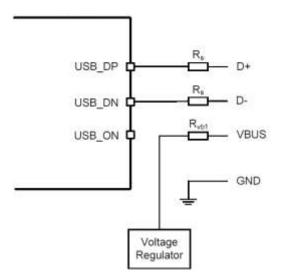

## 7.5 Bus-Powered Mode

In bus-powered mode, the application circuit draws its current from the 5V VBUS supply on the USB cable. WT41 negotiates with the PC during the USB enumeration stage about how much current it is allowed to consume. On power-up the device must not draw more than 100 mA but after being configured it can draw up to 500 mA.

For WT41, the USB power descriptor should be altered to reflect the amount of power required. This is accomplished by setting PSKEY\_USB\_MAX\_POWER (0x2c6). This is higher than for a Class 2 application due to the extra current drawn by the Transmit RF PA. By default for WT41 the setting is 300 mA.

When selecting a regulator, be aware that VBUS may go as low as 4.4V. The inrush current (when charging reservoir and supply decoupling capacitors) is limited by the USB specification. See the USB Specification. Some applications may require soft start circuitry to limit inrush current if more than 10uF is present between VBUS and GND. The 5V VBUS line emerging from a PC is often electrically noisy. As well as regulation down to 3.3V and 1.8V, applications should include careful filtering of the 5V line to attenuate noise that is above the voltage regulator bandwidth. Excessive noise on WT41 supply pins will result in reduced receiver sensitivity and a distorted RF transmit signal.

Figure 17: USB Connections for Bus-Powered Mode

## 7.6 USB Suspend Current

All USB devices must permit the USB controller to place them in a USB suspend mode. While in USB Suspend, bus-powered devices must not draw more than 2.5mA from USB VBUS (self-powered devices may draw more than 2.5mA from their own supply). This current draw requirement prevents operation of the radio by bus-powered devices during USB Suspend.

When computing suspend current, the current from VBUS through the bus pull-up and pull-down resistors must be included. The pull-up resistor at the device is 1.5 k. (nominal). The pull-down resistor at the hub is 14.25k. to 24.80k. The pull-up voltage is nominally 3.3V, which means that holding one of the signal lines high takes approximately 200uA, leaving only 2.3mA available from a 2.5mA budget. Ensure that external LEDs and/or amplifiers can be turned off by BlueCore4-External. The entire circuit must be able to enter the suspend mode.

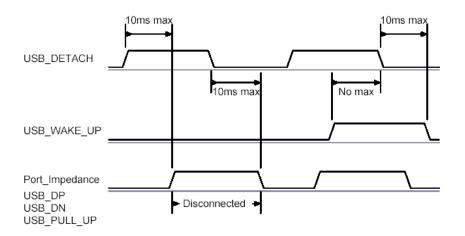

## 7.7 USB Detach and Wake-Up Signaling

WT41 can provide out-of-band signaling to a host controller by using the control lines called USB\_DETACH and USB\_WAKE\_UP. These are outside the USB specification (no wires exist for them inside the USB cable), but can be useful when embedding WT41 into a circuit where no external USB is visible to the user. Both control lines are shared with PIO pins and can be assigned to any PIO pin by setting PSKEY\_USB\_PIO\_DETACH and PSKEY\_USB\_PIO\_WAKEUP to the selected PIO number.

USB\_DETACH is an input which, when asserted high, causes WT41 to put USB\_DN and USB\_DP in high impedance state and turns off the pull-up resistor on DP. This detaches the device from the bus and is logically equivalent to unplugging the device. When USB\_DETACH is taken low, WT41 will connect back to USB and await enumeration by the USB host.

USB\_WAKE\_UP is an active high output (used only when USB\_DETACH is active) to wake up the host and allow USB communication to recommence. It replaces the function of the software USB WAKE\_UP message (which runs over the USB cable) and cannot be sent while BlueCore4-External is effectively disconnected from the bus.

Figure 18: USB\_Detach and USB\_Wake\_Up Signals

### 7.8 USB Driver

A USB Bluetooth device driver is required to provide a software interface between BlueCore4-External and Bluetooth software running on the host computer. Please, contact <u>support@bluegiga.com</u> for suitable drivers.

## 7.9 USB v2.0 Compliance and Compatibility

Although WT41 meets the USB specification, CSR cannot guarantee that an application circuit designed around the module is USB compliant. The choice of application circuit, component choice and PCB layout all affect USB signal quality and electrical characteristics. The information in this document is intended as a guide and should be read in association with the USB specification, with particular attention being given to Chapter 7. Independent USB qualification must be sought before an application is deemed USB compliant and can bear the USB logo. Such qualification can be obtained from a USB plugfest or from an independent USB test house.

Terminals USB\_DP and USB\_DN adhere to the USB Specification v2.0 (Chapter 7) electrical requirements.

BlueCore4-External is compatible with USB v2.0 host controllers; under these circumstances the two ends agree the mutually acceptable rate of 12Mbits/s according to the USB v2.0 specification.

# 8 Serial Peripheral Interface (SPI)

The SPI port can be used for system debugging. It can also be used for programming the Flash memory and setting the PSKEY configurations. WT41 uses 16-bit data and 16-bit address serial peripheral interface, where transactions may occur when the internal processor is running or is stopped. SPI interface is connected using the MOSI, MISO, CSB and CLK pins. Please, contact <a href="mailto:support@bluegiga.com">support@bluegiga.com</a> for detailed information about the instruction cycle.

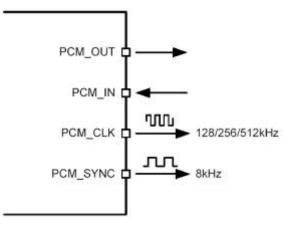

# 9 PCM Codec Interface

PCM is a standard method used to digitize audio (particularly voice) for transmission over digital communication channels. Through its PCM interface, WT41 has hardware support for continual transmission and reception of PCM data, thus reducing processor overhead for wireless headset applications. WT41 offers a bidirectional digital audio interface that routes directly into the baseband layer of the on-chip firmware. It does not pass through the HCI protocol layer.

Hardware on WT41 allows the data to be sent to and received from a SCO connection. Up to three SCO connections can be supported by the PCM interface at any one time.

WT41 can operate as the PCM interface master generating an output clock of 128, 256 or 512kHz. When configured as PCM interface slave, it can operate with an input clock up to 2048kHz. WT41 is compatible with a variety of clock formats, including Long Frame Sync, Short Frame Sync and GCI timing environments.

It supports 13-bit or 16-bit linear, 8-bit µ-law or A-law companded sample formats at 8ksamples/s and can receive and transmit on any selection of three of the first four slots following PCM\_SYNC. The PCM configuration options are enabled by setting PSKEY\_PCM\_CONFIG32.

WT41 interfaces directly to PCM audio devices.

NOTE: Analog audio lines are very sensitive to RF disturbance. Use good layout practices to ensure noise less audio. Make sure that the return path for the audio signals follows the forward current all the way as close as possible and use fully differential signals when possible. Do not compromise audio routing.

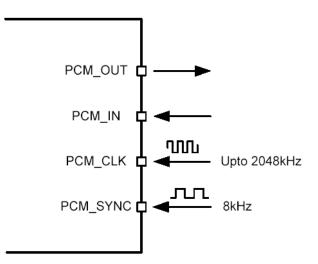

### 9.1 PCM Interface Master/Slave

When configured as the master of the PCM interface, WT41 generates PCM\_CLK and PCM\_SYNC.

### Figure 19: PCM Interface Master

When configured as the Slave of the PCM interface, WT41 accepts PCM\_CLK rates up to 2048kHz.

Figure 20: PCM Interface Slave

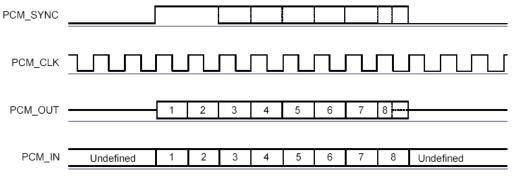

## 9.2 Long Frame Sync

Long Frame Sync is the name given to a clocking format that controls the transfer of PCM data words or samples. In Long Frame Sync, the rising edge of PCM\_SYNC indicates the start of the PCM word. When WT41 is configured as PCM master, generating PCM\_SYNC and PCM\_CLK, then PCM\_SYNC is 8-bits long. When WT41 is configured as PCM Slave, PCM\_SYNC may be from two consecutive falling edges of PCM\_CLK to half the PCM\_SYNC rate, i.e., 62.5s long.

Figure 21: Long Frame Sync (Shown with 8-bit Companded Sample)

WT41 samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT may be configured to be high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

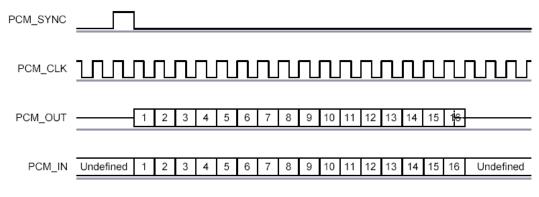

## 9.3 Short Frame Sync

In Short Frame Sync, the falling edge of PCM\_SYNC indicates the start of the PCM word. PCM\_SYNC is always one clock cycle long.

Figure 22: Short Frame Sync (Shown with 16-bit Sample)

As with Long Frame Sync, WT41 samples PCM\_IN on the falling edge of PCM\_CLK and transmits PCM\_OUT on the rising edge. PCM\_OUT may be configured to be high impedance on the falling edge of PCM\_CLK in the LSB position or on the rising edge.

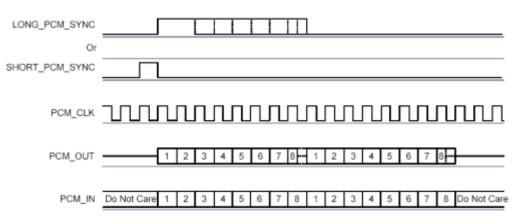

### 9.4 Multi-slot Operation

More than one SCO connection over the PCM interface is supported using multiple slots. Up to three SCO connections can be carried over any of the first four slots.

Figure 23: Multi-slot Operation with Two Slots and 8-bit Companded Samples

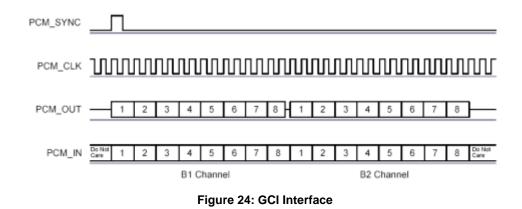

## 9.5 GCI Interface

WT41 is compatible with the GCI, a standard synchronous 2B+D ISDN timing interface. The two 64kbits/s B channels can be accessed when this mode is configured.

The start of frame is indicated by the rising edge of PCM\_SYNC and runs at 8kHz. With WT41 in Slave mode, the frequency of PCM\_CLK can be up to 4.096MHz.

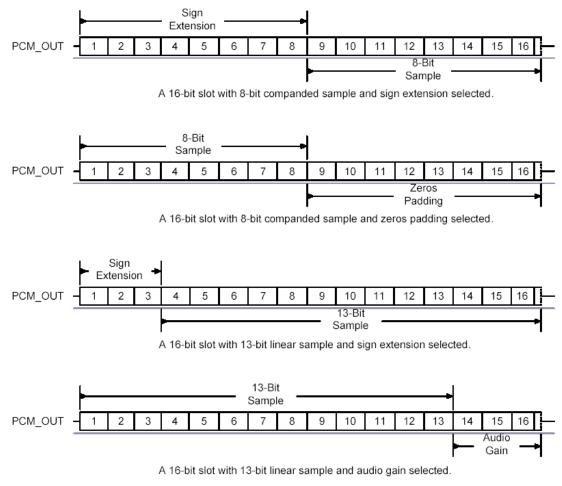

## 9.6 Slots and Sample Formats

WT41 can receive and transmit on any selection of the first four slots following each sync pulse. Slot durations can be either 8 or 16 clock cycles. Durations of 8 clock cycles may only be used with 8-bit sample formats. Durations of 16 clocks may be used with 8-bit, 13-bit or 16-bit sample formats.

WT41 supports 13-bit linear, 16-bit linear and 8-bit -law or A-law sample formats. The sample rate is 8ksamples/s. The bit order may be little or big endian. When 16-bit slots are used, the 3 or 8 unused bits in each slot may be filled with sign extension, padded with zeros or a programmable 3-bit audio attenuation compatible with some Motorola codecs.

Figure 25: 16-bit Slot Length and Sample Formats

## 9.7 Additional Features

WT41 has a mute facility that forces PCM\_OUT to be 0. In master mode, PCM\_SYNC may also be forced to 0 while keeping PCM\_CLK running which some codecs use to control power down.

# 9.8 PCM\_CLK and PCM\_SYNC Generation

WT41 has two methods of generating PCM\_CLK and PCM\_SYNC in master mode. The first is generating these signals by DDS from BlueCore4-External internal 4MHz clock. Using this mode limits PCM\_CLK to 128, 256 or 512kHz and PCM\_SYNC to 8kHz. The second is generating PCM\_CLK and PCM\_SYNC by DDS from an internal 48MHz clock (which allows a greater range of frequencies to be generated with low jitter but consumes more power). This second method is selected by setting bit 48M\_PCM\_CLK\_GEN\_EN in PSKEY\_PCM\_CONFIG32. When in this mode and with long frame sync, the length of PCM\_SYNC can be either 8 or 16 cycles of PCM\_CLK, determined by LONG\_LENGTH\_SYNC\_EN in PSKEY\_PCM\_CONFIG32.

The Equation XXX describes PCM\_CLK frequency when being generated using the internal 48MHz clock:

$$f = \frac{CNT\_RATE}{CNT\_LIMIT} \times 24MHz$$

### Equation 2: PCM\_CLK Frequency When Being Generated Using the Internal 48MHz Clock

The frequency of PCM\_SYNC relative to PCM\_CLK can be set using Equation XXX:

$$f = \frac{PCM_CLK}{SYNC_LIMIT \times 8}$$

## Equation 3: PCM\_SYNC Frequency Relative to PCM\_CLK

CNT\_RATE, CNT\_LIMIT and SYNC\_LIMIT are set using PSKEY\_PCM\_LOW\_JITTER\_CONFIG. As an example, to generate PCM\_CLK at 512kHz with PCM\_SYNC at 8kHz, set PSKEY\_PCM\_LOW\_JITTER\_CONFIG to 0x08080177.

## 9.9 PCM Configuration

The PCM configuration is set using two PS Keys, PSKEY\_PCM\_CONFIG32 detailed in Table 18 and PSKEY\_PCM\_LOW\_JITTER\_CONFIG in Table 19. The default for PSKEY\_PCM\_CONFIG32 is 0x00800000, i.e., first slot following sync is active, 13-bit linear voice format, long frame sync and interface master generating 256kHz PCM\_CLK from 4MHz internal clock with no tri-state of PCM\_OUT.

| Name                          | Bit position | Description                                                                                                                                                                                                                                                             |  |  |  |

|-------------------------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| -                             | 0            | Set to 0                                                                                                                                                                                                                                                                |  |  |  |

| SLAVE MODE EN                 | 1            | 0 selects Master mode with internal generation of PCM_CLK and<br>PCM_SYNC. 1 selects Slave mode requiring externally generated<br>PCM_CLK and PCM_SYNC. This should be set to 1 if<br>48M_PCM_CLK_GEN_EN (bit 11) is set.                                               |  |  |  |

| SHORT SYNC EN                 | 2            | 0 selects long frame sync (rising edge indicates start of frame), 1 selects short frame sync (falling edge indicates start of frame).                                                                                                                                   |  |  |  |

| -                             | 3            | Set to 0                                                                                                                                                                                                                                                                |  |  |  |

| SIGN EXTENDED<br>EN           | 4            | 0 selects padding of 8 or 13-bit voice sample into a 16- bit slot by inserting extra LSBs, 1 selects sign extension. When padding is selected with 3-bit voice sample, the 3 padding bits are the audio gair setting; with 8-bit samples the 8 padding bits are zeroes. |  |  |  |

| LSB FIRST EN                  | 5            | 0 transmits and receives voice samples MSB first, 1 uses LSB first.                                                                                                                                                                                                     |  |  |  |

| TX TRISTATE EN                | 6            | 0 drives PCM_OUT continuously, 1 tri-states PCM_OUT immediately<br>after the falling edge of PCM_CLK in the last bit of an active slot,<br>assuming the next slot is not active.                                                                                        |  |  |  |

| TX TRISTATE<br>RISING EDGE EN | 7            | 0 tristates PCM_OUT immediately after the falling edge of PCM_CLK<br>in the last bit of an active slot, assuming the next slot is also not active<br>1 tristates PCM_OUT after the rising edge of PCM_CLK.                                                              |  |  |  |

| SYNC SUPPRESS<br>EN           | 8            | 0 enables PCM_SYNC output when master, 1 suppresses PCM_SYNC<br>whilst keeping PCM_CLK running. Some CODECS utilize this to enter<br>a low power state.                                                                                                                 |  |  |  |

| GCI MODE EN                   | 9            | 1 enables GCI mode.                                                                                                                                                                                                                                                     |  |  |  |

| MUTE EN                       | 10           | 1 forces PCM_OUT to 0.                                                                                                                                                                                                                                                  |  |  |  |

| 48M PCM CLK GEN<br>EN         | 11           | 0 sets PCM_CLK and PCM_SYNC generation via DDS from internal 4<br>MHz clock, as for BlueCore4-External. 1 sets PCM_CLK and<br>PCM_SYNC generation via DDS from internal 48 MHz clock.                                                                                   |  |  |  |

| LONG LENGTH<br>SYNC EN        | 12           | 0 sets PCM_SYNC length to 8 PCM_CLK cycles and 1 sets length to<br>16 PCM_CLK cycles. Only applies for long frame sync and with<br>48M_PCM_CLK_GEN_EN set to 1.                                                                                                         |  |  |  |

| -                             | [20:16]      | Set to 0b00000.                                                                                                                                                                                                                                                         |  |  |  |

| MASTER CLK RATE               | [22:21]      | Selects 128 (0b01), 256 (0b00), 512 (0b10) kHz PCM_CLK frequency when master and 48M_PCM_CLK_GEN_EN (bit 11) is low.                                                                                                                                                    |  |  |  |

| ACTIVE SLOT                   | [26:23]      | Default is 0001. Ignored by firmaware                                                                                                                                                                                                                                   |  |  |  |

| SAMPLE_FORMAT                 | [28:27]      | Selects between 13 (0b00), 16 (0b01), 8 (0b10) bit sample with 16 cycle slot duration 8 (0b11) bit sample 8 cycle slot duration.                                                                                                                                        |  |  |  |

## Table 18: PSKEY\_PCM\_CONFIG32 description

| Name       | Bit position | Description                                 |

|------------|--------------|---------------------------------------------|

| CNT LIMIT  | [12:0]       | Sets PCM_CLK counter limit                  |

| CNT RATE   | [23:16]      | Sets PCM_CLK count rate.                    |

| SYNC LIMIT | [31:24]      | Sets PCM_SYNC division relative to PCM_CLK. |

## Table 19: PSKEY\_PCM\_LOW\_JITTER\_CONFIG Description

# **10 I/O Parallel Ports**

Six lines of programmable bidirectional input/outputs (I/O) are provided. All the PIO lines are power from VDD.

PIO lines can be configured through software to have either weak or strong pull-ups or pull-downs. All PIO lines are configured as inputs with weak pull-downs at reset. Any of the PIO lines can be configured as interrupt request lines or as wake-up lines from sleep modes.

WT41 has a general purpose analogue interface pin AIO[1]. This is used to access internal circuitry and control signals. It may be configured to provide additional functionality.

Auxiliary functions available via AIO[1] include an 8-bit ADC and an 8-bit DAC. Typically the ADC is used for battery voltage measurement. Signals selectable at this pin include the band gap reference voltage and a variety of clock signals: 48, 24, 16, 8MHz and the XTAL clock frequency. When used with analogue signals, the voltage range is constrained by the analogue supply voltage internally to the module (1.8V). When configured to drive out digital level signals (e.g., clocks), the output voltage level is determined by VDD.

## 10.1 PIO Defaults

Bluegiga cannot guarantee that these terminal functions remain the same. Refer to the software release note for the implementation of these PIO lines, as they are firmware build-specific.

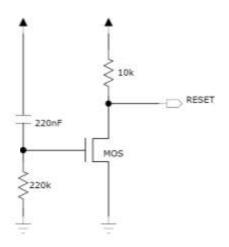

# 11 Reset

WT41 may be reset from several sources: RESET pin, power on reset, a UART break character or via software configured watchdog timer. The RESET pin is an active low reset and is internally filtered using the internal low frequency clock oscillator. A reset will be performed between 1.5 and 4.0ms following RESETB being active. It is recommended that RESET be applied for a period greater than 5ms.

The power on reset occurs when the VDD\_CORE supply internally to the module falls below typically 1.5V and is released when VDD\_CORE rises above typically 1.6V. At reset the digital I/O pins are set to inputs for bidirectional pins and outputs are tri-state.

The reset should be held active at power up until all the supply voltages have stabilized to ensure correct operation of the internal flash memory. Following figure shows an example of a simple power up reset circuit. Time constant of the RC circuitry is set so that the supply voltage is safely stabilized before the reset deactivates.

Figure 26: Example of a simple power on reset circuit.

## 11.1 Pin States on Reset

| PIN NAME | STATE                                |

|----------|--------------------------------------|

| PIO[7:2] | Input with weak pull-down            |

| PCM_OUT  | Tri-staed with weak pull-down        |

| PCM_IN   | Input with weak pull-down            |

| PCM_SYNC | Input with weak pull-down            |

| PCM_CLK  | Input with weak pull-down            |

| UART_TX  | Output tristated with weak pull-up   |

| UART_RX  | Input with weak pull-down            |

| UART_RTS | Output tristated with weak pull-up   |

| UART_CTS | Input with weak pull-down            |

| USB+     | Input with weak pull-down            |

| USB-     | Input with weak pull-down            |

| SPI_CSB  | Input with weak pull-down            |

| SPI_CLK  | Input with weak pull-down            |

| SPI_MOSI | Input with weak pull-down            |

| SPI_MISO | Output tristated with weak pull-down |

| AIO[1]   | Output, driving low                  |

Table 20: Pin States on Reset

# **12 Certifications**

WT41 is compliant to the following specifications.

## 12.1 Bluetooth

WT41 module is *Bluetooth* qualified and listed as a controller subsystem and it is Bluetooth compliant to the following profiles of the core spec version 2.1/2.1+EDR.

- Baseband

- HCI

- Link Manager

- Radio

## 12.2 FCC

This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions:

(1) this device may not cause harmful interference, and

(2) this device must accept any interference received, including interference that may cause undesired operation.

## FCC RF Radiation Exposure Statement:

This equipment complies with FCC radiation exposure limits set forth for an uncontrolled environment. End users must follow the specific operating instructions for satisfying RF exposure compliance. This transmitter meets both portable and mobile limits as demonstrated in the RF Exposure Analysis and should not be used closer than 22 mm from a human body in portable configuration. This transmitter must not be co-located or operating in conjunction with any other antenna or transmitter except in accordance with FCC multi-transmitter product procedures .

### **OEM Responsibilities to comply with FCC Regulations**

The WT41-A/N Module has been certified for integration into products only by OEM integrators under the following conditions:

- The antenna(s) must be installed such that a minimum separation distance of 22 mm is maintained between the radiator (antenna) and all persons at all times.

- The transmitter module must not be co-located or operating in conjunction with any other antenna or transmitter except in accordance with FCC multi-transmitter product procedures.

As long as the two conditions above are met, further transmitter testing will not be required. However, the OEM integrator is still responsible for testing their end-product for any additional compliance requirements required with this module installed (for example, digital device emissions, PC peripheral requirements, etc.).

**IMPORTANT NOTE:** In the event that these conditions can not be met (for certain configurations or colocation with another transmitter), then the FCC and Industry Canada authorizations are no longer considered valid and the FCC ID can not be used on the final product. In these circumstances, the OEM integrator will be responsible for re-evaluating the end product (including the transmitter) and obtaining a separate FCC and Industry Canada authorization.

### End Product Labeling

The WT41-A/N Module is labeled with its own FCC ID. If the IC Certification Number is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. In that case, the final end product must be labeled in a visible area with the following:

#### "Contains Transmitter Module FCC ID: QOQWT41"

or

### "Contains FCC ID: QOQWT41"

The OEM of the WT41-A/N Module must only use the approved antenna(s) listed in table 21, which have been certified with this module. The OEM integrator has to be aware not to provide information to the end user regarding how to install or remove this RF module or change RF related parameters in the user manual of the end product.

## 12.3 IC (Industry Canada)

### IC Statements:

This device complies with Industry Canada licence-exempt RSS standard(s). Operation is subject to the following two conditions: (1) this device may not cause interference, and (2) this device must accept any interference, including interference that may cause undesired operation of the device.

Under Industry Canada regulations, this radio transmitter may only operate using an antenna of a type and maximum (or lesser) gain approved for the transmitter by Industry Canada. To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that necessary for successful communication.

#### If detachable antennas are used:

This radio transmitter (identify the device by certification number, or model number ifCategory II) has been approved by Industry Canada to operate with the antenna types listed below with the maximum permissible gain and required antenna impedance for each antenna type indicated. Antenna types not included in this list, having a gain greater than the maximum gain indicated for that type, are strictly prohibited for use with this device. See table 21 for the approved antennas for WT41-N

#### End Product Labeling

The WT41-A/N Module is labeled with its own IC Certification Number. If the IC Certification Number is not visible when the module is installed inside another device, then the outside of the device into which the module is installed must also display a label referring to the enclosed module. In that case, the final end product must be labeled in a visible area with the following:

#### "Contains Transmitter Module IC: 5123A-BGTWT41"

### "Contains IC: 5123A-BGTWT41"

To comply with Industry Canada RF radiation exposure limits for general population, the antenna(s) used for this transmitter must be installed such that a minimum separation distance of 20 cm is maintained between the radiator (antenna) and all persons at all times and must not be co-located or operating in conjunction with any other antenna or transmitter.

## 12.3.1 IC

## Déclaration de conformité IC :

Ce matériel respecte les standards RSS exempt de licence d'Industrie Canada. Son utilisation est soumise aux deux conditions suivantes :

- (1) l'appareil ne doit causer aucune interférence, et

- (2) l'appareil doit accepter toute interférence, quelle qu'elle soit, y compris les interférences

susceptibles d'entraîner un fonctionnement non requis de l'appareil.

Selon la réglementation d'Industrie Canada, ce radio-transmetteur ne peut utiliser qu'un seul type d'antenne et ne doit pas dépasser la limite de gain autorisée par Industrie Canada pour les transmetteurs. Afin de réduire les interférences potentielles avec d'autres utilisateurs, le type d'antenne et son gain devront être définis de telle façon que la puissance isotrope rayonnante équivalente (EIRP) soit juste suffisante pour permettre une bonne communication.

### Lors de l'utilisation d'antennes amovibles :

Ce radio-transmetteur (identifié par un numéro certifié ou un numéro de modèle dans le cas de la catégorie II) a été approuvé par Industrie Canada pour fonctionner avec les antennes référencées ci-dessous dans la limite de gain acceptable et l'impédance requise pour chaque type d'antenne cité. Les antennes non référencées possédant un gain supérieur au gain maximum autorisé pour le type d'antenne auquel elles appartiennent sont strictement interdites d'utilisation avec ce matériel. Veuillez vous référer au tableau 21 concernant les antennes approuvées pour les WT41-N.

## Les responsabilités de l'intégrateur afin de satisfaire aux réglementations de la FCC et d'Industrie Canada :

Les modules WT41-A/N ont été certifiés pour entrer dans la fabrication de produits exclusivement réalisés par des intégrateurs dans les conditions suivantes :

• L'antenne (ou les antennes) doit être installée de façon à maintenir à tout instant une distance minimum de 20cm entre la source de radiation (l'antenne) et toute personne physique.

Silicon Labs

or

• Le module transmetteur ne doit pas être installé ou utilisé en concomitance avec une autre antenne ou un autre transmetteur.

Tant que ces deux conditions sont réunies, il n'est pas nécessaire de procéder à des tests supplémentaires sur le transmetteur. Cependant, l'intégrateur est responsable des tests effectués sur le produit final afin de se mettre en conformité avec d'éventuelles exigences complémentaires lorsque le module est installé (exemple : émissions provenant d'appareils numériques, exigences vis-à-vis de périphériques informatiques, etc.) ;

**IMPORTANT :** Dans le cas où ces conditions ne peuvent être satisfaites (pour certaines configurations ou installation avec un autre transmetteur), les autorisations fournies par la FCC et Industrie Canada ne sont plus valables et les numéros d'identification de la FCC et de certification d'Industrie Canada ne peuvent servir pour le produit final. Dans ces circonstances, il incombera à l'intégrateur de faire réévaluer le produit final (comprenant le transmetteur) et d'obtenir une autorisation séparée de la part de la FCC et d'Industrie Canada.

### Etiquetage du produit final

Chaque module WT41-A/N possède sa propre identification FCC et son propre numéro de certification IC. Si l'identification FCC et le numéro de certification IC ne sont pas visibles lorsqu'un module est installé à l'intérieur d'un autre appareil, alors l'appareil en question devra lui aussi présenter une étiquette faisant référence au module inclus. Dans ce cas, le produit final doit comporter une étiquette placée de façon visible affichant les mentions suivantes :

### « Contient un module transmetteur certifié FCC QOQWT41 »

#### « Contient un module transmetteur certifié IC 5123A-BGTWT41 »

ou

« Inclut la certification FCC QOQWT41 »

#### « Inclut la certification IC 5123A-BGTWT41 »

L'intégrateur du module WT41-A/N ne doit utiliser que les antennes répertoriées dans le tableau 21 certifiées pour ce module. L'intégrateur est tenu de ne fournir aucune information à l'utilisateur final autorisant ce dernier à installer ou retirer le module RF, ou bien changer les paramètres RF du module, dans le manuel d'utilisation du produit final.

Afin de se conformer aux limites de radiation imposées par la FCC et Industry Canada, l'antenne (ou les antennes) utilisée pour ce transmetteur doit être installée de telle sorte à maintenir une distance

minimum de 20cm à tout instant entre la source de radiation (l'antenne) et les personnes physiques. En outre, cette antenne ne devra en aucun cas être installée ou utilisée en concomitance avec une autre antenne ou un autre transmetteur.

## 12.4CE

WT41 meets the requirements of the standards below and hence fulfills the requirements of EMC Directive 89/336/EEC as amended by Directives 92/31/EEC and 93/68/EEC within CE marking requirement. The official DoC is available at <u>www.bluegiga.com</u>

## 12.5 Japan

WT41-E has modular certification with certification number R 209-J00047

## 12.6 Qualified Antenna Types for WT41-N

This device has been designed to operate with the antennas listed below, and having a maximum gain of 2.3 dBi. Antennas not included in this list or having a gain greater than 2.3 dBi are strictly prohibited for use with this device. The required antenna impedance is 50 ohms.

| Qualified Antenna Types for WT41-N |              |  |  |  |

|------------------------------------|--------------|--|--|--|

| Antenna Type                       | Maximum Gain |  |  |  |

| Dipole                             | 2.3 dBi      |  |  |  |

| Monopole chip antenna              | 3 dBi        |  |  |  |

Table 21: Qualified Antenna Types for WT41-N

To reduce potential radio interference to other users, the antenna type and its gain should be so chosen that the equivalent isotropically radiated power (e.i.r.p.) is not more than that permitted for successful communication. Using an antenna of a different type and/or or higher gain than listed will require additional testing for FCC, CE and IC. Please, contact <a href="mailto:support@bluegiga.com">support@bluegiga.com</a> for more information.

Any antenna of the same type and the same or less gain can be used without additional application to FCC. Table 22 lists approved antennas for WT41. Any approved antenna listed in table 22 can be used directly with WT41 without any additional approval. Any antenna not listed in table 22 can be used with WT41-N as long as detailed information from that particular antenna is provided to Bluegiga for approval. Specification of each antenna used with WT41-N will be filed by Bluegiga. Please, contact <a href="mailto:support@bluegiga.com">support@bluegiga.com</a> for more information.

| Approved antennas for WT41-N |              |                                         |             |                             |            |  |  |  |  |

|------------------------------|--------------|-----------------------------------------|-------------|-----------------------------|------------|--|--|--|--|

| Antenna                      | Antenna part | Specification given by the manufacturer |             | Performance measured by BGT |            |  |  |  |  |

| manufacturer                 | number       | Gain                                    | Efficiency  | Gain                        | Efficiency |  |  |  |  |

| Pulse                        | W1030        | 2                                       | NA          | 1                           | 7080%      |  |  |  |  |

| Linx                         |              |                                         |             |                             |            |  |  |  |  |

| Technologies                 | ANT-2.4-CW-  |                                         | <b>N</b> 14 | 4.0                         |            |  |  |  |  |

| Inc                          | CT-SMA       | NA                                      | NA          | 1.3                         | 77 %       |  |  |  |  |

|                              | CAR-ATR-187- |                                         |             |                             |            |  |  |  |  |

| Litecon                      | 001          | 2                                       | NA          | 0.8                         | 6070%      |  |  |  |  |

Table 22: Approved Antennas For WT41-N

## 12.7 Moisture Sensitivity Level (MSL)

Moisture sensitivity level (MSL) of this product is 3. For the handling instructions please refer to JEDEC J-STD-020 and JEDEC J-STD-033.

If baking is required, devices may be baked for 12 hours at 125°C +/-5°C for high temperature device containers.

#### Disclaimer

Silicon Laboratories intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Laboratories products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Laboratories reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Laboratories shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Laboratories and "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

#### **Trademark Information**

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga Logo®, Clockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress® and others are trademarks or registered trademarks of Silicon Laboratories Inc. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA

## http://www.silabs.com