# AN928.1：EFR32 布局设计指南

本应用说明旨在帮助用户利用能够实现优良 RF 性能的设计实践，设计 EFR32 无线 Gecko 产品组合的 PCB。

2.4 GHz 匹配原则载于应用说明 [AN930.1：EFR32 系列 1 2.4 GHz 匹配指南](#)，1 GHz 以下部分的匹配流程在 [AN923：EFR32 1 GHz 以下匹配指南](#)中讨论。以下应用说明详细介绍了与 MCU 相关的主题：[AN0918.1：MCU 系列 0 至 EFM32GG1x/TG11 兼容性和迁移指南](#)，[AN0948：电源配置和 DC-DC](#) 以及 [AN0955：CRYPTO](#)。

Silicon Labs MCU 和无线入门套件以及 Simplicity Studio 提供强大的开发和调试环境。为利用自定义硬件的功能和特性，Silicon Labs 推荐在自定义硬件设计中包含调试和编程接口连接器。有关包含这些连接器接口的详细信息和优点在 [AN958：自定义设计的调试和编程接口](#)中有详细阐述。

EFR32 内部直流转换器的电源配置和合理用法载于 [AN0948：电源配置和 DC-DC](#)。RF 性能很大程度上依赖于 PCB 布局以及匹配网络的设计。为实现最佳性能，Silicon Labs 建议使用下列部分所述的 PCB 布局设计指南。

## 内容要点

- 提供参考示意图和 PCB 布局

- 列出并描述所有主要设计原则

- 提供所有设计原则的摘要对照表

## 1. 使用 EFR32 系列 1 无线 MCU 的设计建议

- 已使用 Silicon Labs 提供的参考设计完成广泛测试。建议设计者按原样使用参考设计，因为其能够尽可能减小寄生现象导致或不良元件布置和 PCB 排线产生的失谐作用。EFR32 参考设计文件位于 Simplicity Studio 的“套件文档”选项卡下。

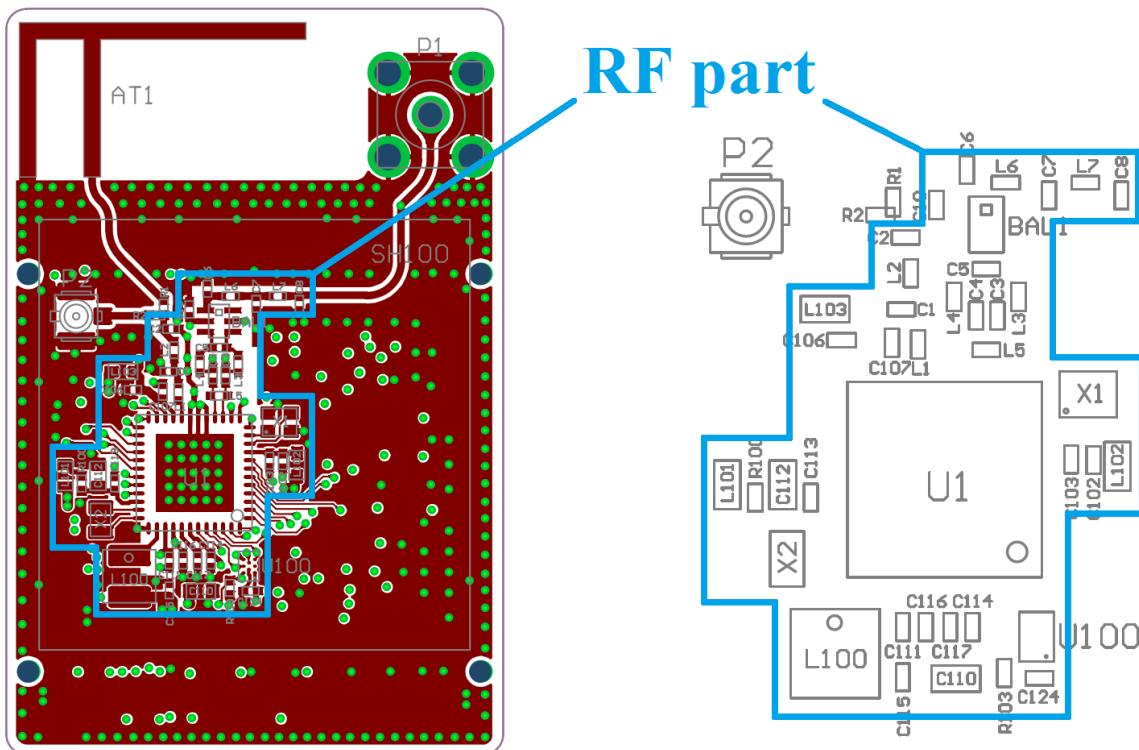

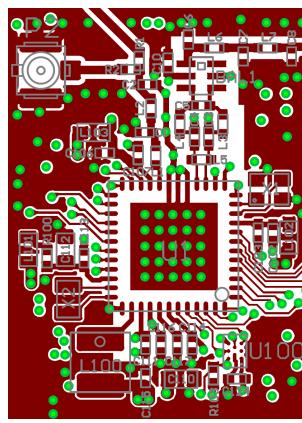

- 设计的紧凑型 RF 部分（不包括 50 Ω 单端天线）以蓝框圈出，强烈建议使用圈出的 RF 布局，以避免出现任何可能的失谐作用。下图显示了设计中圈出的紧凑型 RF 部分。

Figure 1.1. 无线电板的顶层（左侧）和 RF 部分的组装图（右侧）

- MCU VDD 滤波电容的布局也应尽可能参照参考设计。如果布局无法遵循参考设计（由于 PCB 尺寸和形状限制），建议采用下列部分所述的布局设计规则。

## 1.1 2.4 GHz EFR32 系列 1 无线 MCU 的匹配网络类型

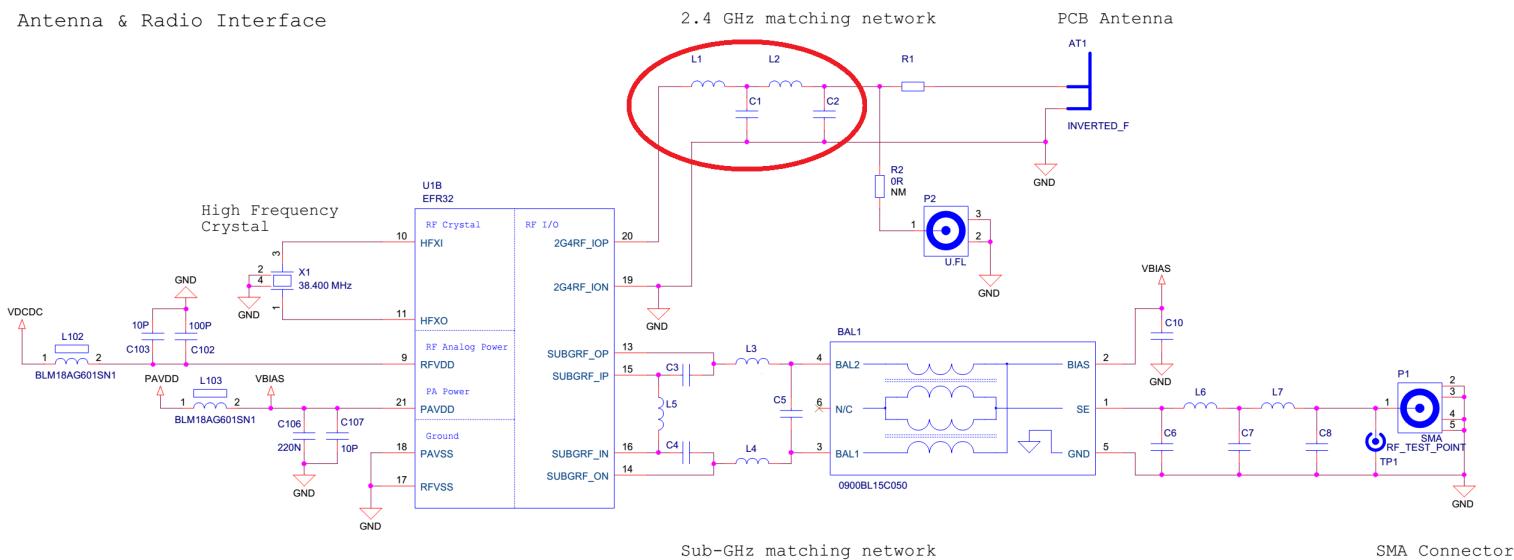

EFR32 系列 1 双频（2.4 GHz 和 1 GHz 以下）参考无线电板的天线和无线电接口示意图如下，2.4 GHz 匹配以红框圈出。

Figure 1.2. EFR32 系列 1 双频参考无线电板 RF 部分的示意图（2.4 GHz 匹配已圈出）

**Note:** 应根据功率范围，选择 2.4 GHz 频带的匹配网络元件值。要了解正确的组件值，请参见参考设计。仅 2.4 GHz EFR32 和双频 EFR32 有不同的引出线。要了解正确的引出线信息，请参见数据表和参考设计。

2.4 GHz EFR32 系列 1 无线 MCU 可提供最大 +19.5 dBm 的功率。2.4 GHz 的所有 EFR32 系列 1 参考设计均使用 L 系列并联 C 梯级匹配网络。对于低功耗应用 ( $\leq 10$  dBm)，2 元素 L-C 网络已足够，而高功耗解决方案 ( $> 10$  dBm) 则需要 4 元素匹配。

在上图中，4 云素匹配窗有一个额外的元件 (P1)，基本上不属干匹配网络。P1 的默认值为  $2\Omega$ 。在使用 2 云素匹配网络的仅 2.4 GHz 天线电板上，P1 被

在上图中，4 元素匹配旁还有一个额外的元件 R1，基本上不属于匹配网络。R1 的默认值为 0.12。在使用电感取代，用于抑制辐射的二次谐波。正确值会随着天线结构而改变，在大部分情况下可使用 0 Ω。

有关 2.4 GHz 匹配网络原则的进一步详情载于应用说明 [AN930.1: EFR32 系列 1 2.4 GHz 匹配指南](#)。

## 1.2 1 GHz 以下 EFR32 系列 1 无线 MCU 的匹配网络类型

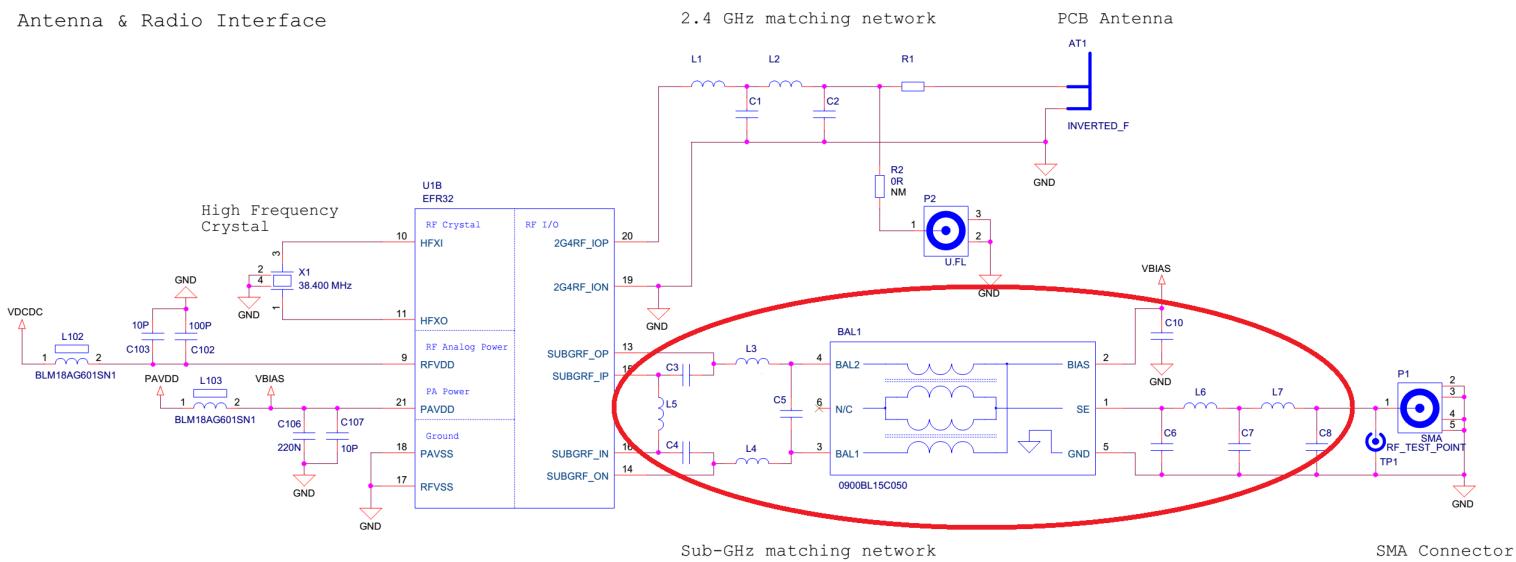

EFR32 系列 1 双频（2.4 GHz 和 1 GHz 以下）参考无线电板的天线和无线电接口示意图如下，1 GHz 以下匹配以红框圈出。

Figure 1.3. EFR32 系列 1 双频参考无线电板 RF 部分的示意图（1 GHz 以下匹配已圈出）

**Note:** 应根据频带选择匹配网络元件值。不同频带的匹配网络结构略有不同。如需了解正确的匹配网络信息，请参见数据表和参考设计。

1 GHz 以下 EFR32 系列 1 无线 MCU 可提供最大 +19.5 dBm 的功率。所有 1 GHz 以下 EFR32 匹配网络包含下列部分：阻抗变换电路、差分至单端平衡-不平衡转换器和低通滤波。

有关 1 GHz 以下匹配网络原理的进一步详细信息，请参见应用说明 [AN923: EFR32 1 GHz 以下匹配指南](#) 中讨论。

所有 1 GHz 以下的无线电板均包含一个 SMA 连接器，可用于传导测量或者连接外部天线，进行辐射测试。

## 2. 使用 EFR32 无线 MCU 的布局设计指南

设计 RF 相关布局实现优良 RF 性能的一般指南包括：

- 对于自定义设计，请尽可能使用与参考设计相同数量的 PCB 层。与参考 PCB 层数出现偏差会导致不同的 PCB 寄生电容，无法实现匹配网络的最佳形态。如果需要层数与参考设计不同的设计，请确保顶层和内部第一层之间的距离与参考设计相似，因为这个距离决定了接地的寄生电容值。否则可能会出现匹配网络失调，可能需要微调元件值。

- 请使用尽可能连续和统一的接地层敷金属，特别是顶层和底层。

- 避免接地层敷金属分离，尤其是在匹配网络的底层和 RFIC GND 引脚/裸焊盘之间。

- 请使用尽可能多的接地孔（尤其是在 GND 引脚附近），以尽可能降低不同层的接地灌流和 GND 引脚之间的串联寄生电感。

- 请沿 PCB 边缘和内部 GND 金属灌流边缘使用一系列 GND 针脚孔。孔之间的最大距离应小于 10 次谐波的 Lambda/10（参考无线电板上孔之间的距离一般为 40 - 50 mil）。该距离能够在这些边缘的弥散场造成的高谐波下降低 PCB 辐射。

- 对于两层以上的设计，建议在内层放置尽可能多的走线（甚至是数字走线），确保顶层和底层有大规模的连续 GND 灌流。

- 避免使用长和/或薄的传输线连接与 RF 相关的元件。否则由于分布式寄生电感，可能发生某些失谐作用。此外，请尽可能缩短互连线，降低接地的并联寄生电容。但是，相邻分立元件的偶联可能会增加。

- 要减少相邻分立元件电感之间的偶联，请避免将其同向放置。

- 在不同宽度（即不同阻抗）的传输线之间使用递变线路，以减少内部反射。

- 避免使用回路和长线，以消除共振。它们还可用作不良辐射体，尤其是在谐波上。

- 请使用一些旁路电容确保优良的 V<sub>DD</sub> 滤波（尤其是工作频率范围）。电容的串联自谐应靠近滤波频率。过滤最高频率的旁路电容应最接近 EFR32 的 V<sub>DD</sub> 引脚。除基础频率外，应过滤晶体/时钟频率及其谐波（最高 3 次），以避免向上变频激励。

- 使用多个孔将晶体壳接地，避免未接地部件的辐射。请勿断开和悬空任何可能是不良辐射体的金属。请避免引导电源走线靠近晶体或在晶体下方，或者与晶体信号或时钟走线并联。

- 确保 RF 相关部件（尤其是天线）远离直流转换器输出和相关的直流元件。

- 请避免 GPIO 线路靠近 RF 线、天线或晶体或在其下方，或者与晶体信号并联。请使用 GPIO 线上尽可能最低的偏差率，降低对 RF 或晶体信号的串扰。

- 请使用尽可能短的 V<sub>DD</sub> 走线。V<sub>DD</sub> 走线可以是隐藏的不良辐射体，以便尽可能简化 V<sub>DD</sub> 布线，并使用带有很多针脚孔的大规模连续 GND 灌流。要简化 V<sub>DD</sub> 布线，请尽量避免 V<sub>DD</sub> 走线的星形拓扑（即避免连接一个通用点中的所有 V<sub>DD</sub>）。

- 在天线附近使用丝网会对天线的绝缘环境造成轻微的影响。尽管这一影响通常可以忽略，但是请尽量避免在天线或天线灌流遮挡区使用丝网。

### 2.1 基于双频（2.4 GHz 和 1 GHz 以下）参考无线电板的 2.4 GHz 频带 EFR32 系列 1 无线 MCU 布局

该部分中显示的示例基于 EFR32 系列 1 双频参考无线电板的布局。主布局设计概念与此布局一同显示，用于展示基本原理。尽管这些规则将通过使用 4 元素匹配的设计显示，但是类似的设计实践也应通过 2 元素匹配网络进行应用。本部分中的大多数布局指南具有通用性，也应在 1 GHz 以下布局设计中运用。

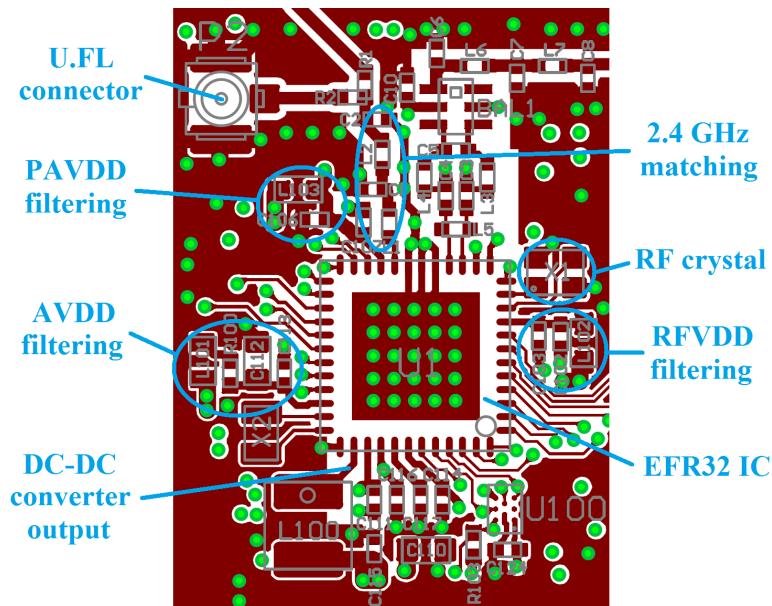

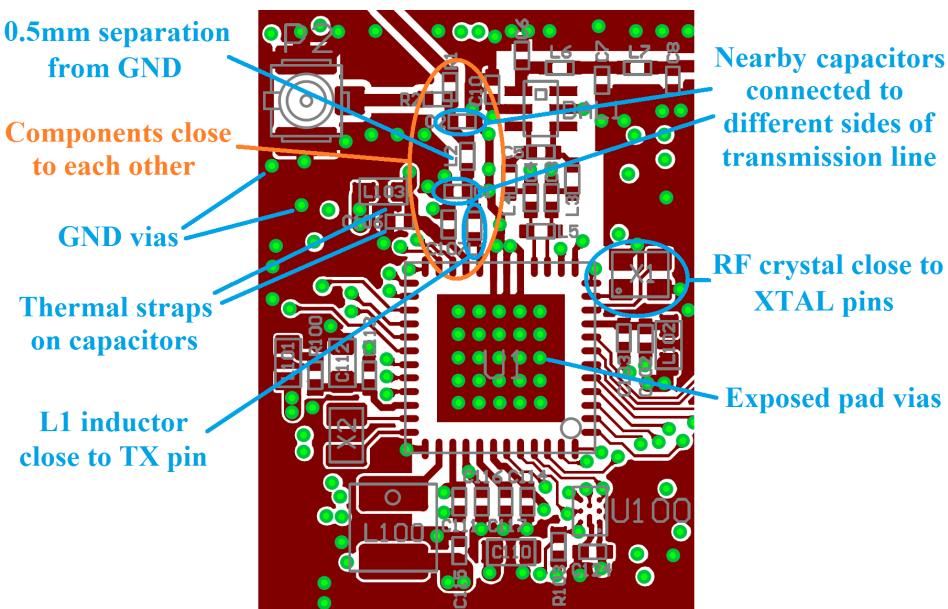

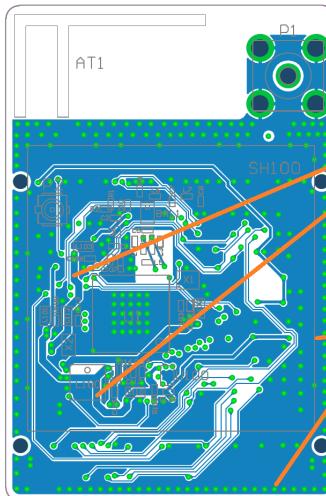

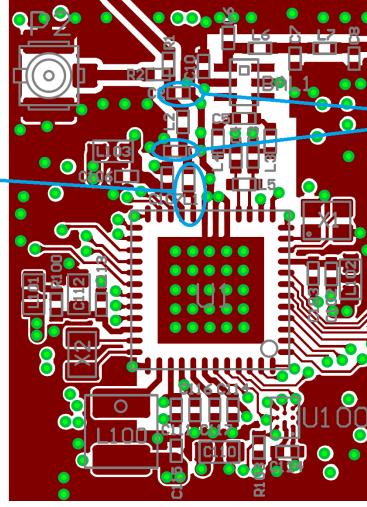

EFR32 系列 1 双频参考无线电板 RF 部分的布局结构示意图如下，2.4 GHz 匹配以蓝框圈出。

Figure 2.1. Layout of the RF Section for the EFR32 Series 1 Dual-band Reference Radio Board (2.4 GHz Matching is Highlighted)

## 2.1.1 布局设计指南 (2.4 GHz)

- L1 电感应尽可能靠近 EFR32 IC 的 2G4RF\_IOP 引脚（ $7 \times 7$  mm 大小封装上的引脚 17），以降低串联寄生电感，同时避免任何失谐作用。

- 相邻匹配网络元件应尽可能彼此靠近，以尽可能降低任何接地的 PCB 寄生电容以及元件之间的串联寄生电感。

- 应加厚电容 GND 引脚附近的走线，以改善散热带的接地效应。这能够尽可能降低接地灌流和 GND 引脚之间的串联寄生电感。靠近电容 GND 引脚的其他孔将其连接至内层/底层 GND 平面并可进一步降低这些效应。

- 低值  $V_{DD}$  旁通电容（带有  $\sim pF$  值）应尽可能靠近  $V_{DD}$  引脚（RFVDD、PAVDD、VREGVDD、AVDD、DVDD、IOVDD）。

- 要确保优良的接地连接，所有  $V_{DD}$  滤波电容应使用靠近接地引脚的多个孔。此外，建议不要以任何方式屏蔽  $V_{DD}$  滤波电容的 GND 孔和 RFIC 开关的 GND 孔之间的 GND 回路；返回电流应有明确、不受妨碍的路径通过 GND 平面抵达 RFIC 背部。

- EFR32 开关的裸焊盘封装应使用尽可能多的孔，确保优良的接地效果和散热能力。在参考设计中， $7 \times 7$  mm 大小封装 IC 有 25 个孔，每个孔的直径为 10 mil。

- RF 晶体应尽可能靠近 EFR32 IC 的 HFXI 和 HFXO 引脚，才能尽可能降低电线寄生电容和任何频率偏移。

- 在匹配网络区域，请至少在布线/盘与相邻 GND 灌流之间相隔 0.5 mm。该方法能够尽可能降低寄生电容并减轻失谐作用。

- 如果空间足够，应保持匹配网络附近的电感相互垂直，减少阶段之间的偶联。这有助于改善较高谐振频率下的滤波衰减。串联匹配/滤波电感可依次放置或相互垂直放置。

- 接地偶联可发生在附近滤波电容之间（尤其是高谐波下）并降低低通滤波的有效性，导致较高的传导和辐射谐波。为避免潜在的高谐波，建议将附近的谐波滤波电容与 **传输线不同端** 的接地层相连。

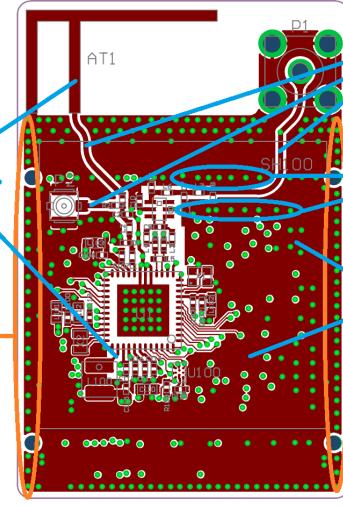

下图展示了上文列出的参考无线电板的设计建议。

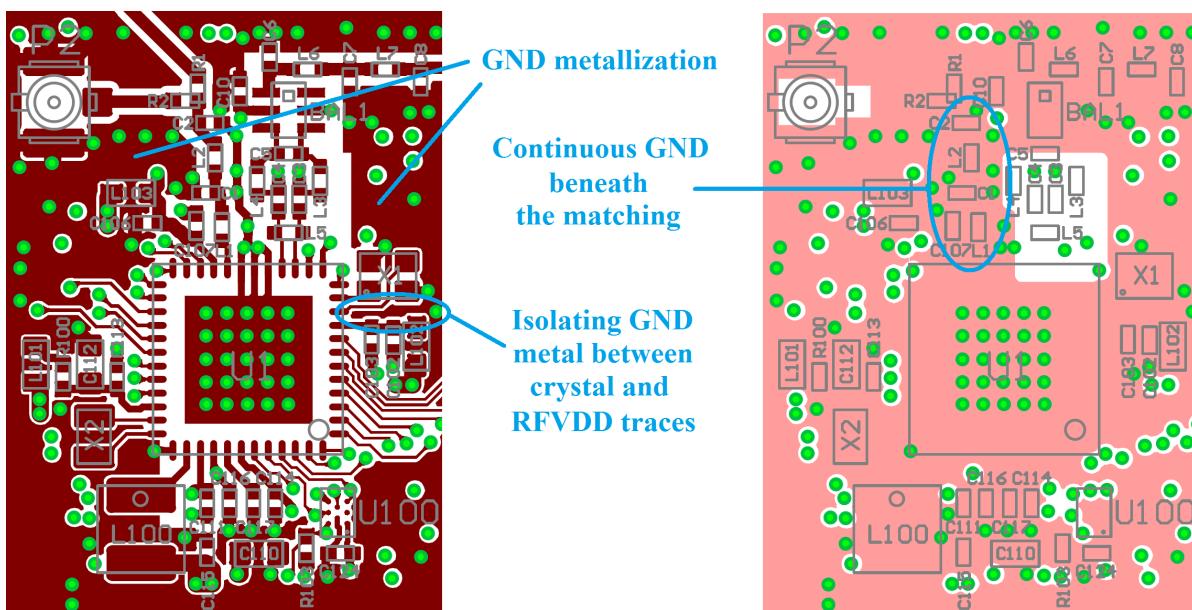

Figure 2.2. EFR32 Series 1 Layout Design Rules (Dual-band Reference Layout Top Layer)

- 为在布局上实现优良的 RF 接地，建议在 RF 部分区域的顶层添加大规模连续 GND 敷金属（最低程度）。如果应用于整个 PCB，则可实现更好的性能。要提供优良的 RF 接地，RF 电压电位应在整个 GND 区域相等，因为这有助于维持优良的  $V_{DD}$  滤波。应使用 GND 金属填充间隙，顶层和底层的最终部分应与尽可能多的孔相连。不在整个 GND 部分使用孔的原因是实际无线电板设计的限制。这些限制包括底端的其他层或元件上的走线，这些走线未在上图中显示。

- RF 芯片和匹配网络下方的区域（内部第一层上）应填充连续接地金属，因为其能够显示匹配网络的优良接地参考，并可确保到 RF 芯片接地的优良低阻抗回路。电路板布线不应放置在该区域，防止与匹配网络产生的偶联作用。此外，建议不要以任何方式屏蔽 TX/RX 匹配网络的 GND 孔和 RFIC 开关的 GND 孔之间的 GND 回路；返回电流应有明确、不受阻碍的路径通过 GND 平面抵达 RFIC 的背部。

- 请在晶体和 V<sub>DD</sub> 走线之间使用隔离接地金属，避免附近电源对晶体造成任何失谐作用，并避免晶体/时钟信号及其谐波泄露至电源线路。

Figure 2.3. EFR32 系列 1 布局设计规则（双频参考布局顶层和内层 1）

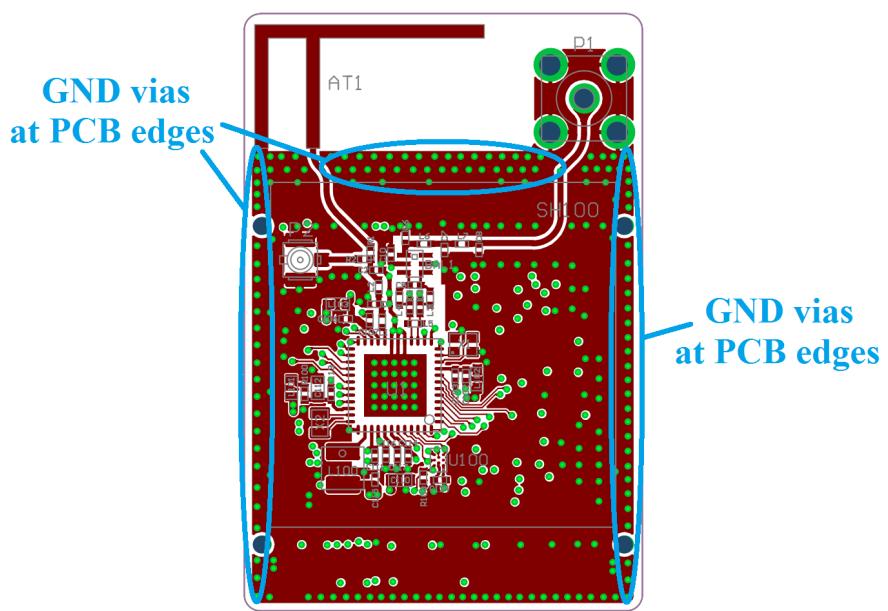

- 请在 GND 金属边缘使用尽可能多的并联接地孔，尤其是 PCB 的边缘以及 V<sub>DD</sub> 走线的沿线，降低弥散场造成的谐波辐射。

Figure 2.4. EFR32 系列 1 双频参考布局上 PCB 边缘的 GND 孔

- 如有必要，可使用屏蔽帽屏蔽 PCB 的谐波辐射；在此情况下，屏蔽帽应覆盖所有 RF 相关元件（不包括天线）。

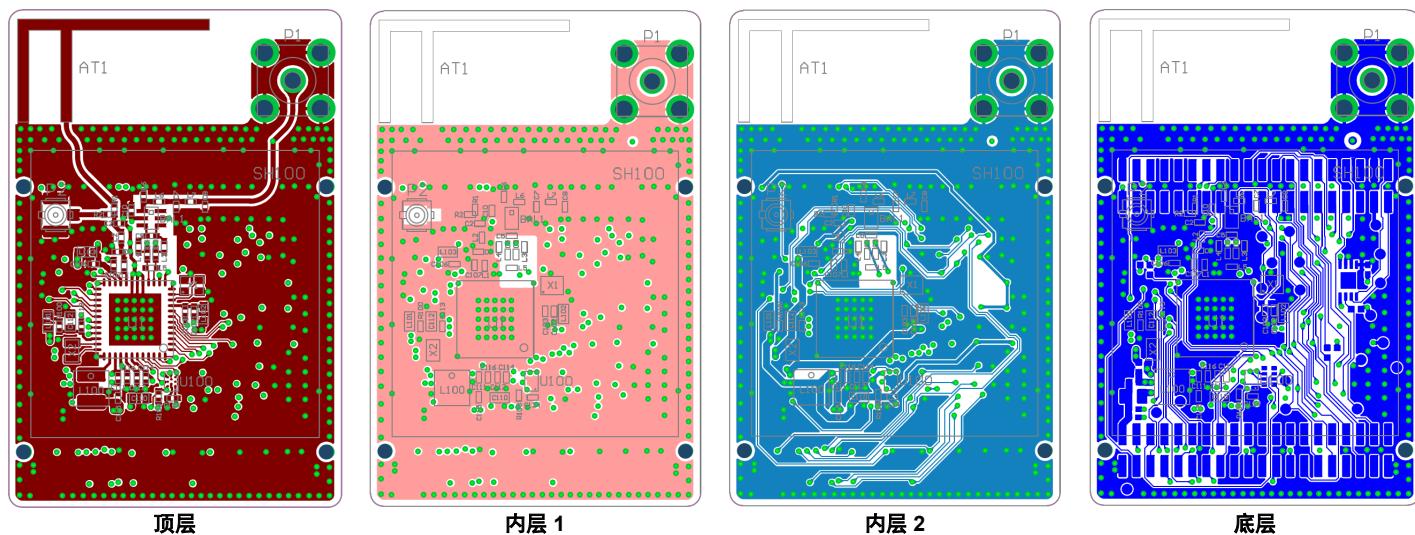

两层以上的 PCB 的理想层一致性如下：

- 顶层:** 请使用尽可能多的连续固体 GND 敷金属以及多个孔。

- 内部第一层:** 在 RF 部分下方使用连续统一的 GND 敷金属；如有必要，电线可布置在非 RF 部分的下方。

- 内部所有其他层:** 在这些层上尽可能多地进行布线（电源和数字）。

- 底层:** 该层应为统一的 GND 金属；仅在必要情况下在此层上进行布线。

下图展示了 EFR32 系列 1 双频参考无线电板布局的层一致性。

Figure 2.5. EFR32 系列 1 双频参考无线电板布局的层一致性

**Note:** 1 GHz 以下匹配针对各个 PCB 层有一些特殊布局建议，[2.2.1 布局设计指南（1 GHz 以下）](#) 将对此进行讨论。

- 在两层以上的电路板的内层进行布线（尤其是电源线和数字线）。

- 避免电源线靠近 PCB 边缘。

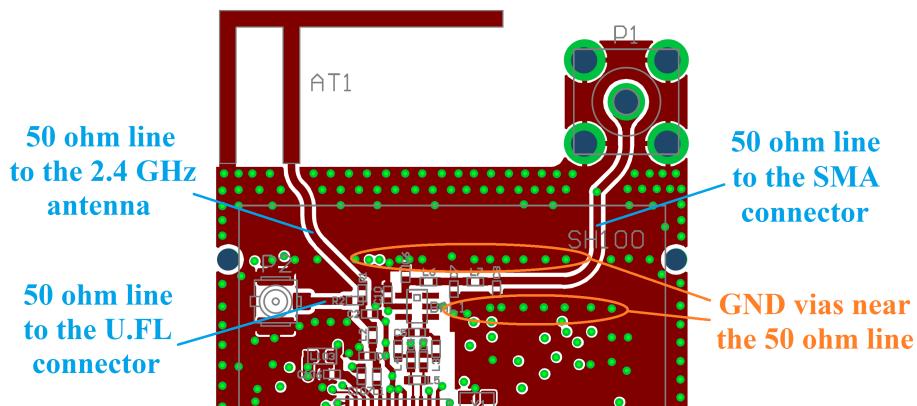

- 为降低对 PCB 厚度变化的敏感度，请尽可能使用  $50\ \Omega$  接地共面线，将天线或 U.FL 连接器连接到匹配网络。这还能够降低辐射和偶联作用。一般规则是使用  $50\ \Omega$  传输线，基本频率下的 RF 布线长度大于  $\lambda/16$ 。

- 元件之间的互连不属于传输线，因为其长度显著短于波长，因此其阻抗不具有决定性。因此，建议长度等于应用元件盘的宽度。在这种情况下，可防止盘走线转换的反射，并能够尽可能降低接地寄生电容。走线尺寸示例显示在下表中。

- 请在共面线附近使用多个孔，以尽可能降低辐射。

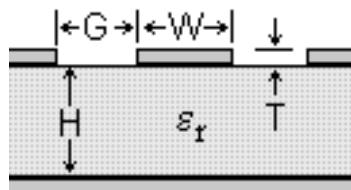

下表展示了 EFR32 系列 1 双频参考无线电板布局上的  $50 \Omega$  接地共面线。

Figure 2.6.  $50 \Omega$  Grounded Coplanar Lines on the Layout of the EFR32 Series 1 Dual-band Reference Radio Board

Table 2.1. Parameters for  $50 \Omega$  Grounded Coplanar Lines

| Lines        | Parameters       |

|--------------|------------------|

| f            | 2.4 GHz, sub-GHz |

| T            | 0.018-0.035 mm   |

| $\epsilon_r$ | 4.6              |

| H            | 0.325 mm         |

| G            | 0.25 mm          |

| W            | 0.45 mm          |

#### 注释:

- 特性阻抗对间隙值不具有超敏感度。应介于 0.25 至 0.4 mm 之间，才能实现 47 到 53  $\Omega$  的阻抗。

- 不同的阻抗计算器会产生略微不同的结果。

- H 是顶层和内部第一层之间的距离。

Figure 2.7. Grounded Coplanar Line Parameters

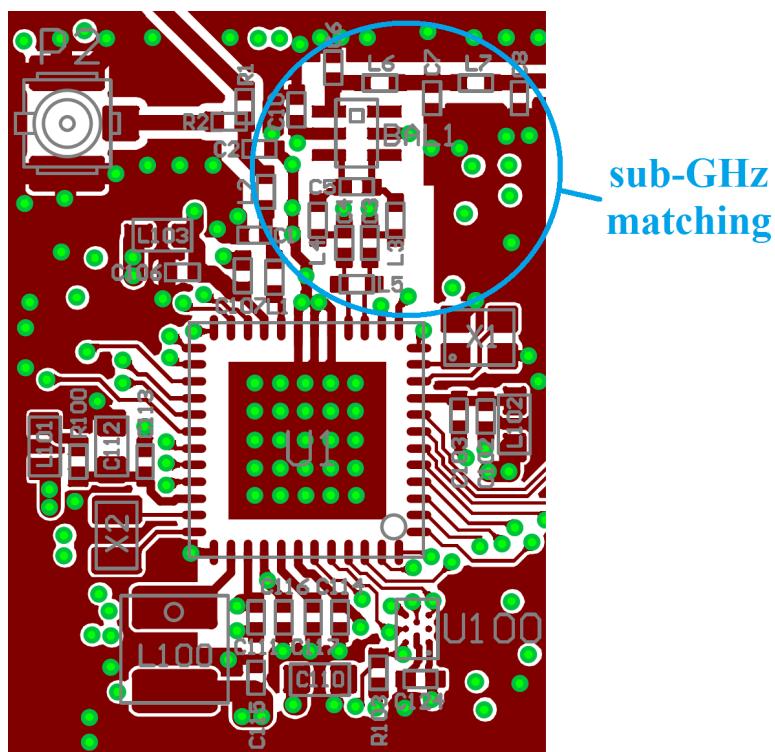

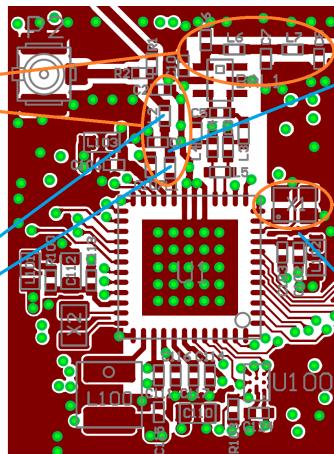

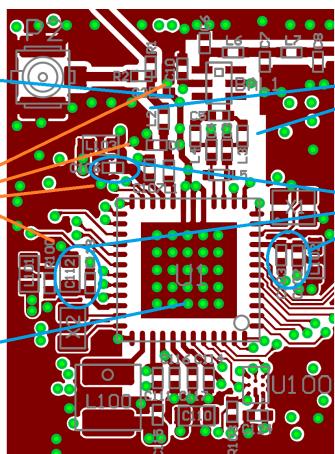

## 2.2 基于双频（2.4 GHz 和 1 GHz 以下）参考无线电板的 1 GHz 以下频带 EFR32 系列 1 布局

该部分中显示的示例基于 EFR32 系列 1 双频参考无线电板的布局。主布局设计概念与此布局一同显示，用于展示基本原理。尽管这些规则将通过使用 915 MHz 匹配的设计显示，但应通过其他 1 GHz 以下频率的匹配网络应用类似的设计实践。

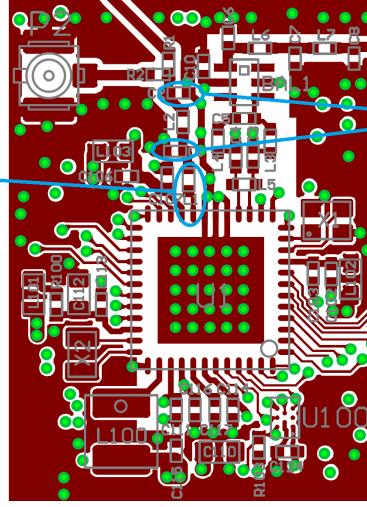

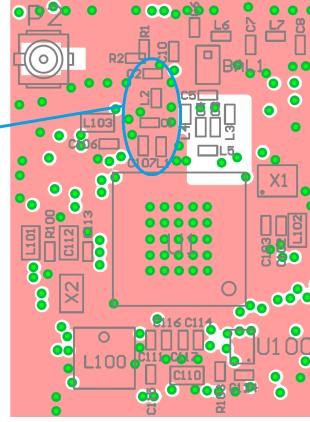

EFR32 系列 1 双频参考无线电板 RF 部分的布局结构示意图如下，1 GHz 以下匹配以蓝框圈出。

Figure 2.8. EFR32 系列 1 双频参考无线电板 RF 部分的布局（1 GHz 以下匹配已圈出）

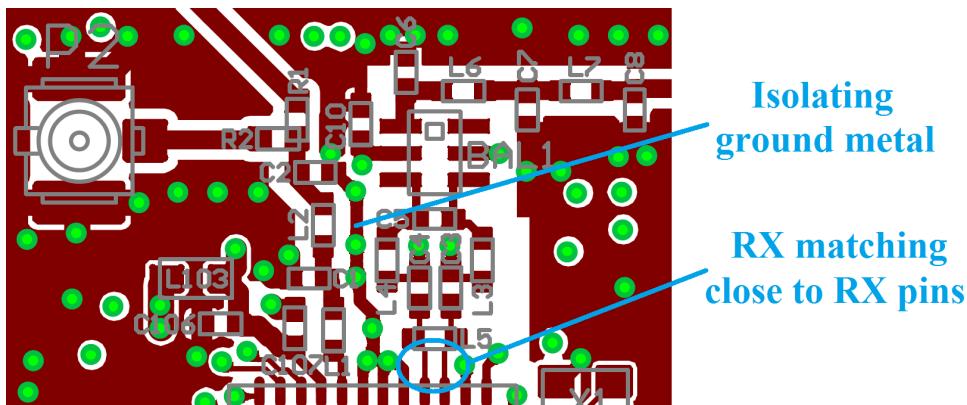

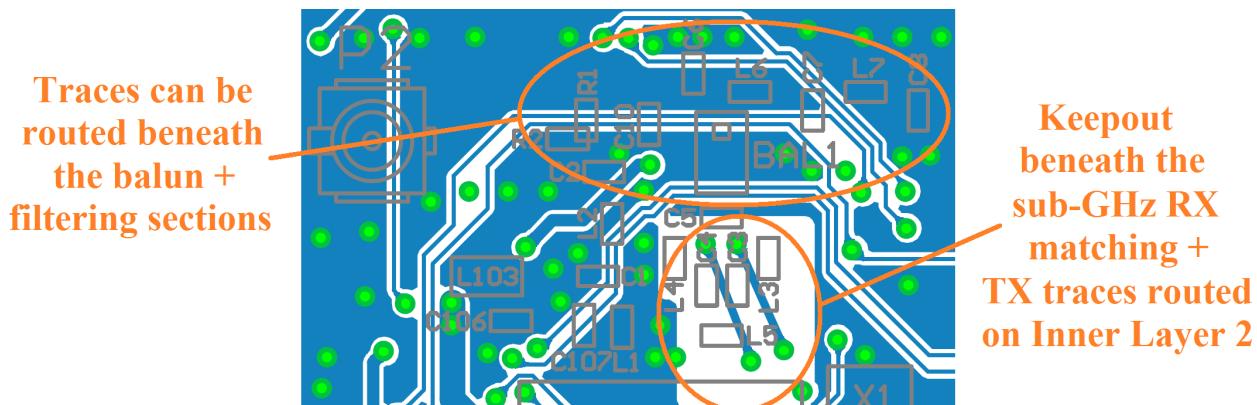

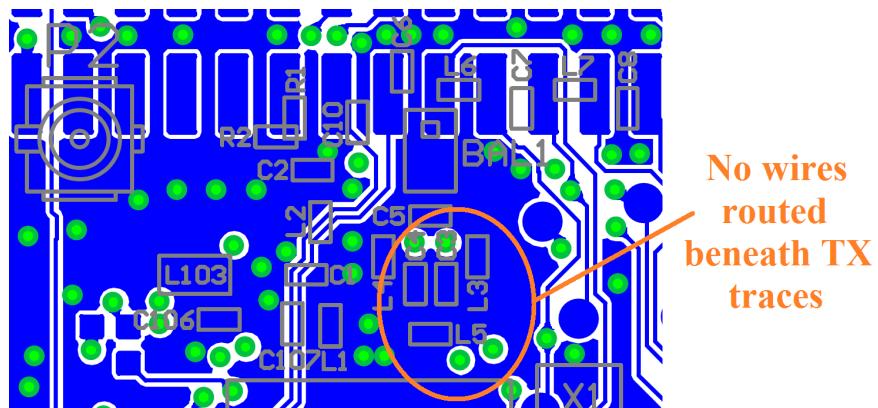

## 2.2.1 布局设计指南 (1 GHz 以下)

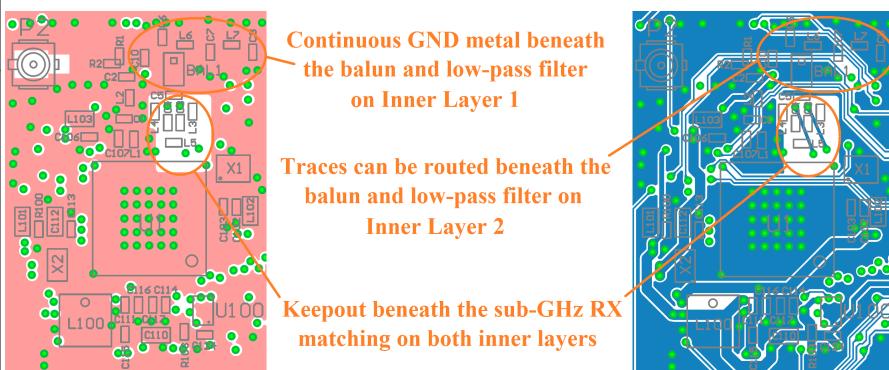

- 由于 1 GHz 以下 EFR32 系列 1 无线 MCU 的差分 TX/RX 引脚，将第一个 TX/RX 元件和芯片 TX 输出/RX 输入相连的走线必须位于不同层上。为降低接地的寄生电容，建议禁止在 RX 匹配网络区域下的所有内层上布线。在第一个内层，其余 1 GHz 以下匹配网络（平衡-不平衡变换器和低通滤波器）下的区域应填充接地金属。可在所有其他内层上平衡-不平衡变换器和低通滤波器的区域下方布线。

- 请使用尽可能最短的走线，将第一个 RX 匹配网络元件与芯片的 RX 输入引脚相连。因此，第一个 TX 匹配网络元件仅可连接较长的走线。

- 不得在连接第一个 TX 匹配元件和 TX 引脚的布线下方的层上布线。

- 建议在 2.4 GHz 和 1 GHz 以下匹配网络之间添加带有多个孔的隔离接地金属。

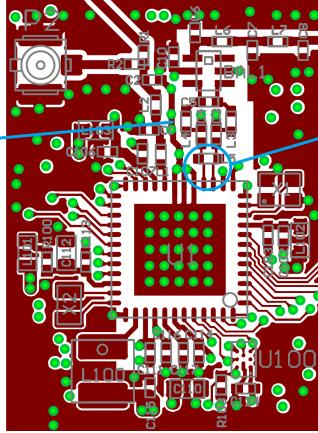

下图展示了 EFR32 系列 1 双频参考无线电板布局上匹配网络区域周围的层一致性。

Figure 2.9. EFR32 系列 1 双频参考布局匹配区布局 — 顶层

Figure 2.10. EFR32 系列 1 双频参考布局匹配区布局 — 内层 1

Figure 2.11. EFR32 系列 1 双频参考布局匹配区布局 — 内层 2

Figure 2.12. EFR32 系列 1 双频参考布局匹配区布局 — 底层

### 3. 对照表

#### 3.1 主布局设计原则

|     |                                                                                        |                                                                                     |

|-----|----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| 1.  | PCB 层数是否与参考设计相同？或者至少顶层和第一个内层之间的距离相似？                                                   |   |

| 2.  | 相邻匹配网络元件是否尽可能彼此接近？                                                                     |                                                                                     |

| 3.  | 布线宽度是否与连接附近元件的盘宽相同（相似）？                                                                |                                                                                     |

| 4.  | 串联匹配/滤波电感是否依次排列或者相互垂直？                                                                 |                                                                                     |

| 5.  | RF 晶体是否尽可能接近 EFR32 IC 的 XTAL 引脚？                                                       |                                                                                     |

| 6.  | 晶体和 RFVDD 馈送之间是否存在接地金属？                                                                |                                                                                     |

| 7.  | 最小值 VDD 滤波电容是否尽可能接近 EFR32 的 V <sub>DD</sub> 引脚 (RFVDD、PAVDD、VREGVDD、AVDD、DVDD、IOVDD) ？ |  |

| 8.  | 并联电容是否使用多个散热带？                                                                         |                                                                                     |

| 9.  | 并联电容的接地引脚是否使用多个孔？                                                                      |                                                                                     |

| 10. | 裸焊盘封装是否使用多个孔？                                                                          |                                                                                     |

| 11. | 布线/盘和 GND 金属之间的匹配是否至少间隔 0.5 mm？                                                        |                                                                                     |

| 12. | 是否避免在 VDD 滤波电容的接地孔和 EFR32 IC 的裸焊盘之间的第一个内 (GND) 层上进行布线？                                 |  |

|     |                                                        |                                                                                                                                                                                                                                                                                           |

|-----|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 13. | 是否在内层进行布置电源和数字线？或者如果布置在顶层或底层，电源线是否被带有很多 GND 孔的接地金属而环绕？ |  <p><b>Supply and digital traces routed on inner layer</b></p> <p><b>Placing supply or digital trace close to PCB edge is avoided</b></p>                                                               |

| 14. | 是否避免电源线或数字线靠近 PCB 边缘？                                  |  <p><b>Antenna far away from DC-DC converter</b></p> <p><b>50 ohm lines</b></p> <p><b>GND vias near the 50 ohm lines</b></p> <p><b>GND metallization</b></p> <p><b>Stitching vias at PCB edges</b></p> |

## 3.2 2.4 GHz 匹配网络的其他问题

|     |                                                  |                                                                                                                                                                                                                                                                  |

|-----|--------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 20. | 第一个匹配网络元件 (L1) 是否尽可能靠近对应的 TX 引脚?                 |  <p><b>First matching component close to TX pin</b></p>                                                                                                                        |

| 21. | 附近的谐波滤波电容是否连接至传输线不同端的接地层?                        |  <p><b>Nearby harmonic filtering capacitors connected to different sides of transmission line</b></p>                                                                          |

| 22. | 是否在 RF 芯片和匹配网络下的第一个内层区域填充了连续 GND 金属? 是否避免在此区域布线? |  <p><b>Continuous GND metal beneath the 2.4 GHz matching on the first inner layer</b></p>  |

## 3.3 1 GHz 以下匹配网络的其他问题

|     |                                                        |                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|--------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 23. | 第一个 RX 匹配网络元件是否尽可能靠近 RX 引脚?                            |                                                                                                                                                                                                                                                                                                                                                                                                   |

| 24. | 是否在 2.4 GHz 和 1 GHz 以下匹配网络之间添加了带有很多孔的隔离接地金属?           | <p style="color: blue; font-weight: bold;">Isolation of the 2.4 GHz and sub-GHz matching</p>  <p style="color: blue; font-weight: bold;">First RX matching component close to RX pins</p>                                                                                                                       |

| 25. | 是否禁止在 RX 匹配网络区域下的所有内层上布线?                              |                                                                                                                                                                                                                                                                                                                                                                                                   |

| 26. | 是否在平衡-不平衡变换器和低通滤波器下的第一个内层上的区域填充了连续 GND 金属? 是否避免在此区域布线? |  <p style="color: orange;">Continuous GND metal beneath the balun and low-pass filter on Inner Layer 1</p> <p style="color: orange;">Traces can be routed beneath the balun and low-pass filter on Inner Layer 2</p> <p style="color: orange;">Keepout beneath the sub-GHz RX matching on both inner layers</p> |

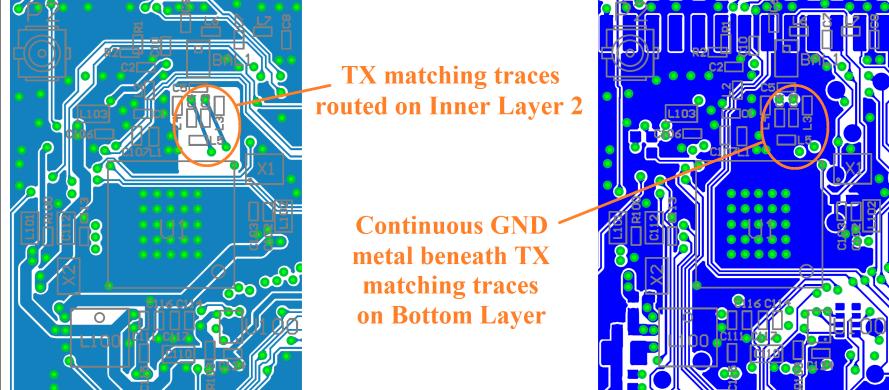

| 27. | 是否避免在连接第一个 TX 匹配网络元件和 TX 引脚的布线下方的层上布线?                 |  <p style="color: orange;">TX matching traces routed on Inner Layer 2</p> <p style="color: orange;">Continuous GND metal beneath TX matching traces on Bottom Layer</p>                                                                                                                                       |

# Simplicity Studio

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

## IoT Portfolio

[www.silabs.com/IoT](http://www.silabs.com/IoT)

## SW/HW

[www.silabs.com/simplicity](http://www.silabs.com/simplicity)

## Quality

[www.silabs.com/quality](http://www.silabs.com/quality)

## Support & Community

[www.silabs.com/community](http://www.silabs.com/community)

### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required, or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs product in such unauthorized applications.

### Trademark Information

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, ClockBuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, Gecko OS, Gecko OS Studio, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri, the Zentri logo and Zentri DMS, Z-Wave®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.