# AN0002.0: EFM32 および EZR32 Wireless MCU シリーズ 0 ハードウェア設計上の考慮事項

このアプリケーション・ノートでは、EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスのハードウェア設計に関する考慮事項について詳しく説明します。EFM32 および EFR32 Wireless Gecko シリーズ 1 デバイスのハードウェア設計に関する考慮事項については、次の資料を参照してください: *AN0002.1: EFM32 および EFR32 Wireless MCU シリーズ 1 ハードウェア設計上の考慮事項*

具体的には、サポートされる電源構成、電源フィルタリングに関する考慮事項、デバッグ・インターフェイス接続、および外部クロック・ソースについて説明します。

また、EFM32 シリーズ 0 マイクロコントローラの基準設計も記載されています。

## 要点

- ・デバイスの電源の整合性を確保するには、デカップリング・コンデンサが必要です。

- ・デバッグ・インターフェイスは、2 つの通信用ピン (SWCLK と SWDIO) で構成されています。

- ・適切に動作させるには、外部クロック・ソースをデバイスに正しく接続する必要があります。

- ・このアプリケーション・ノートに含まれる内容：

- ・本 PDF ドキュメント

- ・基準設計 (zip)

- ・OrCAD 回路図設計ファイル

- ・PDF 回路図

- ・シンボル・ライブラリ (OrCAD、CSV、Edif 形式)

## 第1章 デバイスの互換性

このアプリケーション・ノートは複数のデバイス・ファミリを対象にしています。一部の機能はデバイスによって異なります。

EFM32 シリーズ 0 は、以下で構成されています:

- EFM32 Gecko (EFM32G)

- EFM32 Giant Gecko (EFM32GG)

- EFM32 Wonder Gecko (EFM32WG)

- EFM32 Leopard Gecko (EFM32LG)

- EFM32 Tiny Gecko (EFM32TG)

- EFM32 Zero Gecko (EFM32ZG)

- EFM32 Happy Gecko (EFM32HG)

EZR32 Wireless MCU シリーズ 0 は、以下で構成されています:

- EZR32 Wonder Gecko (EZR32WG)

- EZR32 Leopard Gecko (EZR32LG)

- EZR32 Happy Gecko (EZR32HG)

## 第 2 章 電源の概要

### 2.1 はじめに

EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスの平均消費電流は非常に小さいですが、適切なデカップリングが必要です。すべてのデジタル回路で、電流はクロック・エッジに対応して短パルスで引き抜かれます。特に複数の I/O ラインが同時に切り替わる場合は、平均消費電流が非常に小さくても、電源の過渡電流パルスが数ナノ秒間、数百 mA オーダーになることがあります。

こいつた過渡電流は、高インピーダンス電源ラインを適切に伝送せず、供給電圧にかなりのノイズが発生します。このノイズを減らすために、この過渡電流の流れる短い間、電流を補足するデカップリング・コンデンサが使用されます。

### 2.2 デカップリング・コンデンサ

デカップリング・コンデンサは、高周波過渡電流に対応するために電源、MCU、グラウンド間の電流ループをできるだけ短くします。このため、すべてのデカップリング・コンデンサは、それぞれの電源ピン、接地ピン、PCB（プリント回路基板）接地面のできるだけ近くに配置する必要があります。

すべての外部デカップリング・コンデンサの温度範囲は、アプリケーションが使用される環境に対応している必要があります。たとえば、温度範囲が  $-55 \sim +85^{\circ}\text{C}$ （標準温度範囲デバイス）または  $-55 \sim +125^{\circ}\text{C}$ （拡張温度範囲デバイス）の場合は、キャパシタンスの変化が  $\pm 15\%$  の X5R セラミック・コンデンサが適しています。

レギュレータ出力コンデンサ（DECOPPLE および USB\_VREGO、使用可能な場合）の場合、システム設計者は、温度やバイアス電圧に関するコンデンサの特性に特に注意を払う必要があります。一部のコンデンサ（特に小型のパッケージや安価な誘電体を使用する場合）では、温度または DC バイアス電圧が上昇すると、キャパシタンスの値が大幅に低下する場合があります。レギュレータ出力キャパシタンスがデータシートに指定されている制限の範囲外になるような変更があると、その電源の出力が不安定になる場合があります。

### 2.3 電源要件

すべてのデバイスにおいて、電圧要件と電源ピン間の依存関係を考慮することが重要になります。システム設計者は、電力構成やトポロジにかかわらず、これらの電源要件を確実に満たす必要があります。絶対最大定格および相対的システム電圧制約の詳細については、デバイスのデータシートを参照してください。

#### EFM32 シリーズ 0 電源要件

- VDD\_DREG = AVDD = IOVDD

#### EZR32 Wireless MCU シリーズ 0 電源要件

- VDD\_DREG = AVDD = IOVDD = RFVDD

#### 電源ピンの概要

デバイスには、電源ピンのないものもあります。次の表では、各電源ピンとその場所を解説しています。

表 2.1. Power Supply Pin Overview

| Pin Name  | Product Family                 | Description                                                                  |

|-----------|--------------------------------|------------------------------------------------------------------------------|

| VDD_DREG  | All devices                    | Input to the internal digital LDO                                            |

| AVDD      | All devices                    | Supply to analog peripherals                                                 |

| DECOPPLE  | All devices                    | Output of the internal digital LDO                                           |

| IOVDD     | All devices                    | GPIO supply voltage                                                          |

| USB_VREGI | All USB-enabled devices        | Input to the internal 3.3 V LDO. Typically connected to the USB 5 V supply.  |

| USB_VREGO | All USB-enabled devices        | Output of the internal 3.3 V LDO                                             |

| RFVDD     | EZR32 Wireless MCU シリーズ 0 only | Supply to radio analog. Note, RFVDD also supplies the radio power amplifier. |

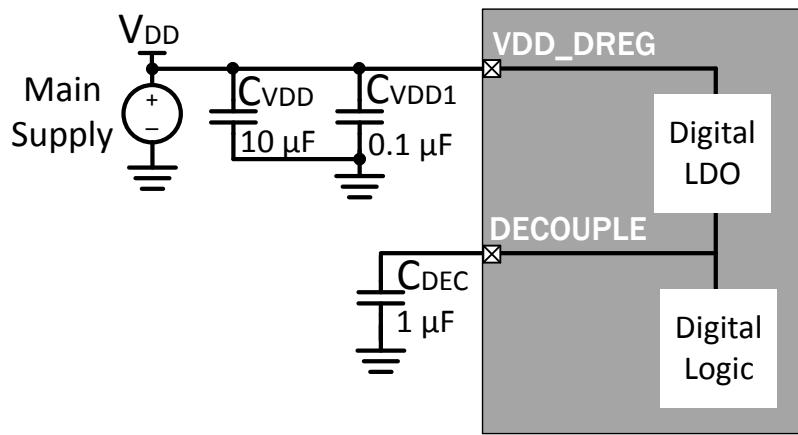

## 2.4 DECOUPLE

すべての EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスには、コアとデジタル・ロジックに電力を供給する内部リニア・レギュレータが搭載されています。DECOUPLE ピンは、デジタル LDO の出力であり、1  $\mu$ F のコンデンサが必要です。

VDD\_DREG ピンは LDO への入力で、DECOUPLE ピンは LDO の出力です。

図 2.1. VDD\_DREG および DECOUPLE

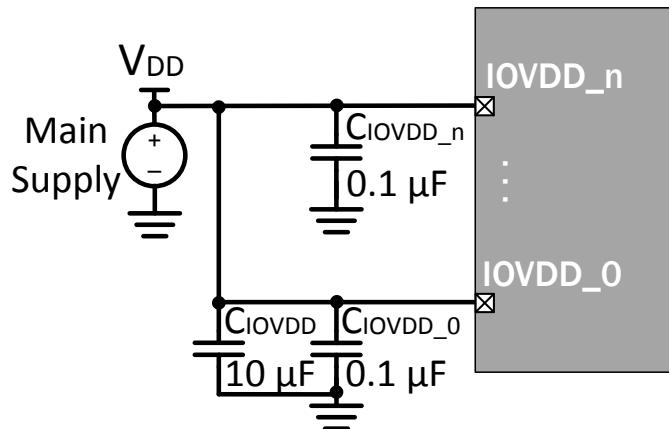

## 2.5 IOVDD

IOVDD ピンは、デバイスのすべての GPIO ピンにデカッピングを提供します。IOVDD ピンあたり 0.1  $\mu$ F のコンデンサ、および 10  $\mu$ F のバルク・コンデンサの使用が推奨されます。同じ電源上に容量の大きい他のバルク・コンデンサが存在する場合 (IOVDD = AVDD = システム主電源で、既に複数の 10  $\mu$ F が複数存在するなど)、バルク・コンデンサの値を安全に下げることができます。

図 2.2. IOVDD デカッピング

## 2.6 AVDD

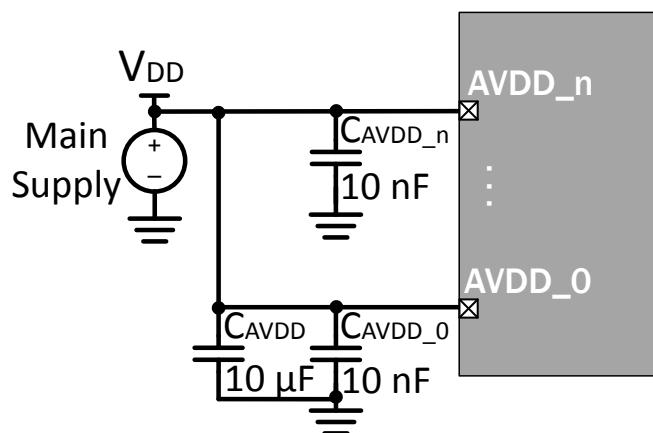

デバイスのアナログ・ペリフェラルの性能は、AVDD 電源の質に影響されます。アナログ性能があまり要求されないアプリケーションの場合は、AVDD の単純なデカッピング方式が許容されます。最高品質のアナログ性能を必要とするアプリケーションの場合は、より堅固なデカッピングとフィルタリングが必要になります。

AVDD アナログ電源ピンの数は、デバイスおよびパッケージによって異なることがあります。

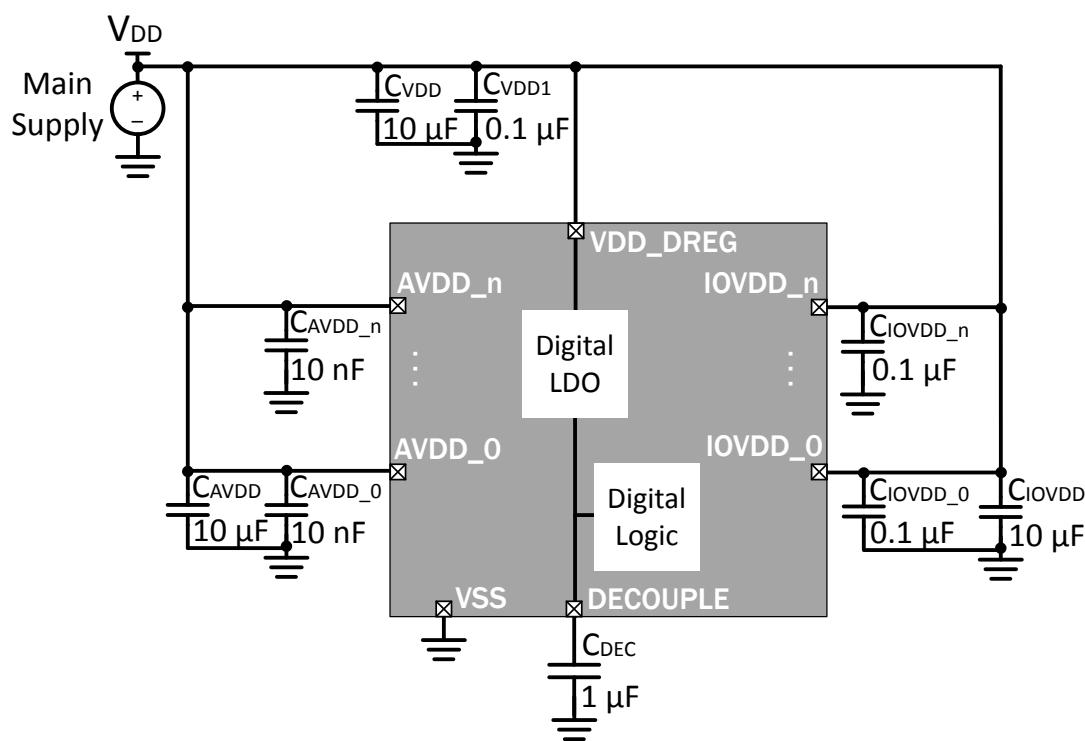

## 2.6.1 AVDD 標準的なデカップリング

下の図は、AVDD ピンのデカップリングの標準的なアプローチを示しています。一般に、10  $\mu$ F のバルク・コンデンサ ( $C_{AVDD}$ ) 1 つと、AVDD ピン ( $C_{AVDD\_0} \sim C_{AVDD\_n}$ ) ごとに 10 nF のコンデンサ 1 つを含める必要があります。

図 2.3. AVDD 標準的なデカップリング

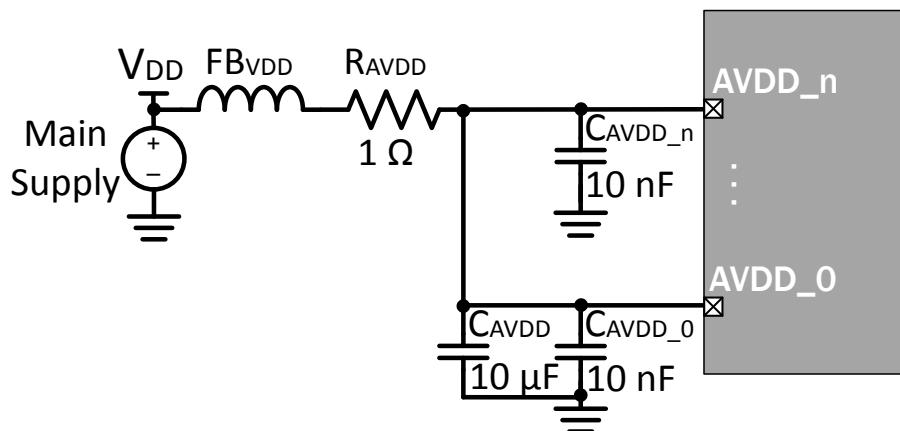

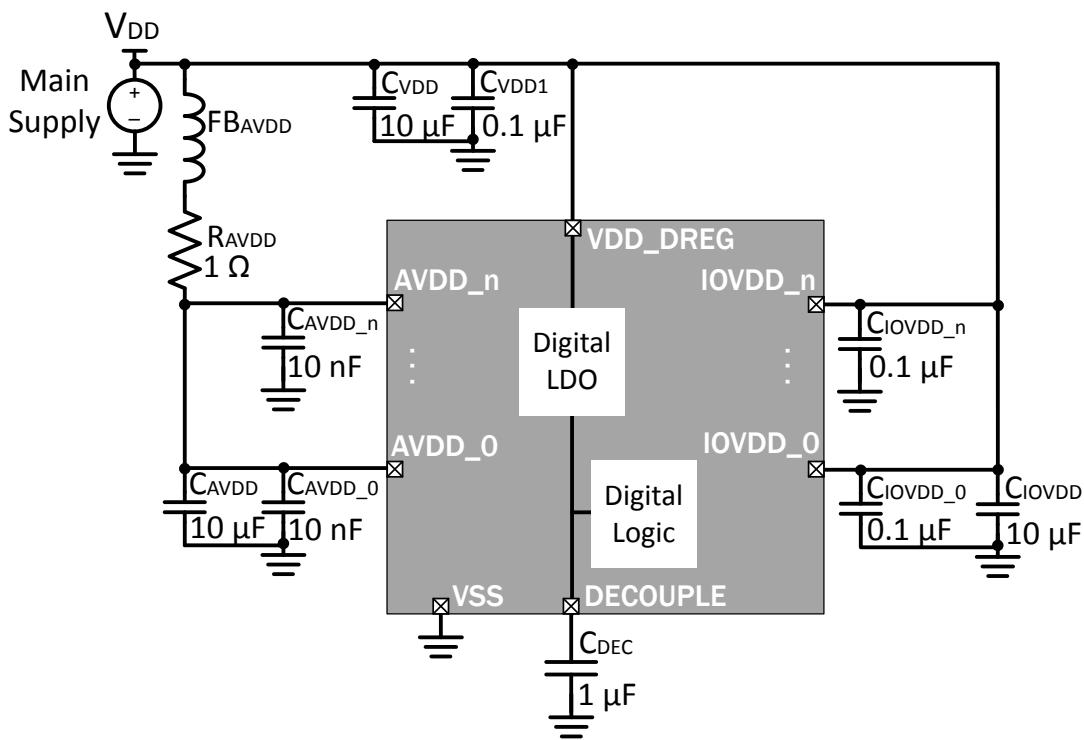

## 2.6.2 AVDD の改良されたデカップリング

下の図は、AVDD ピンのデカップリングとフィルタリングの改良されたアプローチを示しています。一般に、10  $\mu$ F のバルク・コンデンサ ( $C_{AVDD}$ ) 1 つと、AVDD ピン ( $C_{AVDD\_0} \sim C_{AVDD\_n}$ ) ごとに 10 nF のコンデンサ 1 つを含める必要があります。さらに、フェライト・ビーズとシリーズ 1  $\Omega$  の抵抗によって、電源のフィルタリングと絶縁が強化されます。

図 2.4. AVDD の改良されたデカップリング

下の表に、AVDD フィルタリングに適した推奨されるフェライト・ビーズの部品番号を示します。

表 2.2. Recommended Ferrite Beads

| Manufacturer      | Part Number    | Impedance              | $I_{MAX}$ (mA) | DCR ( $\Omega$ ) | Operating Temperature ( $^{\circ}\text{C}$ ) | Package   |

|-------------------|----------------|------------------------|----------------|------------------|----------------------------------------------|-----------|

| Würth Electronics | 74279266       | 1 k $\Omega$ @ 100 MHz | 200            | 0.600            | -55 to +125                                  | 0603/1608 |

| Murata            | BLM21BD102SN1D | 1 k $\Omega$ @ 100 MHz | 200            | 0.400            | -55 to +125                                  | 0805/2012 |

## 2.7 USB (USB\_VREGI &amp; USB\_VREGO)

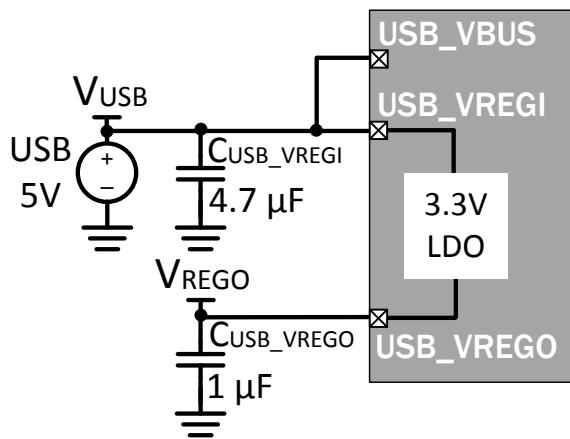

一部の EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスには USB コントローラと 3.3 V LDO が統合されています。下の図は、USB\_VREGI ピンと USB\_VREGO ピンの接続およびデカップリングの標準的アプローチを示しています。さらに、V<sub>USB</sub> は USB5 V センス・ライン (USB\_VBUS) に直接接続されています。

USB 仕様に反しないために、V<sub>USB</sub> の合計キャパシタンスは 10  $\mu$ F を超えないようにする必要があります。USB アプリケーションの詳細なハードウェア・ガイダンスについては、「AN0046 : USB ハードウェア設計ガイド」を参照してください。

図 2.5. USB\_VREGI および USB\_VREGO のデカップリング

## 第3章 電源構成の例

## 3.1 EFM32 シリーズ 0 – 標準的なデカップリングの例

下の図は、デカップリングの標準的アプローチを示しています。この構成は簡素で、最小限の部品しか使用せず、多くのアプリケーションに十分なノイズ抑制を提供します。

図 3.1. EFM32 シリーズ 0 標準的なデカップリングの例

## 3.2 EFM32 シリーズ 0 - 改良された AVDD フィルタリングの例

次の図では、フェライト・ビーズと抵抗を使用して、ノイズ抑制、およびデジタル電源ピンとアナログ電源ピン間の絶縁を向上させるデカッピング・アプローチを示しています。ADC でより高い精度が必要な場合は、この構成が推奨されます。推奨されるフェライト・ビーズの部品番号については、「[表 2.2 Recommended Ferrite Beads\(5 ページ\)](#)」を参照してください。

図 3.2. EFM32 シリーズ 0 改良された AVDD フィルタリングの例

**Note:** EFM32G および EFM32GG デバイスでは、IOVDD\_x ピンと VDD\_DREG ピンの後に AVDD\_x ピンをパワーアップすることはできません。電源の立ち上がり時間が短い場合は、[図 3.2 EFM32 シリーズ 0 改良された AVDD フィルタリングの例\(8 ページ\)](#) のフィルタによって AVDD\_x ピンに多大な遅延が発生することがあります。EFM32G および EFM32GG デバイスの改良された AVDD フィルタリングについては、「[3.3 EFM32G および EFM32GG のみ - 改良された AVDD フィルタリングの例](#)」セクションを参照してください。

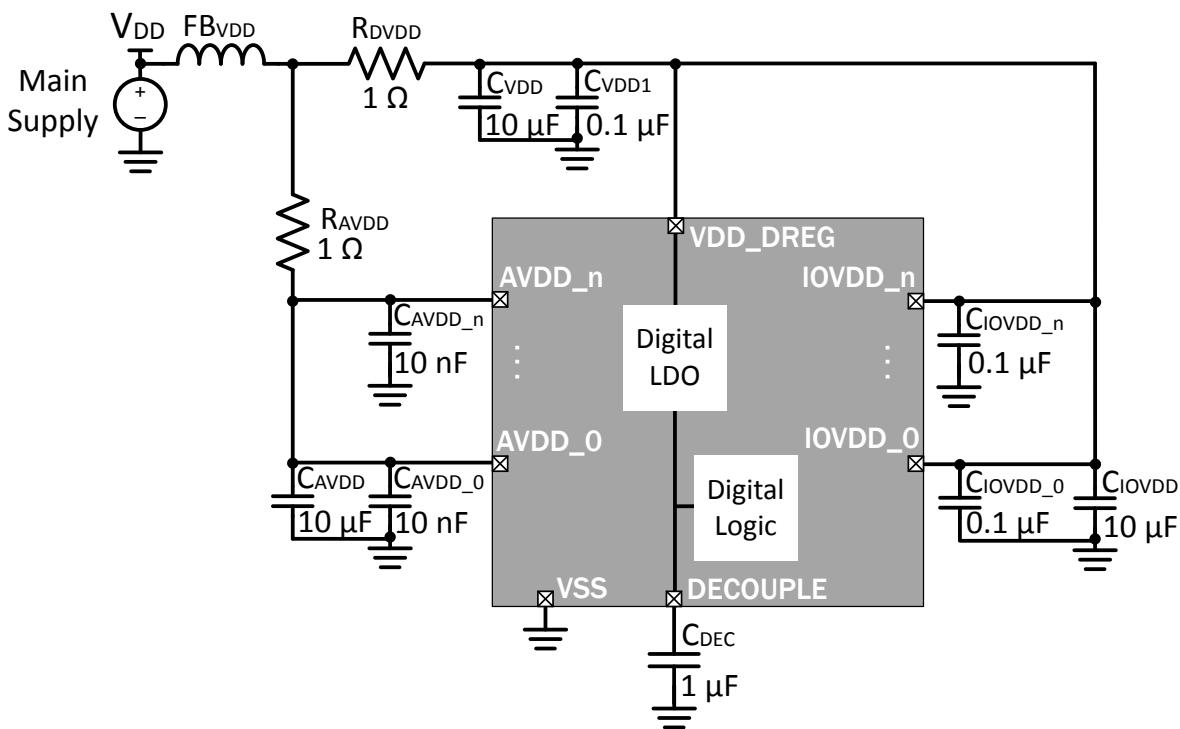

## 3.3 EFM32G および EFM32GG のみ – 改良された AVDD フィルタリングの例

「3.2 EFM32 シリーズ 0 – 改良された AVDD フィルタリングの例」セクションと同様に、下の図は、ADC の精度を高めるための改良されたノイズ抑制、およびデジタル電源ピンとアナログ電源ピン間の絶縁を示しています。推奨されるフェライト・ビーズの部品番号については、「表 2.2 Recommended Ferrite Beads(5 ページ)」を参照してください。

EFM32G および EFM32GG デバイスには固有の制約があり、IOVDD\_x ピンと VDD\_DREG ピンの後に AVDD\_x ピンをパワーアップすることはできません。電源の立ち上がり時間が短い場合は、AVDD フィルタによって AVDD\_x ピンに多大な遅延が発生する場合があります。このため、EFM32G および EFM32GG デバイスの場合は、下の図に示すように、VDD\_DREG 電源路にさらに 1 Ω の抵抗を追加する必要があります。

図 3.3. EFM32G および EFM32GG 改良された AVDD フィルタリングの例

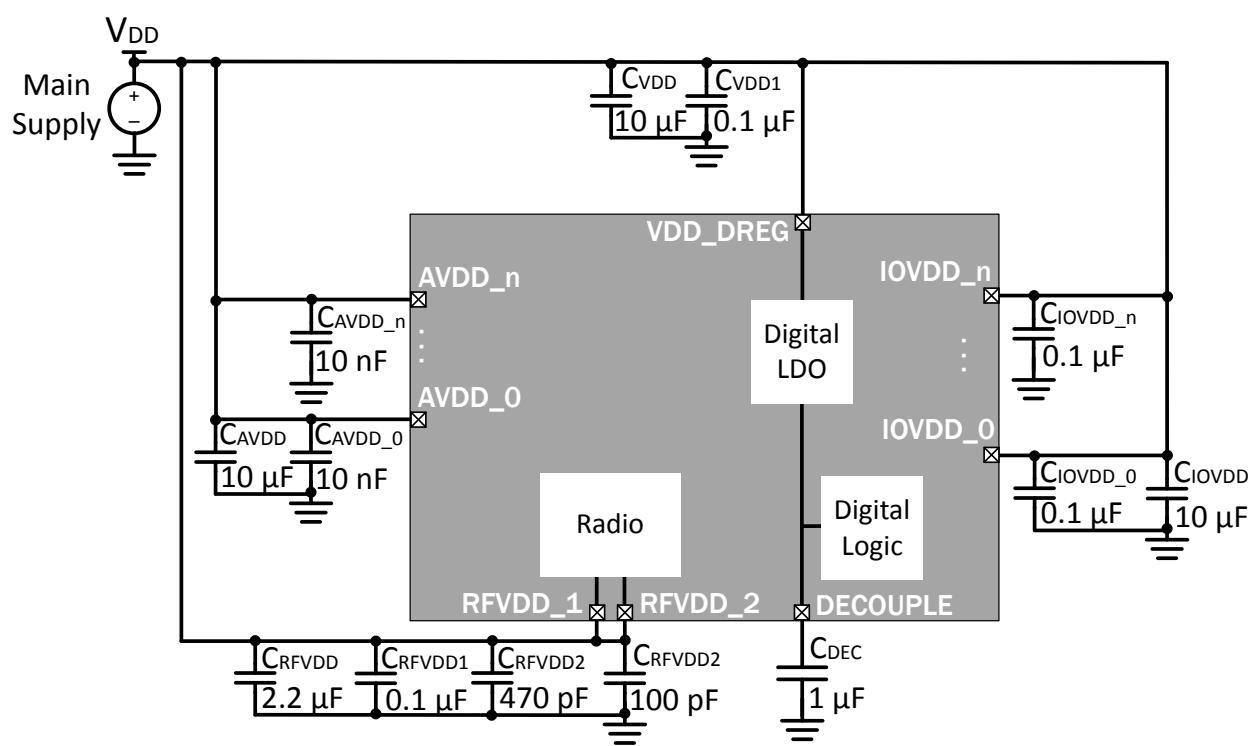

## 3.4 EZR32 Wireless MCU シリーズ 0 – 標準的なデカップリングの例

以下の図は、EZR32 Wireless MCU シリーズ 0 デバイスをデカップリングする標準的アプローチを示しています。

図 3.4. EZR32 Wireless MCU シリーズ 0 標準的なデカップリングの例

## 第4章 デバッグ・インターフェイスと外部リセット・ピン

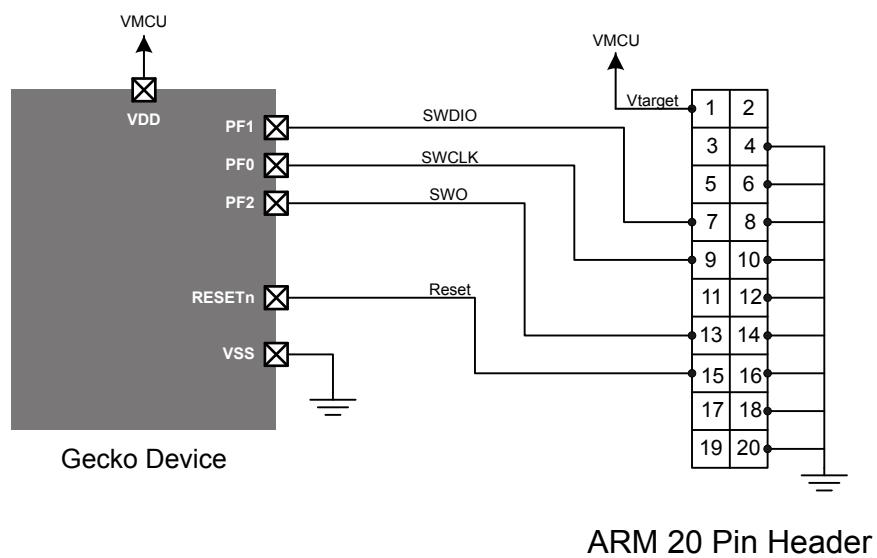

### 4.1 シリアル・ワイヤ・デバッグ

シリアル・ワイヤ・デバッグ (SWD) インターフェイスは、すべての EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスでサポートされており、SWCLK (クロック入力) ライン、SWDIO (データ入力/出力) ライン、およびオプションの SWO (シリアルワイヤ出力) で構成されています。SWO ラインは、インストルメンテーション・トレースとプログラム・カウンタ・サンプリングで使用されるもので、フラッシュのプログラミングや通常のデバッグには必要ありません。ただし、高度なデバッグを行う場合に役立つため、設計者はこれをその他の SWD 信号とともに含めることが強く奨励されています。

次の図は、標準の ARM 20 ピン・デバッグ・ヘッダへの接続を示しています。マイクロコントローラ、電源、またはグラウンドに接続されていないピンは、未接続のままにしておく必要があります。

図 4.1. EFM32 および EZR32 Wireless MCU シリーズ 0 ARM 20 ピン・デバッグ・ヘッダへの SWD 接続

#### Note:

1.  $V_{target}$  接続では、電力は供給されません。デバッガは、そのレベル・トランスレータの基準電圧として  $V_{target}$  を使用します。

2. PF2 は SWO 信号のデフォルトの場所であり、特定のパッケージにおいて PF0 (SWCLK) および PF1 (SWDIO) に隣接しているか、またはその付近に存在します。SWO は特定の他のピンにマッピングすることができます。該当するデバイスのデータシートを参照してください。

その他のデバッグおよびプログラミング・インターフェイスについては、アプリケーション・ノート『AN958: カスタム設計のデバッグおよびプログラミング・インターフェイス』を参照してください。

### 4.2 外部リセット・ピン (RESETn)

EFM32 および EZR32 Wireless MCU シリーズ 0 プロセッサは、RESETn ピンをローで駆動することでリセットされます。弱い内部プルアップ・デバイスでは RESETn ピンがハイに保持されるため、外部リセット・ソースが不要な場合は未接続のままにしておくことができます。また、RESETn にはローパス・フィルタも接続されており、ノイズ・グリッチによる意図しないリセットを防ぎます。プルアップ・デバイスと入力フィルタの特性は、GPIO ピンの特性と同じであり、デバイスのデータシートに記載されています。

**Note:** 内部プルアップは、リセットを確実にリリースするためのものです。デバイスが破損する可能性があるため、デバイスの電源が入っていない状態で RESETn を外部プルアップに接続したり、ハイで駆動したりしないでください。これはバックアップ電源モードの使用時にも重要になります。内部プルアップ・デバイスは自動的にバックアップ母線に切り替わり、RESETn に接続された外部プルアップによってシステムの他のデバイスに再び電力が供給されることがあります。

## 第 5 章 外部クロック・ソース

### 5.1 はじめに

EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスは、内部 LF と HF の RC 発振器に加え、高周波数クロックおよび低周波数クロックを提供するさまざまな外部クロック・ソースをサポートします。LF と HF の両方のドメインで使用可能な外部クロック・ソースは 水晶、セラミック共振器、外部発振器（方形波または正弦波）です。このセクションでは、外部クロック・ソースの接続方法について説明します。

外部発振器の詳細については、アプリケーション・ノート「AN0016.0: 発振器設計上の考慮事項」を参照してください。アプリケーション・ノートは、Silicon Labs のウェブサイト ([www.silabs.com/32bit-appnotes](http://www.silabs.com/32bit-appnotes)) または Simplicity Studio でご確認いただけます。

### 5.2 低周波数クロック・ソース

外部低周波数クロックは、水晶またはセラミック共振器 または外部クロック・ソースから供給できます。

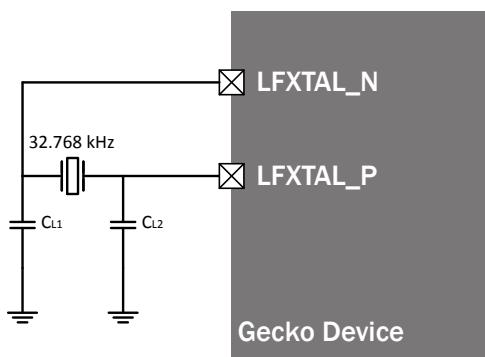

#### 5.2.1 低周波数水晶およびセラミック共振器

水晶およびセラミック共振器のハードウェア構成は、「[図 5.1 低周波数水晶\(12 ページ\)](#)」に示されています。水晶は、EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスの LFXTAL\_N ピンと LFXTAL\_P ピン間に接続する必要があります。

図 5.1. 低周波数水晶

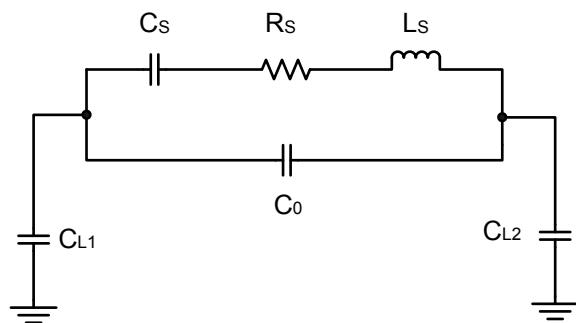

水晶/セラミック共振器は、機械的に共振し、[図 5.2 水晶/セラミック共振器の等価回路\(12 ページ\)](#) に示すように電気的等価回路を持ちます。電気回路では、 $C_S$  は動キャパシタンス、 $L_S$  は動インダクタンス、 $R_S$  は発振中の機械的損失、 $C_0$  はパッケージとピンの寄生キャパシタンスを表します。 $C_{L1}$  と  $C_{L2}$  は負荷キャパシタンスを表します。この回路は、水晶共振器とセラミック共振器の両方に有効です。

図 5.2. 水晶/セラミック共振器の等価回路

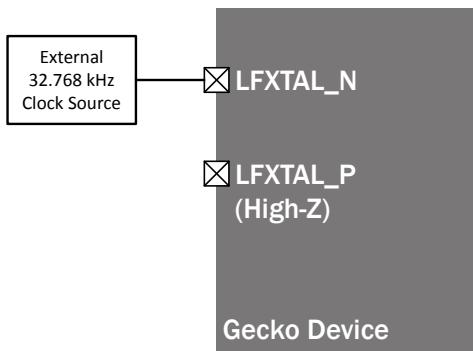

### 5.2.2 低周波数外部クロック

EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスは、TCXO や VCXO などの外部ソースから低周波数クロックを供給することができます。適切な外部発振器を選択するには、周波数、経年劣化、安定性、電圧感度、立ち上がり/立ち下がり時間、デューティ・サイクル、信号レベルなどの仕様を考慮してください。外部クロック信号として、周波数 32.768 kHz の方形波または正弦波のいずれかを使用できます。外部クロック・ソースは [図 5.3 低周波数外部クロック\(13 ページ\)](#) のように接続する必要があります。

バイパスおよびバッファ入力モードは、外部クロック・ソースでサポートされています。50% のデューティ・サイクルで 0 ~  $V_{DD}$  V の範囲で位相を切り替える CMOS 方形波は、LFXO をバイパスする CMU\_CTRL\_LFXOMODE = DIGEXTCLK で使用されます。最小振幅と最大振幅が 200 mV と  $V_{DD}$  V の外部正弦波ソース (CMU\_CTRL\_LFXOMODE = BUFEXTCLK) は、LFXTAL\_N ピンに直列で接続され、内部で AC 結合されます。正弦波の最小電圧は接地電圧よりも高く、最大電圧は  $V_{DD}$  未満である必要があります。

図 5.3. 低周波数外部クロック

### 5.3 高周波数クロック・ソース

外部高周波数クロックは、水晶またはセラミック共振器 または外部クロック・ソースから供給できます。

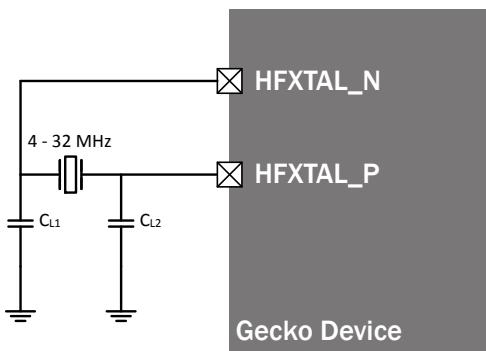

#### 5.3.1 高周波数水晶およびセラミック共振器

水晶およびセラミック共振器のハードウェア構成は、「[図 5.4 高周波数水晶発振器\(13 ページ\)](#)」に示されています。水晶は HFXTAL\_N ピンと HFXTAL\_P ピンの間に接続する必要があります。

高周波数水晶 / セラミック共振器の電気的等価回路は、[図 5.2 水晶/セラミック共振器の等価回路\(12 ページ\)](#) に示された高周波数水晶 / セラミック共振器の電気的等価回路と同じです。

適切な動作周波数を得るには、 $C_L$  の配置が重要です。

図 5.4. 高周波数水晶発振器

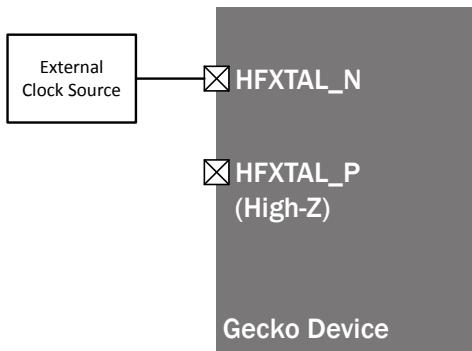

## 5.3.2 高周波数外部クロック

EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスは、TCXO や VCXO などの外部ソースから低周波数クロックを供給することができます。適切な外部発振器を選択するには、周波数、経年劣化、安定性、電圧感度、立ち上がり/立ち下がり時間、デューティ・サイクル、信号レベルなどの仕様を考慮してください。外部クロック信号には、デバイスのデータシートに従って、周波数の方形波または正弦波信号のいずれかが使用されます。外部クロック・ソースは [図 5.5 外部高周波数クロック\(14 ページ\)](#) のように接続する必要があります。

バイパスおよび外部でバッファされた入力モードは、外部クロック・ソースでサポートされています。50% のデューティ・サイクルで  $0 \sim V_{DD}$  V の範囲で位相を切り替える CMOS 方形波は、HFXO をバイパスする CMU\_CTRL\_HFXOMODE = DIGEXTCLK で使用されます。最小振幅と最大振幅が 200 mV と  $V_{DD}$  V の外部正弦波ソース (CMU\_CTRL\_HFXOMODE = BUFEEXTCLK) は、HFXTAL\_N ピンに直列で接続され、内部で AC 結合されます。正弦波の最小電圧は接地電圧よりも高く、最大電圧は  $V_{DD}$  未満である必要があります。

図 5.5. 外部高周波数クロック

## 第 6 章 基準設計

EFM32 および EZR32 Wireless MCU シリーズ 0 デバイスを使用して新しい設計を開始するとき、アプリケーションにかかわらず、レイアウトの一部はほとんど常に必要になります。このアプリケーション・ノートには、電力のデカップリング、リセット、外部クロック、デバッグ・インターフェイスの回路図の例が添付されています。この基準設計をテンプレートとして使用することで、新しい設計の初期段階で開発時間を短縮することができます。基準設計および含まれるシンボルは、Cadence OrCAD 9.0 以降のバージョンに対応しています。

このアプリケーション・ノートにはデバイスのフットプリントは含まれていませんが、<http://www.silabs.com> で \*.bxi 形式でご確認いただけます。

### 6.1 コンテンツ

アプリケーション・ノート・フォルダには、次の内容の zip ファイルが複数含まれています。

- ・ CSV ピン一覧ファイル

- ・ Edif シンボル

- ・ OrCAD OLB シンボル

- ・ OrCAD DSN 回路図の例

- ・ PDF 回路図の例

次のデバイス・ファミリの回路図とシンボルが含まれています。

- ・ EFM32ZG

- ・ EFM32HG

- ・ EFM32TG

- ・ EFM32G

- ・ EFM32LG

- ・ EFM32WG

- ・ EFM32GG

EZR32 Wireless MCU シリーズ 0 ファミリの汎用シンボルが含まれています。

### 6.2 回路図に関するコメント

#### 6.2.1 電源デカップリング

デカップリング・ピンは、 $1 \mu\text{F}$  のコンデンサを使用して、内部電圧レギュレータの電源ドメインの過渡電流をフィルタリングします。

第 3 章 電源構成の例 で説明されているように、 $10 \mu\text{F}$  の共通デカップリング・コンデンサの他に、 $10 \text{nF}$  のデカップリング・コンデンサが各電源ピンに接続されています。デジタル電源は、EMI を減らすためにアナログ電源から分離されています。アナログ電源のスイッチング・ノイズをさらに改善するために、 $V_{\text{MCU}}$  とアナログ電源ピンの間に EMI サプレッサを直列に配置します。

アクティブ・ロー・リセット・ピンは、ノーマル・オープン・スイッチを介してグラウンドに接続されており、デバッグ・インターフェイス・コネクタにも接続されています。

#### 6.2.2 デバッグ・インターフェイス

標準 ARM 20 ピン・デバッグ・コネクタは、EFM32 および EZR32 Wireless MCU シリーズ 0 デバイス・デバッグ・ピンに接続されています。

#### 6.2.3 高/低周波数クロック

高周波数および低周波数のクロック・ピンは、「AN0016 : 発振器設計の考慮事項」アプリケーション・ノートで推奨されている 2 つの水晶を使用して水晶発振器に接続されています。

## 第 7 章 修正履歴

### 改訂 1.50

2020 年 6 月

- ドキュメント・ソースに EFM32 および EFR32 Wireless Gecko シリーズ 1 デバイスを追加して再編したときの間違いを訂正しました。

- [5.2.2 低周波数外部クロック](#) と [5.3.2 高周波数外部クロック](#) の正弦波発振器入力に必要な振幅を訂正しました。

### 改訂 1.49

2019 年 12 月

- AN958 の [4.1 シリアル・ワイヤ・デバッグ](#) にリファレンスを追加。

### 改訂 1.48

2017 年 6 月

- デバイスの互換性情報をトップ・ページから [第 1 章 デバイスの互換性](#) に移動。

- [2.2 デカップリング・コンデンサ](#) のテキストの一部を変更。

### 改訂 1.47

2017 年 1 月

- アプリケーション・ノートをファミリに基づいて複数のアプリケーション・ノートに分割。

- レギュレータ出力コンデンサと DC-DC 出力コンデンサのキャパシタンス対温度の特性を確認するよう、システム設計者へのノートを追加。

## Simplicity Studio

One-click access to MCU and wireless tools, documentation, software, source code libraries & more. Available for Windows, Mac and Linux!

**IoT Portfolio**

[www.silabs.com/iot](http://www.silabs.com/iot)

**SW/HW**

[www.silabs.com/simplicity](http://www.silabs.com/simplicity)

**Quality**

[www.silabs.com/quality](http://www.silabs.com/quality)

**Support and Community**

[community.silabs.com](http://community.silabs.com)

### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required, or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs product in such unauthorized applications.

### Trademark Information

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, ClockBuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadioPRO®, Gecko®, Gecko OS, Gecko OS Studio, ISOmodem®, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri, the Zentri logo and Zentri DMS, Z-Wave®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.

**Silicon Laboratories Inc.**

400 West Cesar Chavez

Austin, TX 78701

USA

<http://www.silabs.com>