# AN1374: Series 2 TrustZone

This version of AN1374 has been deprecated with the release of Simplicity SDK Suite 2025.6.1.

For the latest version, see docs.silabs.com.

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

ARMv8-M TrustZone is a technology that provides a foundation for improved system security in embedded applications. It allows the ARMv8-M to be aware of the security states of the system. Series 2 devices use the Cortex-M33 core to implement the ARMv8-M TrustZone security extension, which provides the ability to restrict access to peripherals and memory regions based on the processor security attribute. TrustZone works with the MPU, which controls privileged/unprivileged execution of code to provide a complete security solution.

ARMv8-M TrustZone is an extensive topic. The references below are publicly available on the ARM Developer Documentation website.

- ARMv8-M Architecture Reference Manual

- ARMv8-M Architecture Technical Overview

- ARM Cortex-M33 Processor Technical Reference Manual

- · System Design with ARMv8-M

- TrustZone technology for ARMv8-M Architecture

- ARM Cortex-M33 Devices Generic User Guide

- · Secure software guidelines for ARMv8-M

- · Software Development in ARMv8-M Architecture

#### Reading guides:

- Beginner Minimal experience with TrustZone, starting with TrustZone Basics

- Intermediate Have a basic understanding of the TrustZone technology, starting with Bus Level Security

- Advanced Developed experience on TrustZone, starting with TrustZone Implementation

- · Demo Starting with TrustZone Platform Examples

#### **KEY POINTS**

- · TrustZone Basics

- · Bus Level Security (BLS)

- Secure and Privileged Programming Model

- · TrustZone Implementation

- · Upgrade Existing Application to TrustZone

- · TrustZone Platform Examples

# 1. Series 2 Device Security Features

Protecting IoT devices against security threats is central to a quality product. Silicon Labs offers several security options to help developers build secure devices, secure application software, and secure communication paths to manage those devices. Silicon Labs' security offerings were significantly enhanced by the introduction of the Series 2 products that included a Secure Engine. The Secure Engine is a tamper-resistant component used to securely store sensitive data and keys, and to execute cryptographic functions and secure services.

On Series 2 devices, the security features are implemented by the Secure Engine and CRYPTOACC (if available). The Secure Engine may be hardware-based or virtual (software-based). Throughout this document, the following abbreviations are used:

- · HSE Hardware Secure Engine

- · VSE Virtual Secure Engine

- SE Secure Engine (either HSE or VSE)

Additional security features are provided by Secure Vault. Three levels of Secure Vault feature support are available, depending on the part and SE implementation, as reflected in the following table:

| Level (1)               | SE Support         | Part                                                                                     |

|-------------------------|--------------------|------------------------------------------------------------------------------------------|

| Secure Vault High (SVH) | HSE only (HSE-SVH) | Refer to UG103.05: IoT Endpoint Security Fundamentals for details on supporting devices. |

| Secure Vault Mid (SVM)  | HSE (HSE-SVM)      | "                                                                                        |

| Secure Vault Mid (SVM)  | VSE (VSE-SVM)      | "                                                                                        |

| Secure Vault Base (SVB) | N/A                | "                                                                                        |

#### Note:

1. The features of different Secure Vault levels can be found in https://www.silabs.com/security.

Secure Vault Mid consists of two core security functions:

- Secure Boot: Process where the initial boot phase is executed from an immutable memory (such as ROM) and where code is authenticated before being authorized for execution.

- Secure Debug Access Control: The ability to lock access to the debug ports for operational security, and to securely unlock them

when access is required by an authorized entity.

Secure Vault High offers additional security options:

- Secure Key Storage: Protects cryptographic keys by "wrapping" or encrypting the keys using a root key known only to the HSE-SVH.

- · Anti-Tamper protection: A configurable module to protect the device against tamper attacks.

- Device authentication: Functionality that uses a secure device identity certificate along with digital signatures to verify the source or target of device communications.

Series 2 devices require a specific SE firmware version to support the TrustZone implementation. Refer to AN1222: Production Programming of Series 2 Devices to learn how to upgrade the SE firmware and UG103.05: IoT Endpoint Security Fundamentals for the latest SE Firmware shipped with Series 2 devices and modules.

Series 2 devices use Cortex-M33 core to implement the ARMv8-M Mainline TrustZone security extension and refer to TrustZone as Bus Level Security. The following table lists the configuration of TrustZone related components in the Series 2 Cortex-M33 core.

| Component                       | Series 2 Configuration | Description                                                                                        |

|---------------------------------|------------------------|----------------------------------------------------------------------------------------------------|

| Security Extension (TrustZone)  | Enabled                | The security extension cannot be disabled, and the entire memory after RESET is Secure by default. |

| Memory Protection Unit (MPU)    | 16 regions (maximum)   | The MPU regions for both Secure and Non-secure MPUs.                                               |

| Security Attribution Unit (SAU) | 8 regions (maximum)    | The SAU regions for Non-secure and Non-secure Callable.                                            |

#### 2. TrustZone Basics

#### 2.1 Introduction

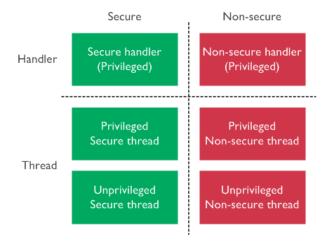

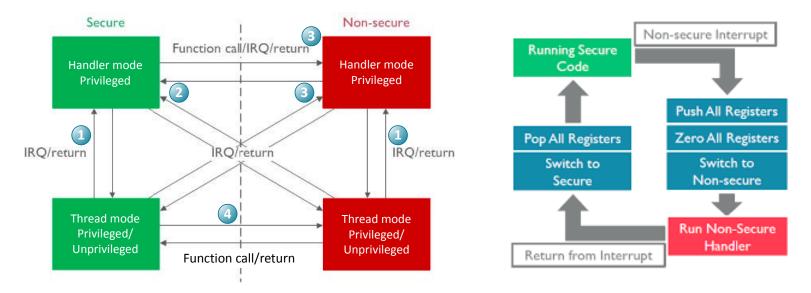

TrustZone for ARMv8-M adds extra states to the Cortex-M processor operations to ensure there is a Secure and Non-secure state. These security states are orthogonal to the existing Thread and Handler modes, thereby having both a Thread and Handler mode in both Secure and Non-secure states. The Thread mode can also be either Privileged or Unprivileged.

Figure 2.1. Operation States and Modes of TrustZone Implementation

Image: https://documentation-service.arm.com/. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

TrustZone for ARMv8-M is an optional architecture extension. By default, the system starts up in a Secure state if the processor implements the TrustZone security extension. The division of Secure and Non-secure worlds is memory-map based (security state depends on the address of the fetched instruction), and the transitions happen automatically. It is also possible to leave the Non-secure state unused and execute the whole application in the Secure state.

# 2.2 Memory Security Attributes

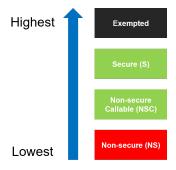

TrustZone classifies memory into four security attributes as described in the following table.

| Security Attribute        | Processor State   | Description                                                                                                                                                                                                                                                                                                                                                                                          |

|---------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-secure (NS)           | Non-secure        | Non-secure and Secure software can access these memory regions.                                                                                                                                                                                                                                                                                                                                      |

| Secure (S)                | Secure            | Secure software can access these memory regions. Non-secure software cannot gain access to the Secure memory.                                                                                                                                                                                                                                                                                        |

| Non-secure Callable (NSC) | Secure            | Secure memory with an NSC attribute provides entry points for Secure APIs that can be called from a Non-secure space. It is a region of memory that contains the Secure Gateway (SG) veneers that allow Non-secure code to call secure functions that exist in Secure code. Non-secure software cannot read/write to an NSC memory but can branch into it if the branch target is an SG instruction. |

| Exempted                  | Secure/Non-secure | Non-secure and Secure software can access these memory regions (exempted from security checking). Exempted regions are typically used by debugging components that do not pose any security risk (e.g., system ROM table) when accessed by the Non-secure software.                                                                                                                                  |

**Note:** The Non-secure Callable is also known as Secure Non-secure Callable (Secure NSC) to declare that this region resides in Secure memory.

# 2.3 Banked Register

The concept of a banked register in ARMv8-M between Secure and Non-secure states means that there are two copies of the register, and the core automatically uses the copy that belongs to the current security state. When a register is banked, the \_s and \_ns suffixes are used in the ARMv8-M architecture to identify whether the resource is for the Secure state or Non-secure state.

## 2.3.1 General-Purpose Registers

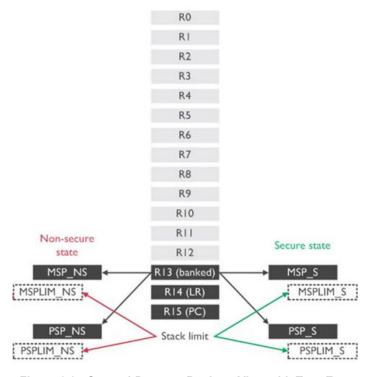

The Cortex-M processors have 16 general-purpose registers (R0 - R15) for data processing (R0 - R12) and control. The following figure shows the general-purpose register view of the ARMv8-M system with TrustZone. Refer to the ARM Cortex-M33 Devices Generic User Guide for details about these registers.

Figure 2.2. General-Purpose Register View with TrustZone

Image: https://documentation-service.arm.com/. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

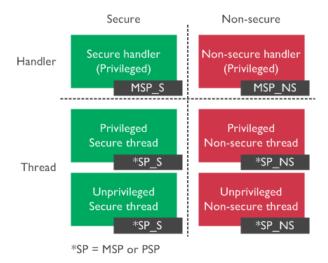

The Secure or Non-secure state can access the data processing registers R0 - R12 and special usage registers R13 - R15. The register R13 (banked SP) is the stack pointer alias, and the actual stack pointer (MSP\_NS, PSP\_NS, MSP\_S, PSP\_S) accessed depends on the state (Secure or Non-secure) and mode (Handler or Thread) as described in the following figure.

In addition, stack limit registers (special registers) enable hardware to detect stack overflow conditions. Two pairs of stack limit registers (MSPLIM\_NS and PSPLIM\_NS, MSPLIM\_S and PSPLIM\_S) are implemented, one per security state, to protect the Main Stack Pointer (MSP) and Process Stack Pointer (PSP).

Figure 2.3. Banked Registers in the General-Purpose Registers

Image: https://documentation-service.arm.com/. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

In Thread mode, execution can be privileged or unprivileged. The stack pointer used can be the MSP or PSP, depending on the SPSEL bit in the CONTROL register. When in Handler mode, the processor is Privileged. The stack pointer is always MSP.

It is possible to directly access the stack pointers (MSP and PSP) and stack limit registers (MSPLIM and PSPLIM), providing that the processor is in a privileged state. If the processor is in a Secure privileged state, the software can also access the Non-secure stack pointers (MSP\_NS and PSP\_NS) through Core Register Access Functions in CMSIS-Core.

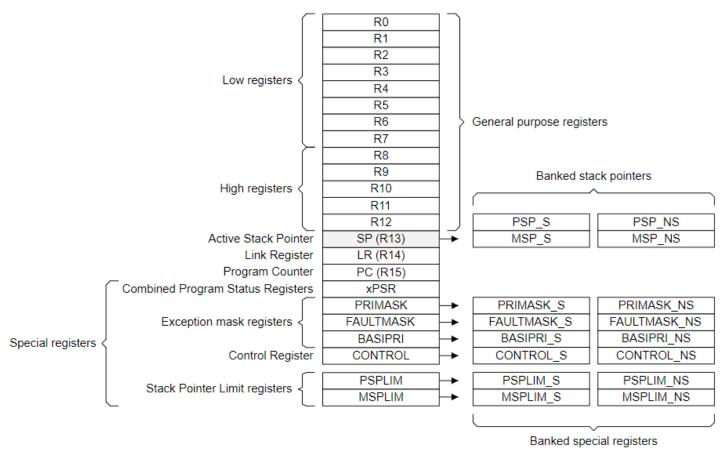

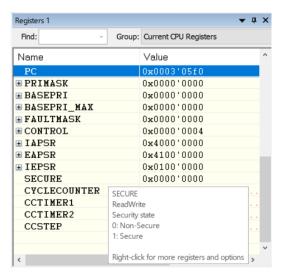

# 2.3.2 Special-Purpose Registers

Except for the general-purpose registers, there are several special-purpose registers for conditional flags, interrupt masking, control, and stack pointer limit. The following figure shows the special-purpose registers view of the ARMv8-M system with TrustZone. Refer to the ARM Cortex-M33 Devices Generic User Guide for details about these registers.

Figure 2.4. Special-purpose Registers View with TrustZone

Image: https://documentation-service.arm.com/. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

The Combined Program Status Register (xPSR) consists of the Application Program Status Register (APSR), Interrupt Program Status Register (IPSR), and Execution Program Status Register (EPSR).

Some of the special-purpose registers are banked between Secure and Non-secure states. Special-purpose registers are not memory-mapped and can be accessed using Core Register Access Functions in CMSIS-Core (except for EPSR in xPSR).

Secure privileged software can also access the Non-secure interrupt masking registers (PRIMASK\_NS, FAULTMASK\_NS, and BASEPRI\_NS), CONTROL register (CONTROL\_NS), and stack limit registers (MSPLIM\_NS and PSPLIM\_NS) through Core Register Access Functions in CMSIS-Core.

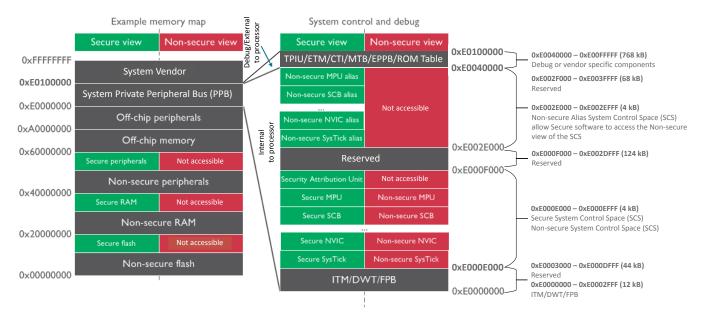

## 2.3.3 System Private Peripheral Bus (PPB)

The banking of registers is usually used to separate the Secure and Non-secure information of the system components inside the processor. The following figure shows the System Private Peripheral Bus (PPB) registers view of the ARMv8-M system with TrustZone. Refer to the ARM Cortex-M33 Devices Generic User Guide for details about the System PPB registers.

Figure 2.5. System Private Peripheral Bus (PPB) Registers View with TrustZone

# System components for debugging and trace operations (0xE0000000 to 0xE0002FFF):

- Instrumentation Trace Macrocell (ITM)

- · Data Watch point and Trace unit (DWT)

- Flash Patch and Breakpoint unit (FPB)

#### System Control Space (SCS):

- The registers in SCS address spaces are memory-mapped and can be accessed using pointers in software

- Secure SCS (0xE000E000 to 0xE000EFFF) Secure software using this address space to access the banked Secure SCS registers (e.g., SCB->CPUID)

- Non-secure SCS (0xE000E000 to 0xE000EFFF) Non-secure software using this address space to access the banked Non-secure SCS registers (e.g., SCB->CPUID)

- Non-secure alias SCS (0xE002E000 to 0xE002EFFF) Secure software using this address space to access the Non-secure SCS registers (e.g., SCB\_NS->CPUID)

The following table describes some core peripherals in the SCS and corresponding data structures defined in the CMSIS-Core header file to access the registers of core peripherals in two SCS address spaces.

| Core Peripheral                      | Data Structure for Secure and NS SCS | Data Structure for NS Alias SCS |

|--------------------------------------|--------------------------------------|---------------------------------|

| Implementation Control Block         | SCnSCB (0xE000E004)                  | SCnSCB_NS (0xE002E004)          |

| SysTick Timer                        | SysTick (0xE000E010)                 | SysTick_NS (0xE002E010)         |

| Nested Vectored Interrupt Controller | NVIC (0xE000E100)                    | NVIC_NS (0xE002E100)            |

| System Control Block                 | SCB (0xE000ECFC)                     | SCB_NS (0xE002ECFC)             |

| Memory Protection Unit               | MPU (0xE000ED90)                     | MPU_NS (0xE002ED90)             |

| Security Attribution Unit            | SAU (0xE000EDD0)                     | _                               |

| Debug Control Block                  | CoreDebug (0xE000EDF0)               | CoreDebug_NS (0xE002EDF0)       |

| Software Interrupt Generation        | STIR (0xE000EF00)                    | STIR_NS (0xE002EF00)            |

| Floating-Point Extension             | FPU (0xE000EF34)                     | FPU_NS (0xE002EF34)             |

#### Note:

- The SCB is a group of system control registers for the various usages below.

- · System Control Register (SCR) to configure processor low power mode

- Fault Status Register (xFSR) to provide fault status information

- · Vector Table Offset Register (VTOR) for vector table relocation

- The SAU register is accessible from the Secure state only.

- · The STIR register is not physically banked.

- · Core peripherals such as SysTick, SCB, and MPU are duplicated. One instance is Secure and the other one is Non-secure.

- Secure software can use the corresponding functions for ARMv8-M in CMSIS-Core to configure the Non-secure NVIC and SysTick through the Non-secure alias SCS.

# Debug or vendor specific components (0xE0040000 to 0xE00FFFFF):

- Optional debug components (e.g., ETM)

- External Private Peripheral Bus (EPPB) allows designers to add their own debug or vendor-specific components

- System ROM Table is a simple lookup table that enables debug tools to extract the addresses of debug and trace components

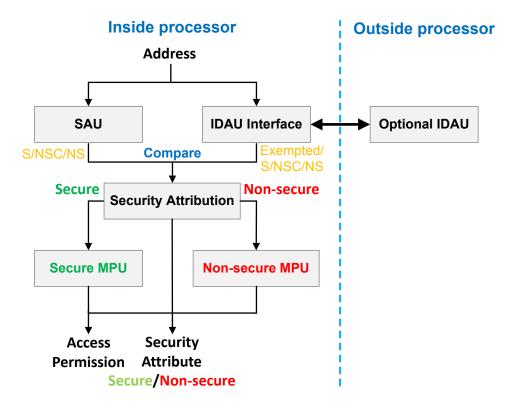

# 2.4 Secure Attribution Unit (SAU), Implementation Defined Attribution Unit (IDAU), and Memory Protection Unit (MPU)

Two units determine the security attribute of an address:

- 1. The internal programmable Secure Attribution Unit (SAU).

- The external Implementation Defined Attribution Unit (IDAU), through the IDAU interface, returns the security attribute and region number of an address.

Three possible configurations to define the security attribute of an address:

- 1. Internal SAU only

- 2. External IDAU only

- 3. A combination of the internal SAU and external IDAU

#### Note:

- · Series 2 devices use configuration 3.

- · IDAU in Series 2 devices is the External Secure Attribution Unit (ESAU).

The Memory Protection Unit (MPU) is a programmable unit that allows privileged software to define memory access permission. If the TrustZone is enabled, there can be up to two MPUs, one for Secure and one for Non-secure.

- The number of MPU regions for the Secure and the Non-secure MPU can be different.

- The MPU registers are memory-mapped and are placed in the System Control Space (SCS).

- Secure software can use the MPU Functions for ARMv8-M in CMSIS-Core to configure the Non-secure MPU through the Non-secure alias SCS (0xE002ED90 0xE002ED24).

| Software              | Non-secure MPU Registers | Secure MPU Registers    | MemManage Fault          |

|-----------------------|--------------------------|-------------------------|--------------------------|

| Non-secure privileged | 0xE000ED90 - 0xE000EDC4  | _                       | Non-secure MPU violation |

| Secure privileged     | 0xE002ED90 - 0xE002EDC4  | 0xE000ED90 - 0xE000EDC4 | Secure MPU violation     |

# 2.5 Exceptions and Interrupts

# 2.5.1 Type of Exceptions

The following table describes the types of exceptions in the TrustZone implemented system.

| Exception (IRQ) Number | Exception       | Туре         | Default State |

|------------------------|-----------------|--------------|---------------|

| 1 (—)                  | Reset           | Secure only  | Secure        |

| 2 (-14)                | NMI             | Configurable | Secure        |

| 3 (-13)                | HardFault       | Configurable | Secure        |

| 4 (-12)                | MemManage Fault | Banked       | Banked        |

| 5 (-11)                | BusFault        | Configurable | Secure        |

| 6 (-10)                | UsageFault      | Banked       | Banked        |

| 7 (-9)                 | SecureFault     | Secure only  | Secure        |

| 11 (-5)                | SVCall          | Banked       | Banked        |

| 12 (-4)                | DebugMonitor    | Configurable | Secure        |

| 14 (-2)                | PendSV          | Banked       | Banked        |

| 15 (-1)                | SysTick         | Banked       | Banked        |

| 16 - 495 (0 - 479)     | IRQ0 - IRQ479   | Configurable | Secure        |

#### Note:

- "Secure only" means the system exceptions can only trigger in the Secure state.

- "Configurable" means the system exceptions and interrupts can be configured to target either the Secure state or the Non-secure state

- Banked means the system exceptions can have Secure and Non-secure versions. Both can be triggered and executed independently and have different priority level settings.

## 2.5.2 Exception Priorities

It may cause a security issue if the Non-secure software uses high priority levels to mask the Secure interrupts. To avoid this issue, TrustZone introduces a programmable bit in the AIRCR register called PRIS (Prioritize Secure exception) for Secure software to prioritize, if needed, Secure exceptions and interrupts.

The AIRCR.PRIS is set to 0 out of reset, which means Secure and Non-secure exceptions/interrupts share the same configurable programmable priority level space (columns 2 and 3 in the following table). When the AIRCR.PRIS is set to 1, all Non-secure configurable exceptions/interrupts are placed in the lower half of the priority level space so that Secure exceptions/interrupts can potentially have higher priorities (columns 2 and 4 in the following table).

| Priority Value | Secure Priority | Non-secure Priority (PRIS = 0) | Non-secure Priority (PRIS = 1) |

|----------------|-----------------|--------------------------------|--------------------------------|

| 0              | 0               | 0 (0x00)                       | 128 (0x80)                     |

| 1              | 32              | 32 (0x20)                      | 144 (0x90)                     |

| 2              | 64              | 64 (0x40)                      | 160 (0xA0)                     |

| 3              | 96              | 96 (0x60)                      | 176 (0xB0)                     |

| 4              | 128             | 128 (0x80)                     | 192 (0xC0)                     |

| 5              | 160             | 160 (0xA0)                     | 208 (0xD0)                     |

| 6              | 192             | 192 (0xC0)                     | 224 (0xE0)                     |

| 7              | 224             | 224 (0xE0)                     | 240 (0xF0)                     |

**Note:** This table uses three bits (Bit [7:5]) of the group priority level (AIRCR.PRIGROUP) to limit the maximum number of preemption levels to 8. A lower priority value indicates a higher priority.

#### 2.5.3 Vector Tables

The following figure shows two vector tables for Secure and Non-secure exceptions and interrupts. The vector table offset is defined by a Vector Table Offset Register (VTOR at 0xE000ED08), which can only be programmed in the privileged state.

| Exception number | IRQ number | Secure Vector    | Non-secure Vector | Offset |

|------------------|------------|------------------|-------------------|--------|

| 495              | 479        | IRQ479           | IRQ479            | 0x7BC  |

|                  |            |                  |                   |        |

|                  | =          | 2                |                   | ¥ .    |

|                  |            |                  |                   | -      |

| 18               | 2          | IRQ2             | IRQ2              | 0x48   |

| 17               | 1          | IRQ1             | IRQ1              | 0x44   |

| 16               | 0          | IRQ0             | IRQ0              | 0x40   |

| 15               | -1         | SysTick _S       | SysTick_NS        | 0x3C   |

| 14               | -2         | PendSV_S         | PendSV_NS         | 0x38   |

| 13               |            | Reserved         | Reserved          | 0x30   |

| 12               | -4         | DebugMonitor     | DebugMonitor      |        |

| 11               | -5         | SVCall _S        | SVCall_NS         | 0x2C   |

| 10               |            |                  |                   |        |

| 9                |            | Reserved         | Reserved          |        |

| 8                |            |                  | Reserveu          |        |

| 7                | -9         | SecureFault      |                   | 0x1C   |

| 6                | -10        | UsageFault_S     | UsageFault_NS     | 0x18   |

| 5                | -11        | BusFault_S       | BusFault_NS       | 0x14   |

| 4                | -12        | MemManage_S      | MemManage_NS      | 0x10   |

| 3                | -13        | HardFault _S     | HardFault_NS      | 0x0C   |

| 2                | -14        | NMI_S            | NMI_NS            | 0x08   |

| 1                |            | Reset            |                   | 0x04   |

|                  |            | Initial SP value |                   |        |

Image: Vector Table. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

#### Note:

- The VTOR\_S defines the address of the Secure vector table in Secure memory, and the Secure Main Stack Pointer (MSP\_S) is the default stack for the Secure exception handler.

- The VTOR\_NS defines the address of the Non-secure vector table in Non-secure memory, and the Non-secure Main Stack Pointer (MSP\_NS) is the default stack for the Non-secure exception handler.

- Secure privileged software can access the VTOR\_NS using the Non-secure SCB alias (0xE002ED08).

- The System Control Space contains registers for the SysTick timer, NVIC, and SCB.

- The interrupt masking registers (PRIMASK, FAULTMASK, and BASEPRI) are banked between security states. The priority level space is shared between the Secure and the Non-secure world, setting an interrupt mask register on one side can block some, or all, of the exceptions on the other side.

- Interrupts (IRQ0 IRQ479) are defined as Secure by default. Each interrupt can be configured as Secure or Non-secure and is determined by the Interrupt Target Non-secure (NVIC\_ITNS) register, which is only programmable in the Secure software.

## 2.5.4 State Transitions in Exceptions and Interrupts

The following figure shows transitions between the processor states in ARMv8-M TrustZone.

Figure 2.6. State Transitions

Image (left): Switching-between-Secure-and-Non-secure-states. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

- 1. Secure Thread → Secure Handler or Non-secure Thread to Non-secure Handler

- · No security state transition.

- · The exception sequence is almost identical to the exception stacking mechanism of current Cortex-M processors.

- The Interrupt Service Routine (ISR) is executed in the current security state (either Secure or Non-secure).

- 2. Non-secure Thread  $\rightarrow$  Secure Handler or Non-secure Handler  $\rightarrow$  Secure Handler

- The transition from Non-secure to Secure state.

- · The exception sequence is almost identical to the exception stacking mechanism of current Cortex-M processors.

- · The ISR is executed in a Secure state.

- 3. Secure Thread → Non-secure Handler or Secure Handler → Non-secure Handler

- · The transition from Secure to Non-secure state.

- To avoid an information leak when transitioning from the Secure to Non-secure state. The processor automatically pushes all general-purpose registers into the Secure stack and erases the contents of all general-purpose registers before executing the Non-secure ISR. The processor pops the contents of all general-purpose registers from the Secure stack when returning from the Non-secure ISR (right side in Figure 2.6 State Transitions on page 12). It incurs a slightly longer interrupt latency.

- The ISR is executed in a Non-secure state.

- Secure Privileged Thread ↔ Non-secure Privileged Thread or Secure Unprivileged Thread ↔ Non-secure Unprivileged Thread

- The transition from Secure to Non-secure state or Non-secure to Secure state.

- · The Function calls and returns can be used when the privileged level remains the same.

**Note:** Subject to interrupt priority, there are no restrictions regarding whether a Non-secure or Secure interrupt can occur when the processor runs Non-secure or Secure code.

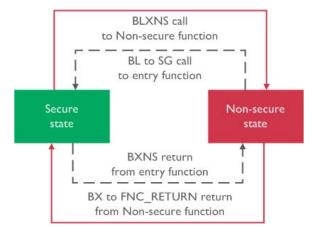

#### 2.6 Switching Between Secure and Non-secure States

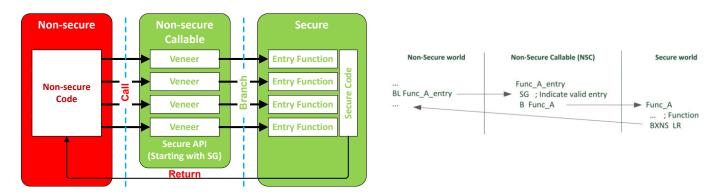

The TrustZone allows direct calling between Secure and Non-secure software. The following figure shows how to use an API function call to trigger security state transitions. The state transitions can also happen because of exceptions and interrupts.

Image: Switching-between-Secure-and-Non-secure-states. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

#### 2.6.1 Switching from Non-secure to Secure State

When the Non-secure program calls a Secure software, the first instruction must be a Secure Gateway (SG) instruction residing in Non-secure Callable memory. The Secure Gateway entry points (veneers) decouple the address of the SG instructions in the Non-secure Callable memory region from the rest of the Secure code. It can eliminate the risk of having inadvertent entry points when the Secure software contains a pattern that matches the opcode of the SG instruction.

Image (right): Whitepaper - ARMv8-M Architecture Technical Overview. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

The bit 0 of the Link Register (LR) is cleared to zero by sg instruction to indicate that returning from this function transits from Secure to Non-secure. The processor is still in the Non-secure state when the sg instruction is executed. The BXNS LR instruction is used when returning since a normal BX LR instruction interprets it as an unsupported execution mode change. A SecureFault exception is triggered if the processor returns to a Secure address. It prevents a hacker from calling a Secure API with a fake return address pointing to a Secure program location. If bit 0 of LR is 1, the BXNS LR instruction behaves like a normal BX LR. Therefore, Secure code can call a Secure API in the NSC region even it is not a usual practice.

| Program                    | Call Instruction | SG Instruction    | Return Instruction                   |

|----------------------------|------------------|-------------------|--------------------------------------|

| Non-secure call Non-secure | BL or BLX        | _                 | BX LR (Return to Non-secure state)   |

| Non-secure call Secure     | BL or BLX        | Clear bit 0 of LR | BXNS LR (Return to Non-secure state) |

| Secure call Secure         | BL or BLX        | Set bit 0 of LR   | BXNS LR (Return to Secure state)     |

To help software developers create Secure APIs in C/C++, the Cortex-M Security Extension (CMSE) defines a C function attribute called cmse\_nonsecure\_entry.

- GCC \_\_attribute\_\_((cmse\_nonsecure\_entry))

- IAR \_\_cmse\_nonsecure\_entry

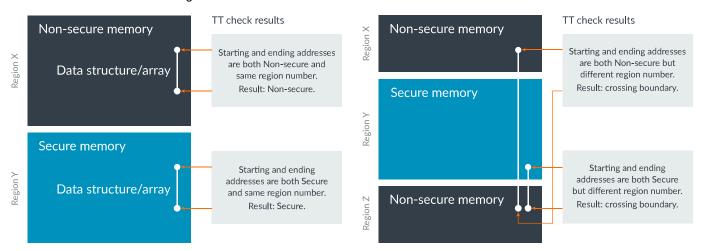

#### 2.6.2 Test Target (TT) Instruction

The software can use an ARMv8-M instruction called Test Target (TT) and the region number generated by the SAU or the IDAU to determine if a contiguous range of memory shares common security attributes and privilege levels.

The TT instruction returns the SAU/IDAU region number, security attributes (S/NS), and MPU region number after passing the start and end addresses of the memory range to the TT instruction. The software can determine whether the memory range has required security attributes and resides in the same region number.

Image: Test-target-instruction. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

This mechanism allows security checking at the beginning of the API service (instead of during the operation) to determine if the memory referenced by a pointer from Non-secure software points to the Non-secure address. It prevents Non-secure software from using those APIs in Secure software to access or modify Secure data.

To make these operations easier in a C/C++ programming environment, the Cortex-M Security Extension (CMSE) has defined a range of intrinsic functions for dealing with pointer checks with the TT instructions.

## 2.6.3 Switching from Secure to Non-secure State

When the Secure program calls a Non-secure software, the Secure program must use a BLXNS <reg> instruction to invoke the process. If bit 0 of the <reg> is 0, the processor must switch to the Non-secure state when branching to the target address. During the state transition, the return address and some processor state information are pushed onto the Secure stack, while the return address on the Link Register (LR) is set to a special value called FNC\_RETURN (0xFEFFFFFF).

The Non-secure function completes by performing a branch (BX LR) to the FNC\_RETURN address (bit 0 is 1 to indicate the function was called from the Secure state). It automatically triggers the unstacking of the actual return address from the Secure stack and returns to the calling function. The FNC\_RETURN hides the return address of the Secure program from the Non-secure software to avoid the leakage of any secret information. It also prevents Non-secure software from modifying the Secure return address stored in the Secure stack.

```

Non-secure

Func_B Return address push to ...

Secure stack, LR set to—BLXNS R0/* R0=address of Func_B with LSB =0 (NS)*/...

FNC_RETURN ...

Branch to FNC_RETURN triggers

BX LR unstacking of return address from Secure stack

```

Image: Switching-between-Secure-and-Non-secure-states. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

To help software developers declare Non-secure function pointers in C/C++, the Cortex-M Security Extension (CMSE) defines a C function attribute called <code>cmse\_nonsecure\_call</code>.

- GCC: \_\_attribute\_\_((cmse\_nonsecure\_call))

- IAR: \_\_cmse\_nonsecure\_call

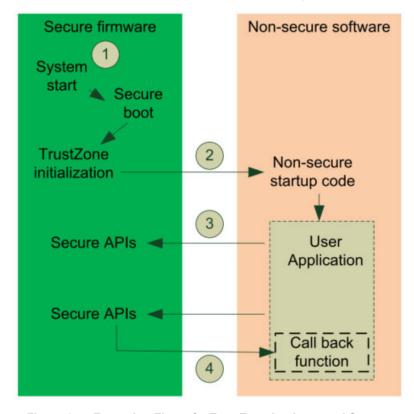

#### 2.7 Software Flow

The following figure describes a software flow example in a TrustZone implemented system.

Figure 2.7. Execution Flow of a TrustZone Implemented System

Image: Software Development in ARMv8-M Architecture. Copyright © 1995-2022 Arm Limited (or its affiliates). All rights reserved.

- 1. The system starts executing code in the Secure state after a power-on or reset (Secure boot).

- The Secure stack pointer (MSP\_S) is set from the address of the Secure vector table (VTOR\_S).

- The Secure Reset Handler pointed by the VTOR\_S is called.

- · Perform various initialization tasks such as C startup code.

- Place peripherals and associated interrupts in either Secure or Non-secure applications.

- · Program SAU/IDAU to partition the entire memory into Secure, Non-secure Callable, and Non-secure regions.

- Program the address of the Non-secure vector table (VTOR\_NS).

- Initialize the two first entries of the table for the Non-secure stack pointer (MSP\_NS) and Reset Handler to emulate a Non-secure reset.

- 2. The Secure firmware branches to the entry point (Reset Handler pointed by the VTOR\_NS) of the Non-secure application.

- · The Non-secure software has its Reset Handler.

- Perform various initialization tasks such as C startup code and hardware initialization (e.g., Non-secure peripherals).

- It does not conflict with initialization from the Secure code as the stack and heap spaces of Secure and Non-secure code are separated.

- 3. During the execution of Non-secure applications, the application could call Secure APIs through the Secure Gateway (SG) veneer in the Non-secure Callable region.

- 4. In some cases, Secure APIs might need to call Non-secure call-back functions (e.g., a hardware driver).

# 3. Bus Level Security (BLS)

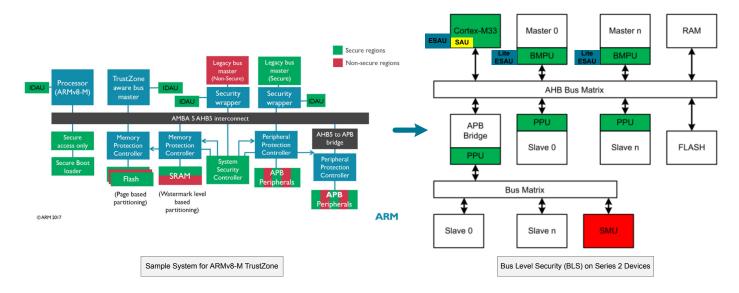

## 3.1 System Design

The following figure shows two system designs:

- The sample system contains an ARMv8-M processor and the required components to support TrustZone.

- Bus Level Security (BLS) on Series 2 devices implements the concepts introduced in the ARM TrustZone sample system. BLS enforces Secure and privileged programming models and uses security components (colored blocks) to configure the security attribute and privileged level of peripherals and Bus Masters.

Figure 3.1. ARMv8-M TrustZone Implementation

#### **ARMv8-M Processor**

The ARMv8M processor is TrustZone capable of Secure and Non-secure states. It has a dedicated internal SAU that is fully programmable up to 8 different memory regions. Out of reset, the processor is in a Secure state and every transaction is a Secure transaction.

ARMv8-M Processor in Series 2 devices is the Cortex-M33.

## **System Security Controller**

The system security controller is the central location for all security settings in the system. Each type of controller, IDAU, and wrapper receives its security configuration and bus response configuration from this block.

System Security Controller in Series 2 devices is the Security Management Unit (SMU).

# Implementation Defined Attribution Unit (IDAU)

The IDAU generates the security attribute for a given address. All IDAUs in the system have the same memory partitioning. The IDAU is intended only for ARMv8-M cores and utilizes the entire IDAU interface for the core. The lite IDAU uses only the Secure and Non-secure interface from the IDAU and is intended for Non-ARMv8-M Bus Masters.

IDAU in Series 2 devices is the External Secure Attribution Unit (ESAU).

## **Security Wrapper**

The Security Wrapper gives a legacy Bus Master the ability to drive security attribution. The security wrapper outputs the transaction address to the lite IDAU which returns the security attribute of the address. If the wrapper is configured as Non-secure, any transactions to a Secure address are blocked.

Security Wrapper in Series 2 devices is the Bus Master Protect Unit (BMPU).

# **Memory Protection Controller (MPC)**

MPC has a security configuration for a per block of memory or memory above and below the watermark. If the security attribute of the block or memory region does not match the security attribute of the address, the transaction is blocked. This controller is used in a system that alias RAM or flash memory locations. This controller is not needed when the memory region size is programmable in an IDAU.

Series 2 devices have a programmable flash and RAM region in the ESAU (equivalent to IDAU) and are not implementing this block.

# **Peripheral Protection Controller (PPC)**

PPC has a security configuration for every peripheral. If the security attribute of the selected peripheral does not match the security attribute of the address, the transaction is blocked. This controller is used in systems that alias the peripheral memory locations.

PPC in Series 2 devices is the Peripheral Protection Unit (PPU).

Hardware security is now extended to the peripheral bus system of the processor. Each component on the bus can verify and propagate the security level for each bus operation. The following sections describe the individual security component for BLS on Series 2 devices.

#### 3.2 Security Management Unit (SMU)

The SMU is the only user-facing block in the BLS architecture and houses all the configuration and status for the ESAUs, BMPUs, and PPUs.

- · Thirteen memory regions (ESAU)

- · Per Bus Master privileged and security attribute (BMPU)

- Interrupt flag for Bus Master security fault (fault table in BMPU section)

- Per peripheral privileged and security attribute (PPU)

- · Interrupt flags for privileged, security, and instruction peripheral access faults (fault tables in PPU section)

- Separate Secure and Privileged IRQ

The SMU configurations can be locked down and protected from runaway code. The SMU\_LOCK register resets to UNLOCK. Any write other than the unlock code (0xACCE55) locks all SMU registers from further updates. The SMU\_STATUS register contains a SMULOCK bit-field with the current lock state of the SMU.

The SMU\_M33CTRL register can lock down internal security and privileged configurations below.

- Cortex-M33 SAU

- · Non-secure MPU

- Secure MPU

- Non-secure Vector Table Offset Register (VTOR)

- · Secure AIRCR register

Interrupt flags in the SMU\_IF register can generate a Secure or Privileged interrupt in the table below when its corresponding interrupt enable bit in the SMU\_IEN register is set and IRQn is enabled.

| Enable Bit in SMU_IEN Register | IRQn                | Interrupt Handler           |

|--------------------------------|---------------------|-----------------------------|

| BMPUSEC, PPUSEC                | SMU_SECURE_IRQn     | SMU_SECURE_IRQHandler()     |

| PPUPRIV, PPUINST               | SMU_PRIVILEGED_IRQn | SMU_PRIVILEGED_IRQHandler() |

Each interrupt flag in the SMU\_IF register can be cleared by writing 1 to the corresponding bit of the SMU\_IF\_CLR register.

## 3.3 External Secure Attribution Unit (ESAU)

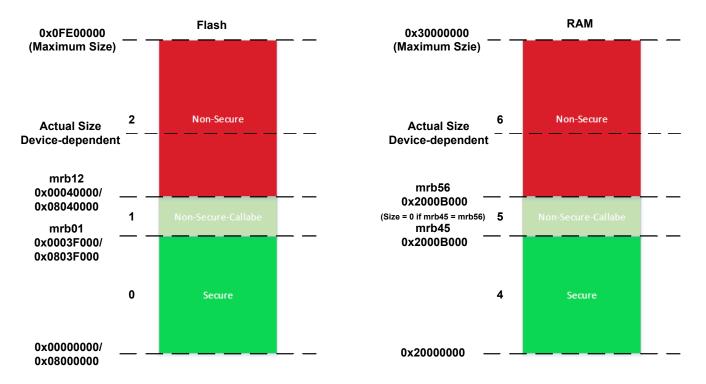

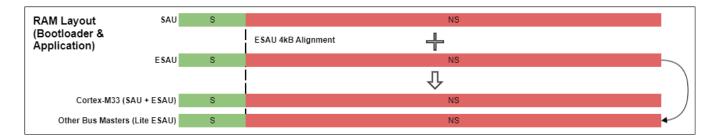

The ESAU is responsible for determining the memory region and security attribute of a given address. Referring to Figure 3.1 ARMv8-M TrustZone Implementation on page 16, the Cortex-M33 interfaces with an ESAU and the BMPUs of other Bus Masters interface with lite ESAUs to determine the security attribute of all transactions. The following figure describes the security attributes of different memory regions defined by the ESAU on Series 2 devices.

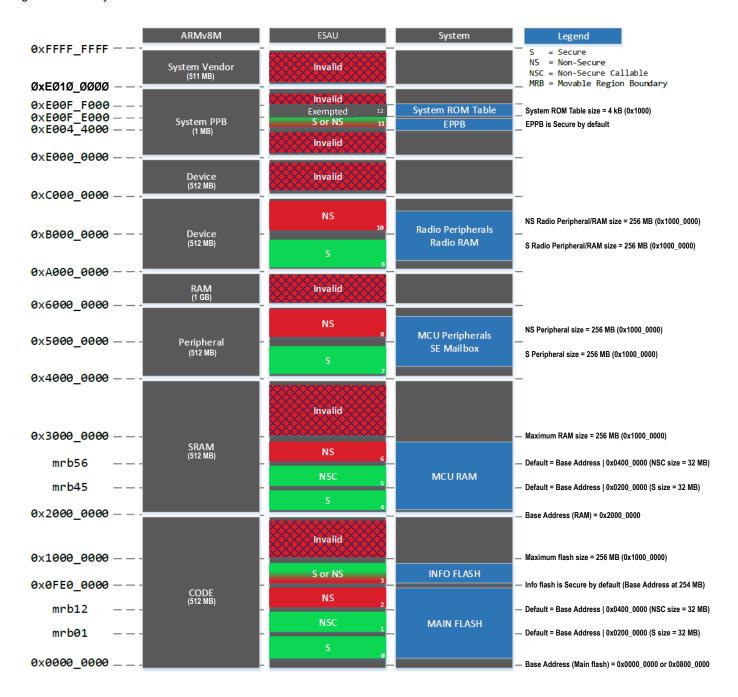

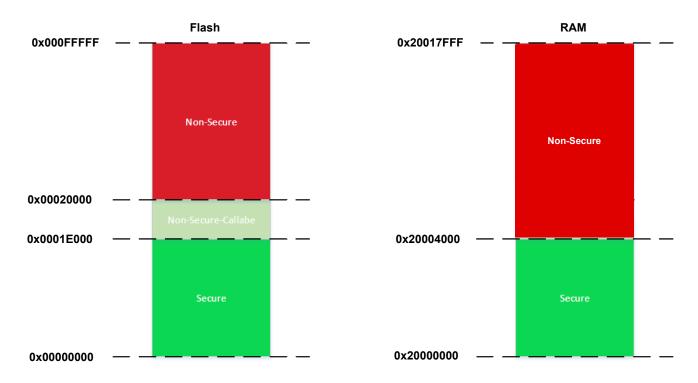

Figure 3.2. System Memory Map of Series 2 Device with TrustZone

#### Note:

- For Series 2 devices with base address 0x08000000 in region 0, the memory address from 0x0 to 0x07FFFFFF is an invalid region.

- · The invalid regions are deemed as Secure.

- The NSC and Exempted attributes are only available to the ESAU, and all lite ESAUs in the system view these attributes as Secure.

The ESAU divides the memory map into 13 memory regions and has a maximum of 6 Non-secure regions.

- Four Movable Region Boundaries (MRBs) determine the size of 6 regions.

- · Two regions have configurable security attributes.

- Each memory region consists of a base address that specifies the start of the region and a limit address that specifies the end of the region plus one (+ 1).

- The address is valid if it falls between the base (≥ base) and limit (< limit) of a region.</li>

- · If the memory region is not defined, it is deemed invalid and Secure.

The MRBs distinguish the Secure, Non-secure Callable, and Non-secure regions in flash and RAM. The two configurable regions determine if the Info flash and Cortex-M33 EPPB regions are Secure or Non-secure. The MRBs have a specific programming sequence. Any misprogramming results in a SMUPRGERR in the SMU\_STATUS register.

#### **ARMv8-M CODE Regions**

- Regions 0, 1, and 2 are in the Main space of flash. Region 3 is the info space of flash.

- The mrb01 (ESAUMRB01 in SMU\_ESAURMBR01 register) determines the end of region 0 and the start of region 1.

- The mrb12 (ESAUMRB12 in SMU\_ESAURMBR12 register) determines the end of region 1 and the start of region 2.

- · The size of region 3 is device-dependent.

- Three regions' security attributes are static, and one region is configurable. Region 0 is always Secure, region 1 is always Non-secure Callable, and region 2 is always Non-secure. Region 3 is configurable as either Secure or Non-secure (ESAUR3NS in SMU\_ESAURTYPESO register, default is secure after reset).

- Sizes of regions 0, 1, and 2 are adjusted in 4 kB increments with the lower 12 bits of ESAUMRB## in SMU\_ESAURMBR## ignored.

- The Secure region can be set to size 0 when mbr01 = base address of region 0.

- The Non-secure Callable regions can be set to size 0 when mbr01 = mbr12.

- The default value of mbr01 is equal to base address + 0x02000000, so the size of region 0 is 32 MB. Out of reset, all flash is Secure since all Series 2 devices have less than 32 MB of flash.

| Region | Memory     | Base Address                       | Limit Address                      | Security Attribute   |

|--------|------------|------------------------------------|------------------------------------|----------------------|

| 0      | Main flash | 0x00000000 or 0x08000000           | (0x00000000 or 0x08000000)   mbr01 | Secure               |

| 1      | Main flash | (0x00000000 or 0x08000000)   mbr01 | (0x00000000 or 0x08000000)   mbr12 | Non-secure Callable  |

| 2      | Main flash | (0x00000000 or 0x08000000)   mbr12 | 0x0FE00000                         | Non-secure           |

| 3      | Info flash | 0x0FE0000                          | 0x10000000                         | Secure or Non-secure |

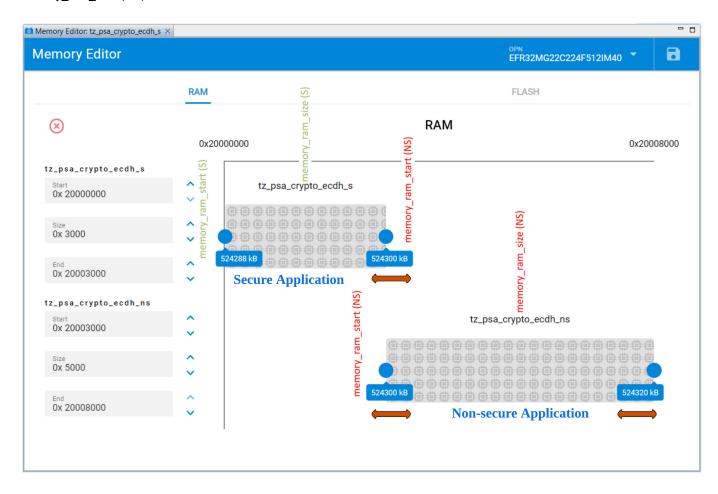

#### **ARMv8-M RAM Regions**

- Regions 4, 5, and 6 cover the entire available RAM in the device.

- The mrb45 (ESAUMRB45 in SMU\_ESAURMBR45 register) determines the end of region 4 and the start of region 5.

- The mrb56 (ESAUMRB56 in SMU\_ESAURMBR56 register) determines the end of region 5 and the start of region 6.

- All three regions' security attributes are static. Region 4 is always Secure, region 5 is always Non-secure Callable, and region 6 is always Non-secure.

- Sizes of all three regions are adjusted in 4 kB increments with the lower 12 bits of ESAUMRB## in SMU\_ESAURMBR## ignored.

- The Secure region can be set to size 0 when mbr45 = base address of region 4.

- The Non-secure Callable region can be set to size 0 when mbr45 = mbr56.

- The default value of mbr45 is equal to 0x02000000, so the size of region 4 is 32 MB. Out of reset, all RAM is Secure since all Series 2 devices have less than 32 MB of RAM.

| Region | Memory | Base Address       | Limit Address      | Security Attribute  |

|--------|--------|--------------------|--------------------|---------------------|

| 4      | SRAM   | 0x20000000         | 0x20000000   mbr45 | Secure              |

| 5      | SRAM   | 0x20000000   mbr45 | 0x20000000   mbr56 | Non-secure Callable |

| 6      | SRAM   | 0x20000000   mbr56 | 0x30000000         | Non-secure          |

#### **ARMv8-M Peripheral Regions**

- These regions are aliases to the chip peripherals and SE mailbox (a device with HSE).

- · Both regions have a fixed size.

- Both regions' security attributes are static. Region 7 is always Secure, and region 8 is always Non-secure.

| Region | Memory           | Base Address | Limit Address | Security Attribute |

|--------|------------------|--------------|---------------|--------------------|

| 7      | Chip Peripherals | 0x40000000   | 0x50000000    | Secure             |

| 8      | Chip Peripherals | 0x50000000   | 0x60000000    | Non-secure         |

## **ARMv8-M Device Regions**

- · These regions are aliases to all radio peripherals and radio RAM.

- · Both regions have a fixed size.

- Both regions' security attributes are static. Region 9 is always Secure, and region 10 is always Non-secure.

- From the perspective of the device bus system, the radio is one peripheral that is either Secure or Non-secure. So any Bus Master accessing the radio needs to know the security attribute of the radio. From the perspective of the radio, all of its radio bus peripherals are accessible regardless of the security attribute. However, the radio needs to know the security attribute of chip bus peripherals to access them through the correct alias.

| Region | Memory            | Base Address | Limit Address | Security Attribute |

|--------|-------------------|--------------|---------------|--------------------|

| 9      | Radio Peripherals | 0xA0000000   | 0xB0000000    | Secure             |

| 10     | Radio Peripherals | 0xB0000000   | 0xC0000000    | Non-secure         |

## ARMv8-M System Private Peripheral Bus (PPB) Regions

- · Both regions have a fixed size.

- Region 11 is the Cortex-M33 EPPB memory region and is configurable as either Secure or Non-secure (ESAURTINS in SMU\_ESAURTYPES1 register, default is secure after reset). It is important to note that the Cortex-M33 core is the only Bus Master that sees these memory regions. All other Bus Masters in the system do not have access to the System PPB, and it is an invalid region.

- Region 12 has a static security attribute of Exempted. It means that the Cortex-M33 core allows the transaction in all cases. It permits debuggers to read the system ROM Table regardless of the state of the Cortex-M33 core.

| Region | Memory           | Base Address | Limit Address | Security Attribute   |

|--------|------------------|--------------|---------------|----------------------|

| 11     | ЕРРВ             | 0xE0044000   | 0xE00FE000    | Secure or Non-secure |

| 12     | System ROM Table | 0xE00FE000   | 0xE00FF000    | Exempted             |

#### Note:

- The regions in flash (0/1/2) and RAM (4/5/6) can only create in the order of Secure, Non-secure Callable, and Non-secure.

- The ESAU and lite ESAUs handle the transactions of Bus Masters and must have consistent security attribute mapping. Therefore, configurations in the SMU registers apply to ESAU and lite ESAUs.

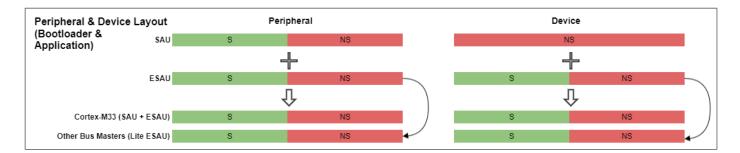

- Unlike other Bus Masters using BMPU and lite ESAU, merging the address lookup results from the internal SAU and ESAU determines the security attribute of the Cortex-M33 transaction.

| Bus Master | Security Attribution |

|------------|----------------------|

| Cortex-M33 | SAU and ESAU         |

| Other      | Lite ESAU            |

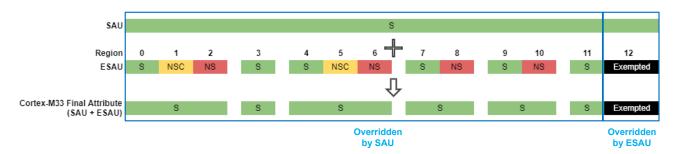

#### 3.4 Security Attribution Unit

In Series 2 devices, the combination of the integrated SAU in the Cortex-M33 processor and an ESAU determine the security attribute of a Cortex-M33 transaction.

The SAU consists of several programmable registers. These registers are placed in the System Control Space (SCS) and are only accessible from the Secure privileged state.

- SAU Control Register (SAU\_CTRL) The SAU is disabled after RESET

- SAU Type Register (SAU\_TYPE) Indicates the number of available regions (read-only)

- SAU Region Number Register (SMU\_RNR) Assigns a region number

- SAU Region Base Address Register (SAU->RBAR) Configures selected region base address

- SAU Region Limit Address Register (SAU->RLAR) Configures selected region limit address and security attribute (NSC or NS), enable or disable the region

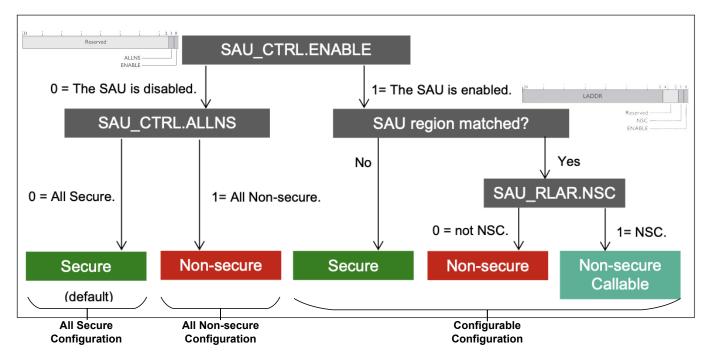

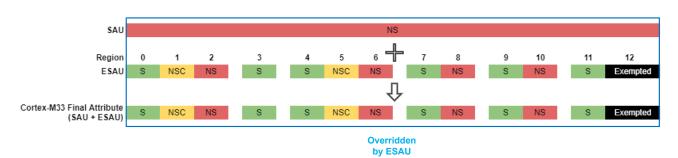

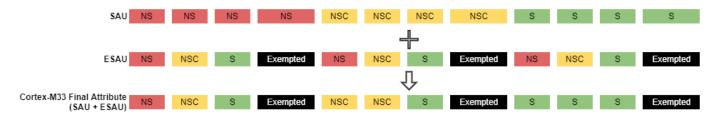

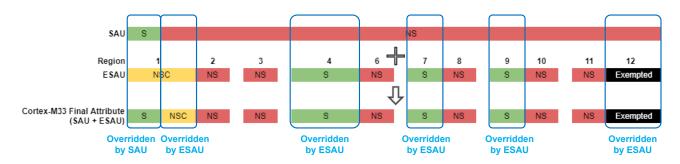

The following figure shows three different SAU configurations for determining the security attribute of a Cortex-M33 transaction.

Figure 3.3. Configuration of SAU\_CTRL Register

#### Note:

- · All address ranges after RESET in SAU are Secure by default.

- The SAU can configure a 32 bytes aligned region as Non-secure or Non-secure Callable. Any address not defined in the SAU defaults to Secure.

- An ESAU can configure or hard-code a region as Secure, Non-secure Callable, Non-secure, or Exempted. An Exempted region enables Non-secure debuggers to access debugging components and establish a debug connection to the processor before the SAU is configured.

- The processor determines the final attribute of the address based on the higher security attribute (Exempted > S > NSC > NS) from

either the SAU or the ESAU.

## 3.4.1 All Secure Configuration

Highlights:

- · SAU is disabled.

- ALLNS bit in the SAU Control register is clear.

- The whole memory is in a Secure state (highest security attribute apart from Exempted).

- All Cortex-M33 transactions in this configuration are Secure or Exempted and give the Cortex-M33 access to all memory locations through either the Secure or Non-secure alias after RESET.

It is up to the boot procedure in a Secure state to keep the current configuration or use other configurations once the boot process is complete.

# 3.4.2 All Non-secure Configuration

Highlights:

- · SAU is disabled.

- · ALLNS bit in the SAU Control register is set.

- · The whole memory is in a Non-secure state (lowest security attribute).

- · Therefore the ESAU configuration determines the security attribute of all Cortex-M33 transactions.

· Except for the SAU\_CTRL register, this configuration does not require programming on other SAU registers.

## 3.4.3 Configurable Configuration

#### Highlights:

- · SAU is enabled.

- ALLNS bit in the SAU Control register can be 0 or 1 (do not care).

- The NSC bit on the SAU\_RLAR register determines the security attribute of an address as Non-secure or Non-secure Callable if an address matches an SAU region.

- The security attribute of an address is Secure by default if the address does not match any SAU region.

- · This configuration programs SAU\_RNR, SAU\_RBAR, and SAU\_RLAR registers to correlate the Non-secure regions in ESAU.

- The SAU or ESAU overrides the attribute to a higher security level if any security attribute mismatch occurs in a memory region.

• The following figure is an example of a configurable configuration with the size of ESAU regions 0 and 5 are set to zero.

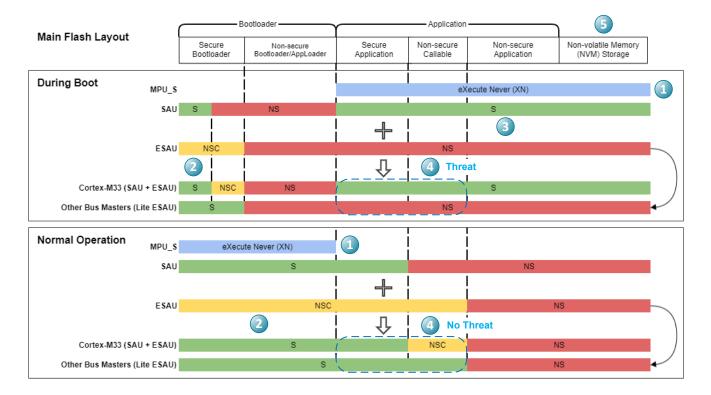

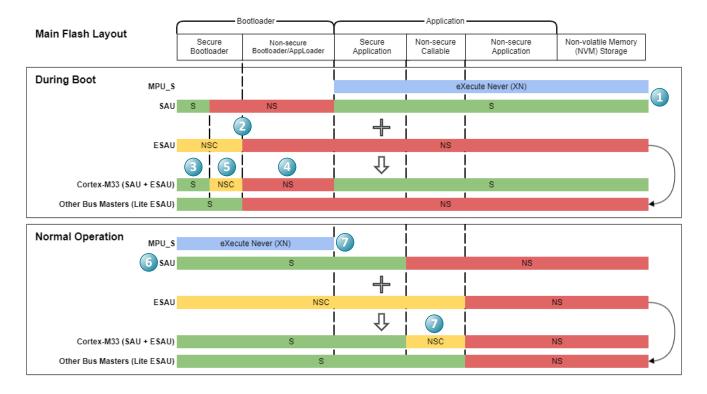

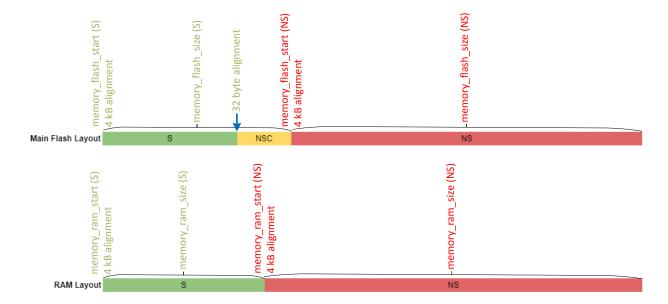

**Note:** The Cortex-M33 has an internal SAU that defaults all undefined addresses to Secure if enabled. If the Secure regions do not align between the Cortex-M33 (SAU + ESAU) and other Bus Masters (lite ESAU), the Cortex-M33 treats a memory region as Secure while other Bus Masters treat it as Non-secure. It can lead to the leaking of secure data if the Cortex-M33 stores secure data in what other Bus Masters think is a Non-secure area (Figure 5.1 Main Flash Layout on page 34).

#### 3.5 Bus Master Protection Unit (BMPU)

The BMPU is a security wrapper used for assigning a Bus Master specific security and privileged states. Referring to Figure 3.1 ARMv8-M TrustZone Implementation on page 16, the BMPU generally lies between the Bus Master and the Advanced High-performance Bus (AHB) Matrix. BMPU interfaces with a lite ESAU to determine the security attribute of all Bus Master transactions.

The registers below in SMU configure the security and privileged state of a Bus Master. The Bus Masters in group 0 are device-dependent. Out of reset, each Bus Master is Secure and privileged.

| Register      | Description                                                                                |

|---------------|--------------------------------------------------------------------------------------------|

| SMU_BMPUPATD0 | Bitfields (privileged if set) for privileged attribute configuration on Bus Master group 0 |

| SMU_BMPUSATD0 | Bitfields (Secure if set) for security attribute configuration on Bus Master group 0       |

**Note:** The Bus Master privileged attribute only applies to peripheral accesses. Flash and RAM accesses ignore the privileged attribute of the Bus Master.

The BMPU generates a security fault when the security attribute of the bus transaction is Secure, and the security attribute (SMU\_BMPUSATD0) for the BMPU is configured as Non-secure.

Below is the security fault table that shows how the security attribute on the bus is driven based on the lite ESAU attribute and the BMPU security configuration. The interrupt is triggered if BMPUSEC in SMU\_IEN is set and the SMU\_SECURE\_IRON is enabled.

| Lite ESAU Attribute | Secure Bus Master | Non-secure Bus Master |

|---------------------|-------------------|-----------------------|

| Non-secure          | Non-secure        | Non-secure            |

| Secure              | Secure            | FAULT                 |

Upon a BMPU fault, the registers in SMU below notify that a BMPU security fault occurred and on which Bus Master. The registers also identify the offending fault address. If a fault is detected, the response is Read As Zero (RAZ) or Write Ignored (WI) and the corresponding interrupt flag is set in the SMU\_IF register. The values in SMU\_BMPUFS and SMU\_BMPUFSADDR do not change until the BMPU fault (BMPUSEC) in the SMU\_IF register is cleared by software.

| Register       | Bitfield       | Fault                                         |

|----------------|----------------|-----------------------------------------------|

| SMU_IF         | BMPUSEC        | Security Fault if set                         |

| SMU_BMPUFS     | BMPUFSMASTERID | ID of the Bus Master that triggered the fault |

| SMU_BMPUFSADDR | BMPUFSADDR     | Access address that triggered the fault       |

Note: No privileged fault is generated because all the other Bus Masters in the system do not drive the privileged attribute.

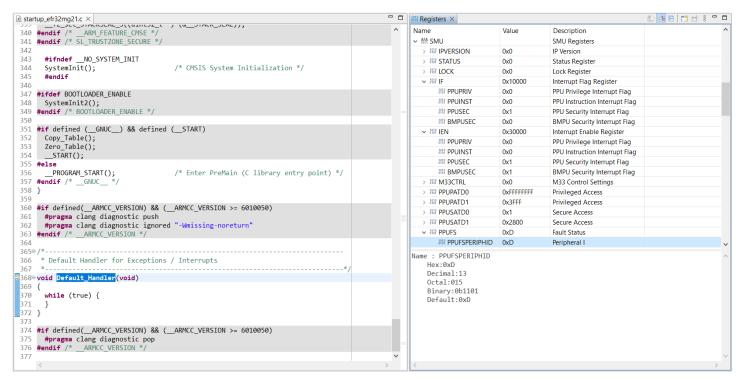

#### 3.6 Peripheral Protection Unit (PPU)

The PPU is a security wrapper used for assigning a Bus Slave peripheral specific security and privileged states. Referring to Figure 3.1 ARMv8-M TrustZone Implementation on page 16, the PPU comes in the form of a PPU in Advanced High-performance Bus (AHB) and a PPU in Advanced Peripheral Bus (APB).

- The PPU AHB generally lies between the Bus Matrix and an AHB Bus Slave peripheral.

- The PPU APB lies between the output of an AHB to APB bridge and all of the APB Slaves on that APB bus.

The registers below in SMU configure the security and privileged state of a peripheral. The peripherals in groups 0 and 1 are device-dependent. Out of reset, each peripheral is Secure and privileged. While each peripheral in address 0x40000000 (region 7) or 0x50000000 (region 8) can be configured independently, the radio subsystem in 0xA0000000 (region 9) or 0xB0000000 (region 10) is configured as a unit.

| Register     | Description                                                                             |

|--------------|-----------------------------------------------------------------------------------------|

| SMU_PPUPATD0 | Bitfields (privileged if set) for privileged access configuration on peripheral group 0 |

| SMU_PPUPATD1 | Bitfields (privileged if set) for privileged access configuration on peripheral group 0 |

| SMU_PPUSATD0 | Bitfields (Secure if set) for security access configuration on peripheral group 0       |

| SMU_PPUSATD1 | Bitfields (Secure if set) for security access configuration on peripheral group 1       |

The PPU can generate three types of faults:

1. Privileged faults occur on unprivileged transactions to privileged peripherals. Below is the privileged fault table that shows when a privileged fault occurs based on the PPU peripheral privileged configuration and the bus transaction privileged attribute. The interrupt is triggered if PPUPRIV in SMU\_IEN is set and the SMU\_PRIVILEGED\_IRQn is enabled.

| Bus Attribute | Privileged Peripheral | Unprivileged Peripheral |

|---------------|-----------------------|-------------------------|

| Privileged    | SUCCESS               | SUCCESS                 |

| Unprivileged  | FAULT                 | SUCCESS                 |

2. Security faults occur on Secure transactions to Non-secure peripherals and Non-secure transactions to Secure peripherals. Below is the security fault table that shows when a security fault occurs based on the PPU Peripheral security configuration and the bus transaction security attribute. The interrupt is triggered if PPUSEC in SMU\_IEN is set and the SMU\_SECURE\_IRQn is enabled.

| Bus Attribute | Secure Peripheral | Non-secure Peripheral |

|---------------|-------------------|-----------------------|

| Secure        | SUCCESS           | FAULT                 |

| Non-secure    | FAULT             | SUCCESS               |

3. Instruction faults occur on any transaction marked as an instruction fetch. Below is the instruction fault table that shows when a PPU instruction fault occurs based on the bus transaction instruction attribute. The interrupt is triggered if PPUINST in SMU\_IEN is set and the SMU\_PRIVILEGED\_IRQn is enabled.

| Bus Attribute | PPU Output |

|---------------|------------|

| Instruction   | FAULT      |

| Data          | SUCCESS    |

Upon a PPU fault, the registers below in SMU notifies which PPU fault occurred and on which peripheral. If a fault is detected, the response is Read As Zero (RAZ) or Write Ignored (WI) and set the corresponding interrupt flag in the SMU\_IF register. The values in SMU\_IF and SMU\_PPUFS do not change until all PPU faults in the SMU\_IF register are cleared by software.

| Register  | Bitfield      | Fault                                      |

|-----------|---------------|--------------------------------------------|

| SMU_IF    | PPUPRIV       | Privilege Fault if set                     |

| SMU_IF    | PPUSEC        | Security Fault if set                      |

| SMU_IF    | PPUINST       | Instruction Fault if set                   |

| SMU_PPUFS | PPUFSPERIPHID | ID of the peripheral that caused the fault |

# 3.7 Compatibility

Secure software usually controls the SYSCFG and SMU peripherals to prevent Non-secure software from changing critical configurations in the Secure domain. It requires switching between Secure and Non-secure states when Non-secure software wants to update the registers in these peripherals. Therefore dedicated registers for Non-secure access are added to SYSCFG and SMU peripherals on newer Series 2 devices.

## 3.7.1 System Configuration (SYSCFG)

Except for EFR32xG21 devices, the following tables apply to all Series 2 devices.

Table 3.1. Dedicated Bitfield to Configure Access for Non-secure SYSCFG Registers

| Bitfield (Register)        | Description                                                                              |

|----------------------------|------------------------------------------------------------------------------------------|

| SYSCFGCFGNS (SMU_PPUPATD0) | Bitfields (privileged if set) for privileged access configuration on NS SYSCFG registers |

| SYSCFGCFGNS (SMU_PPUSATD0) | Bitfields (Secure if set) for security access configuration on NS SYSCFG registers       |

Note: Reset SYSCFGCFGNS bit in SMU\_PPUSATD0 to allow Non-secure software to access NS SYSCFG registers.

Table 3.2. Dedicated SYSCFG Registers for Non-secure State

| SYSCFG Non-secure Registers | Description                           |

|-----------------------------|---------------------------------------|

| SYSCFG_CFGNS_CFGNSTCALIB    | NS SysTick calibration value register |

| SYSCFG_CFGNS_ROOTNSDATA0    | NS root data register 0               |

| SYSCFG_CFGNS_ROOTNSDATA0    | NS root data register 1               |

# 3.7.2 Security Management Unit (SMU)

Except for EFR32xG21 devices, the following tables apply to all Series 2 devices.

Table 3.3. Dedicated Bitfield to Configure Access for Non-secure SMU Registers

| Bitfield (Register)     | Description                                                                           |

|-------------------------|---------------------------------------------------------------------------------------|

| SMUCFGNS (SMU_PPUPATD1) | Bitfields (privileged if set) for privileged access configuration on NS SMU registers |

| SMUCFGNS (SMU_PPUSATD1) | Bitfields (Secure if set) for security access configuration on NS registers           |

Note: Reset SMUCFGNS bit in SMU\_PPUSATD1 to allow Non-secure software to access NS SMU registers.

The SMU\_CFGNS register file is for the TrustZone Non-secure state and has its register lock (NSLOCK). It allows hardware to maintain the privileged assignments for the NS state. The privileged configuration within the NS state is the same as the Secure state, except it has an "NS" to differentiate the registers.

Table 3.4. Dedicated SMU Registers for Non-secure State

| SMU Non-secure Registers | Description                                                                                   |

|--------------------------|-----------------------------------------------------------------------------------------------|

| SMU_CFGNS_NSSTATUS       | Lock status of SMU_CFGNS registers                                                            |

| SMU_CFGNS_NSLCOK         | Lock and unlock the SMU_CFGNS registers                                                       |

| SMU_CFGNS_NSIF           | Interrupt flags for NS privilege (PPUNSPRIVIF) and instruction (PPUNSINSTIF) faults           |

| SMU_CFGNS_NSIEN          | Interrupt enable flags for NS privilege (PPUNSPRIVIEN) and instruction (PPUNSINSTIEN) faults  |

| SMU_CFGNS_PPUNSPATD0     | Bitfields (privileged if set) for NS privileged access configuration on peripheral group 0    |

| SMU_CFGNS_PPUNSPATD1     | Bitfields (privileged if set) for NS privileged access configuration on peripheral group 1    |

| SMU_CFGNS_PPUNSFS        | ID (PPUFSPERIPHID) of the NS peripheral that caused the fault                                 |

| SMU_CFGNS_BMPUNSPATD0    | Bitfields (privileged if set) for privileged attribute configuration on NS Bus Master group 0 |

Table 3.5. Fault Statuses Only for Secure State

| Bitfield (Register)       | Description                                   |

|---------------------------|-----------------------------------------------|

| PPUPRIV (SMU_IF)          | Fault status now limited only to Secure state |

| PPUINST (SMU_IF)          | Fault status now limited only to Secure state |

| PPUPRIV (SMU_IEN)         | Fault status now limited only to Secure state |

| PPUINST (SMU_IEN)         | Fault status now limited only to Secure state |

| PPUFSPERIPHID (SMU_PPUFS) | Fault status now limited only to Secure state |

Table 3.6. Dedicated SMU Interrupt for Non-secure State

| Interrupt                      | Description                                                                                                                                                                                                                                                                                                       |

|--------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SMU_NS_PRIVILEGED_IRQHandler() | An interrupt flag in the SMU_CFGNS_NSIF register can generate an NS privileged interrupt when its corresponding interrupt enable bit in the SMU_CFGNS_NSIEN register is set and SMU_NS_PRIVILEGED_IRQn is enabled, and in which the peripheral (ID) that triggers the fault is in the SMU_CFGNS_PPUNSFS register. |

# 4. Secure and Privileged Programming Model

The implementation of BLS on Series 2 devices, both flash and RAM, use a programmable watermark to delineate Secure, Non-secure Callable, and Non-secure regions. On the other hand, peripherals exist in both a Secure and Non-secure alias of memory.

#### 4.1 BLS SMU Programming

## 4.1.1 Enabling SMU Clock

Except for the EFR32xG21 devices, all Series 2 devices enable the SMU clock in CMU before programming the SMU registers.

```

#if (_SILICON_LABS_32B_SERIES_2_CONFIG > 1)

CMU->CLKEN1_SET = CMU_CLKEN1_SMU;

#endif

```

#### 4.1.2 Cortex-M33 Lock Control

The Cortex-M33 security and privileged configurations can be locked by programming the SMU\_M33CTRL register.

```

// Lock Secure MPU configuration

SMU->M33CTRL |= SMU_M33CTRL_LOCKSMPU;

```

#### 4.1.3 Locking SMU Configuration

Th entire SMU configuration can be locked down to avoid runaway code. Below is an example of how to lock and unlock the SMU.

```

uint32_t lock_status;

// Lock Down SMU

SMU->LOCK = ~SMU_LOCK_SMULOCKKEY_UNLOCK;

// Grab Lock Status

lock_status = (SMU->STATUS & _SMU_STATUS_SMULOCK_MASK) >> _SMU_STATUS_SMULOCK_SHIFT;

// Unlock SMU

SMU->LOCK = SMU_LOCK_SMULOCKKEY_UNLOCK;

```

# 4.1.4 Interrupt Control

Each interrupt flag in SMU\_IF can generate an interrupt when its corresponding interrupt enable flag in the SMU\_IEN register is set. Each interrupt flag can be cleared by writing the clear alias of the SMU\_IF register.

```

// Clear and enable the SMU PPUSEC and BMPUSEC interrupt

NVIC_ClearPendingIRQ(SMU_SECURE_IRQn);

SMU->IF_CLR = SMU_IF_PPUSEC | SMU_IF_BMPUSEC;

NVIC_EnableIRQ(SMU_SECURE_IRQn);

SMU->IEN = SMU_IEN_PPUSEC | SMU_IEN_BMPUSEC;

```

#### 4.2 BLS ESAU Programming

## 4.2.1 Region Types

The SMU\_ESAURTYESn registers are used to configure memory regions with a specific security attribute. All configurable memory regions reset to Secure. Below is an example of programming regions 3 and 11 to Non-secure.

```

// Region 3 (Info flash) is Non-secure

SMU->ESAURTYPES0 = SMU_ESAURTYPES0_ESAUR3NS;

// Region 11 (EPPB) is Non-secure

SMU->ESAURTYPES1 = SMU_ESAURTYPES1_ESAUR11NS;

```

#### 4.2.2 Region Sizes

The code and figure below highlight how to program the Movable Region Boundaries (MRBs) of ESAU.

```

// ESAU region 0/1/2 programming

// Boundary01 at 252kB and Boundary12 at 256kB

SMU->ESAUMRB01 = 0x0003F000U & _SMU_ESAUMRB01_MASK;

SMU->ESAUMRB12 = 0x00040000U & _SMU_ESAUMRB12_MASK;

// ESAU region 4/5/6 programming

// Boundary45 at 44kB and Boundary56 at 44kB (region 5 size = 0)

SMU->ESAUMRB45 = 0x0000B000U & _SMU_ESAUMRB45_MASK;

SMU->ESAUMRB56 = 0x0000B000U & _SMU_ESAUMRB56_MASK;

```

#### Note:

- The mrb12 (ESAUMRB12 in SMU\_ESAURMBR12) has to be greater than or equal to mrb01 (ESAUMRB12 in SMU\_ESAURMBR12).

- The mrb56 (ESAUMRB56 in SMU\_ESAURMBR562) has to be greater than or equal to mrb45 (ESAUMRB45 in SMU\_ESAURMBR45).

- If one of the rules above is violated, the SMU\_STATUS.SMUPRGERR is asserted.

- · When mrb01 and mrb12 are equal, region 1 (NSC) is a size of 0 and is not seen by the system.

- · When mrb45 and mrb56 are equal, region 5 (NSC) is a size of 0 and is not seen by the system.

## 4.3 BLS SAU Programming

#### 4.3.1 All Secure Configuration

All secure configuration is the default state after reset. It clears the SAU\_CTRL.ENABLE and the SAU\_CTRL.ALLNS bits in SAU, and the entire memory is in a Secure attribute.

## 4.3.2 All Non-secure Configuration

All Non-secure Configuration occurs when the SAU\_CTRL.ENABLE bit is cleared, and the SAU\_CTRL.ALLNS bit is set. The ESAU controls the security attribute of a Cortex-M33 transaction.

```

// Disable SAU (ALLNS = 1) and clear data and instruction pipe

SAU->CTRL = SAU_CTRL_ALLNS_Msk;

__DSB();

__ISB();

```

## 4.3.3 Configurable Configuration

Configurable configuration occurs when the SAU\_CTRL.ENABLE bit is set (SAU\_CTRL.ALLNS is irrelevant). Both SAU and ESAU determine the security attribute of a Cortex-M33 transaction. The code and figure below highlight how to program the SAU regions.

```

// Define all Non-secure (NS) and Non-secure Callable (NSC) Regions

#define REGIONO_BASE 0x0001E000UL

#define REGION1_BASE 0x00020000UL

#define REGION2_BASE 0x20004000UL

#define REGIONO_LIMIT 0x0001FFFFUL

#define REGION1_LIMIT 0x000FFFFFUL

#define REGION2_LIMIT 0x20017FFFUL

// CMSIS calls to enable SAU Regions

// SAU region 0 - Flash NSC at 120 kB to 128 kB (0x0001E000 - 0x0001FFFF)

SAU->RNR = (OUL & SAU_RNR_REGION_Msk);

SAU->RBAR = (REGIONO_BASE & SAU_RBAR_BADDR_Msk);

SAU->RLAR = (REGIONO_LIMIT & SAU_RLAR_LADDR_Msk) | SAU_RLAR_NSC_Msk | SAU_RLAR_ENABLE_Msk;

// SAU region 1 - Flash NS at 128 KB to 1024 kB (0x00020000 - 0x000FFFFF)

SAU->RNR = (1UL & SAU_RNR_REGION_Msk);

SAU->RBAR = (REGION1_BASE & SAU_RBAR_BADDR_Msk);

SAU->RLAR = (REGION1_LIMIT & SAU_RLAR_LADDR_Msk) | SAU_RLAR_ENABLE_Msk;

// SAU region 2 - RAM NS at 16 kB to 96 kB (0x20004000 - 0x20017FFF)

SAU->RNR = (2UL & SAU_RNR_REGION_Msk);

SAU->RBAR = (REGION2_BASE & SAU_RBAR_BADDR_Msk);

SAU->RLAR = (REGION2_LIMIT & SAU_RLAR_LADDR_Msk) | SAU_RLAR_ENABLE_Msk;

\ensuremath{//} CMSIS functions to enable SAU and clear data and instruction pipe

TZ_SAU_Enable();

_DSB();

_ISB();

```

#### 4.4 BLS BMPU Programming

#### 4.4.1 Bus Master Privileged Attribute

A Bus Master can be configured as either privileged (default) or unprivileged by programming the corresponding index in the SMU\_BMPUPATDn register.

```

// Configure all odd Bus Masters unprivileged

for (i = 0; i < SMU_NUM_BMPUS; i++) {

if (i & 0x01) {

SMU->BMPUPATD0 &= ~(1 << i);

}

}</pre>

```

#### 4.4.2 Bus Master Security Attribute

A Bus Master can be configured as either Secure (default) or Non-secure by programming the corresponding index in the SMU\_BMPUPATDn register. Configure a Bus Master as Non-secure results in the Bus Master only being able to access Non-secure addresses.

```

// Configure all odd Bus Masters Non-secure

for (i = 0; i < SMU_NUM_BMPUS; i++) {

if (i & 0x01) {

SMU->BMPUSATD0 &= ~(1 << i);

}

}</pre>

```

#### 4.4.3 Bus Master Fault Status

The Bus Master ID and the address that triggered the fault can be read from the SMU\_BMPUFS and SMU\_BMPUFSADDR registers.

```

uint32_t fs_bmpu_id;

uint32_t fs_bmpu_addr;

uint32_t fs_bmpu_secfault;

// Read Bus Master fault status

fs_bmpu_id = SMU->BMPUFS;

fs_bmpu_addr = SMU->BMPUFSADDR;

fs_bmpu_addr = SMU->IF & _SMU_IF_BMPUSEC_MASK) >> _SMU_IF_BMPUSEC_SHIFT;

// Clear the IF to capture a new fault

SMU->IF_CLR = SMU_IF_BMPUSEC;

```

# 4.5 BLS PPU Programming

# 4.5.1 Peripheral Privileged Attributes

A peripheral can be configured as either privileged (default) or unprivileged by programming the corresponding index in the SMU\_PPUPATDn register.

```

// Configure all odd peripherals unprivileged

for (i = 0; i < SMU_NUM_PPU_PERIPHS; i++) {

if (i & 0x01) {

if (i >= 32) {

SMU->PPUPATD1 &= ~(1 << (i-32));

} else {

SMU->PPUPATD0 &= ~(1 << i);

}

}

}</pre>

```

## Note:

- The peripherals in SMU\_PPUPATD0 and SMU\_PPUPATD0 are device-dependent.

- The privileged attribute of the radio subsystem (AHBRADIO index) is configured as a unit.

#### 4.5.2 Peripheral Security Attributes

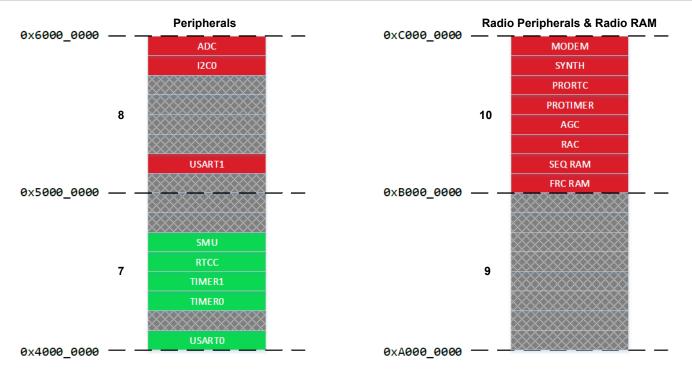

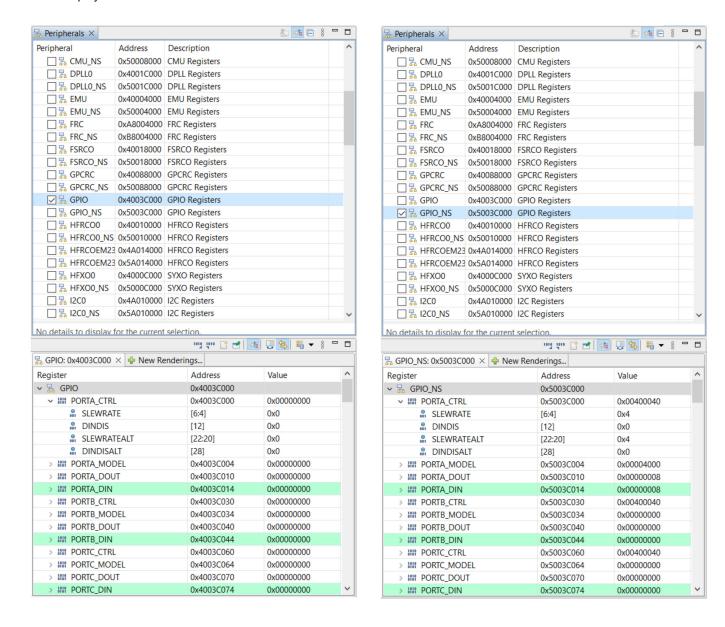

A peripheral can be configured as either Secure (default) or Non-secure by programming the corresponding index in the SMU\_PPUSATDN register. The figure below shows the memory map when the ADC, I2C0, USART1, and RADIO are configured as Non-secure and other peripherals (e.g., SMU, RTCC, TIMER1, TIMER0, USART0...) as Secure.

```

// Configure all the Non-secure peripherals

SMU->PPUSATDO &= ~SMU_PPUSATDO_USART1;

SMU->PPUSATD1 &= ~(SMU_PPUSATD1_I2CO | SMU_PPUSATD1_IADCO | SMU_PPUSATD1_AHBRADIO);

```

#### Note:

- The peripherals in SMU\_PPUSATD0 and SMU->PPUSATD1 are device-dependent.

- The security attribute of the radio subsystem (AHBRADIO index) is configured as a unit.

# 4.5.3 Peripheral Fault Status

The peripheral ID that triggered the fault can be read from the  $\mathtt{SMU\_PPUFS}$  register.

```

uint32_t fs_ppu_periph_id;

uint32_t fs_sec_fault;

uint32_t fs_priv_fault;

uint32_t fs_inst_fault;

// Read peripheral fault status

fs_ppu_periph_id = SMU->PPUFS;

fs_sec_fault = (SMU->IF & _SMU_IF_PPUSEC_MASK) >> _SMU_IF_PPUSEC_SHIFT;

fs_priv_fault = (SMU->IF & _SMU_IF_PPUPRIV_MASK) >> _SMU_IF_PPUPRIV_SHIFT;

fs_inst_fault = (SMU->IF & _SMU_IF_PPUINST_MASK) >> _SMU_IF_PPUINST_SHIFT;

// Clear the IF to capture a new fault

SMU->IF_CLR = SMU_IF_PPUSEC | SMU_IF_PPUPRIV | SMU_IF_PPUINST;

```

# 4.6 Floating Point Unit (FPU) Programming

If the Non-secure application enables the FPU at initialization, the Secure software needs to set up the NSACR register in SCB to grant the FPU access for Non-secure software.

```

// Enable Non-secure access to the FPU

SCB->NSACR |= SCB_NSACR_CP10_Msk + SCB_NSACR_CP11_Msk;

```

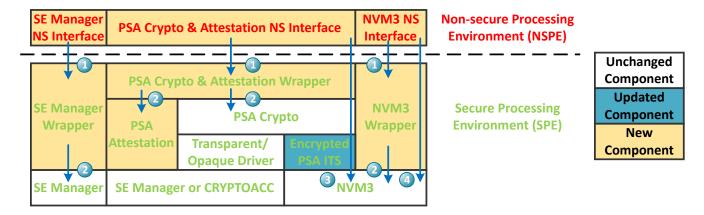

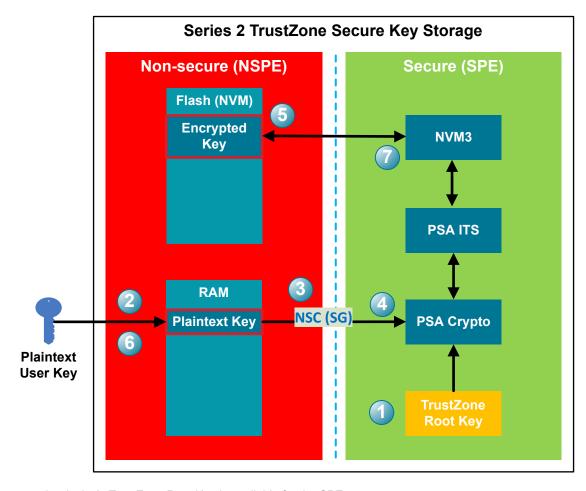

# 5. TrustZone Implementation

The goal of TrustZone implementation is to provide Secure Key Storage that can keep access to keys limited to Secure applications while at the same time allowing Non-secure applications to exercise the keys. It is an added feature for the SVM devices that do not have dedicated hardware for Secure Key Storage as in SVH devices.

The PSA Crypto is placed in a Secure region to keep key material hidden from the Non-secure application. The exposed PSA Crypto APIs stay the same while the backend provides persistent key encryption and decryption similar to the key wrapping and unwrapping functionality of the SVH device.

The following items need to be considered when upgrading the existing system for Secure Key Storage with TrustZone.

- System Configuration

- · Gecko Bootloader

- Secure Library

- TrustZone Secure Key Storage

- PSA Attestation

- SE Manager

- Common Vulnerabilities and Exposures (CVE)

#### 5.1 System Configuration

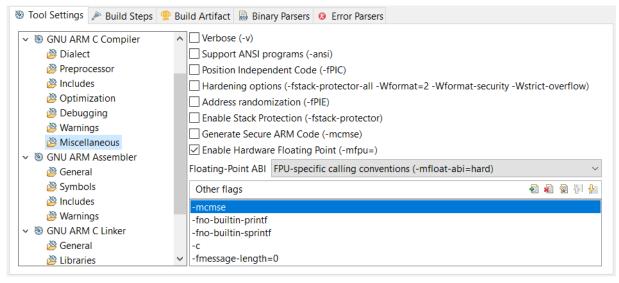

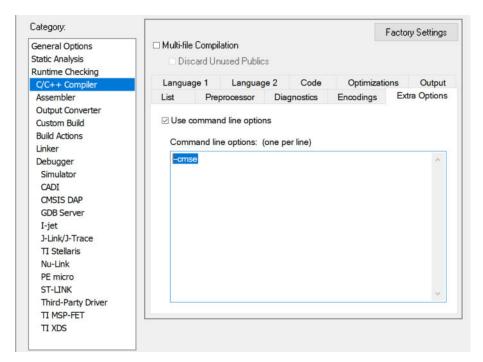

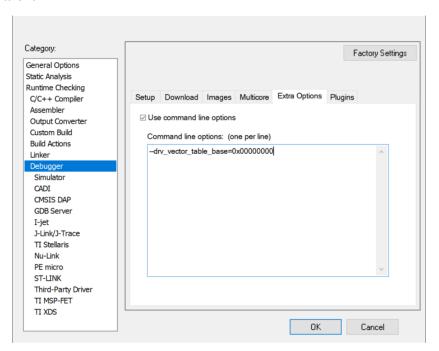

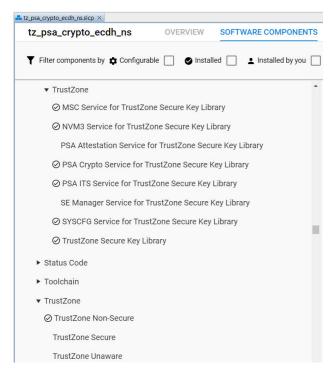

The system configuration includes the following items: