# EFP01 高エネルギー効率 PMIC ファミリ・データ・シート

EFP01 高エネルギー効率電源管理 IC (PMIC) は、EFM32 および EFR32 デバイス用の包括的なシステム電力および一次電池のクーロン・カウンタ機能を提供する、複数の出力を備えた非常に柔軟な高効率電源管理 IC です。EFP01 は、広い入力電圧範囲(0.8~5.5 V)、低静止電流 300 nA (EM2 モード、1 つの出力がイネーブルの場合)で動作します。

EFP01 は、以下のバッテリ・タイプをサポートするように構成できます。

- ・ シングル・アルカリ( $Zn/MNo_2$ )、マンガンまたはリチウム二硫化鉄( $Li/FeS_2$ )一次電池、または NimH/Nicd 充電式電池( $0.8\sim 1.8~V$ )

- ・デュアル・アルカリ、マンガンまたはリチウム二硫化鉄(Li/FeS<sub>2</sub>)一次電池、または NimH/Nicd 充電式電池( $1.6\sim3.6~\rm V$ )

- · シングル・リチウム(Li/MnO<sub>2</sub>)一次電池(1.8 ~ 3.2 V)

- ・ シングル塩化チオニル・リチウム (Li/SOCI<sub>2</sub>) 一次電池 (3.0 ~ 3.65 V)

- ・ シングル・リチウム・イオン/リチウム・ポリマー(一般に LiCoO<sub>2</sub>)充電式電池(2.7 ~ 4.35 V)

- ・ シングル・リン酸鉄リチウム・イオン (LiFePO<sub>4</sub>)充電式電池 (2.5 ~ 3.65 V)

- · USB (≤ 5.5 V)

EFP01 アプリケーションには以下が含まれます。

- · loT センサーおよびエンド・デバイス

- ・メータリング

- · ホーム・オートメーション、ビル・オートメーション、およびセキュリティ

- ・ 健康およびウェルネス

- ・ウェアラブル

- ・スマート・アクセサリ

- ・ヒューマン・インターフェイス・デバイス

# 省エネ機能

- ・4 つの電源出力を提供:

- ・1 x バック/ブースト DC-DC コンバータ

- ・1 x バック専用 DC-DC コンバータ + LDO

- · 1 x LDO

- ・1 x スイッチ出力

- · 最大効率 94%

# 第1章 機能リスト

EFP01の主な特徴は以下のとおりです。

#### · VOA

- · 出力電圧: 1.7 V ~ 5.2 V

- · DCDC A は、バック/ブースト、バック専用、またはブースト専用で構成可能

- ・ DCDC A 出力を VOC リニア・レギュレータと組み合わせる ことで、入力電圧が出力電圧に近くなるため、より効率的な 制御が可能

- ・ファームウェアでプログラム可能なスイッチ出力 (VOA\_SW)により、低電カモードで漏電の大きい外部回路 の完全なパワーダウンが可能

#### · VOB

- · 出力電圧:

- · 0.8 V ~ 3.3 V (EFP0101/03/06/09/11)

- · 0.8 V ~ 1.26 V (EFP0102/04/07/08/10)

- · DCDC B はバック構成でのみ使用可能

- · 入力電圧が出力電圧に近くなるため、並列の専用内部リニア・レギュレータによって、より効率的な制御が可能

#### · VOC

- · 出力電圧: 1.7 V ~ 3.3 V

- ・リニア・レギュレータのみ

- ・独立した第三の出力電源を作成するか、または DCDC A と 組み合わせて使用可能

# ・クーロン・カウンタ

・負荷に対する充電の無損失(センス抵抗なし)測定

#### · 通信 & 制御

- · 完全に構成可能な I<sub>2</sub>C

- ・ダイレクト・モードでエネルギー・モード間の高速遷移をサポート

- ・ホスト・プロセッサに通知するための IRQ ピン

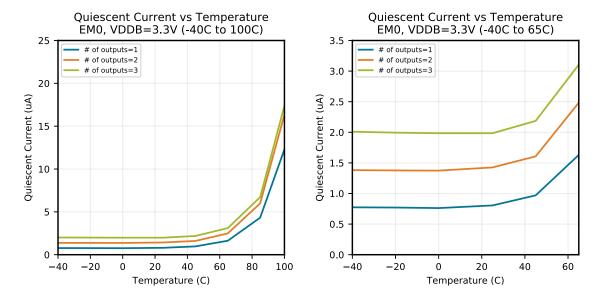

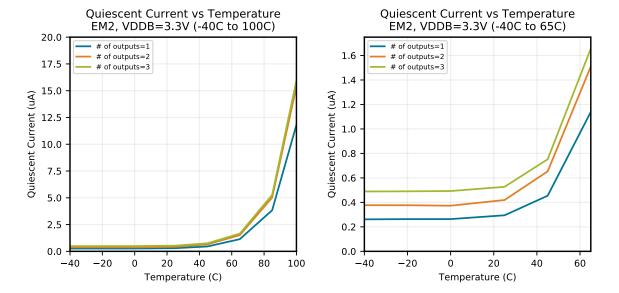

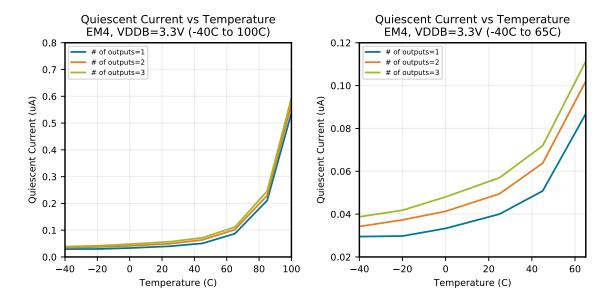

#### · EM2 超低静止電流

- ・ 150 nA: 出力がイネーブルになっていない場合

- · 300 nA: 1 つの出力がイネーブルの場合

- · 追加の出力がイネーブルになるごとに +125 nA

# ·安全性

- ・ プログラム可能な突入電流

- 耐短絡出力

- ・VDDB が 1.2 V 未満になると、低電圧誤動作防止(UVLO) 回路によってデバイスを最低電カリセット状態に維持

- ・ 過熱モニタリングおよび IRQ アサーション

# ・広範な動作範囲

- · 入力電源: 0.8 V ~ 5.5 V · 接合部温度: -40 ~ 100 °C

- ・ QFN20 3x3 mm パッケージ

# 2. Ordering Information

Additional OPN-specific features & limitations can be found in • OPN-Specific Features.

Table 2.1. Ordering Information

| Orderable Part Number (OPN) | Supported In-<br>put Voltage<br>Range               | Device Configuration  | VOB Configuration at Startup | Temp<br>Code | Package | Top Mark<br>Line 1 |

|-----------------------------|-----------------------------------------------------|-----------------------|------------------------------|--------------|---------|--------------------|

| EFP0101GM20-E               | 1.8 V–5.5 V                                         | Wired Buck            | 1.858 V                      | G            | QFN20   | P01G               |

| EFP0102GM20-E               | 1.8 V–5.5 V                                         | Wired Buck            | OFF                          | G            | QFN20   | P02G               |

| EFP0103GM20-E               | 1.8 V–5.5 V                                         | Wired Buck with LDO C | 1.858 V                      | G            | QFN20   | P03G               |

| EFP0104GM20-E               | 1.8 V–5.5 V                                         | Wired Buck with LDO C | OFF                          | G            | QFN20   | P04G               |

| EFP0106GM20-E               | 1.8 V–5.5 V                                         | Buck/Boost            | 1.858 V                      | G            | QFN20   | P06G               |

| EFP0107GM20-E               | 1.8 V–5.5 V                                         | Buck/Boost            | OFF                          | G            | QFN20   | P07G               |

| EFP0108GM20-E               | 0.8 V-1.8 V                                         | Single-Cell Boost     | OFF                          | G            | QFN20   | P08G               |

| EFP0109GM20-E               | 1.8 V - 3.6 V                                       | Wired Boost           | 1.858 V                      | G            | QFN20   | P09G               |

| EFP0110GM20-E               | 1.8 V - 3.6 V                                       | Wired Boost           | OFF                          | G            | QFN20   | P10G               |

| EFP0111GM20-E               | 1.5 V–5.5 V (after startup), 2.5–5.5 V (at startup) | Boost Bootstrap       | 1.858 V                      | G            | QFN20   | P11G               |

# **Table of Contents**

| 1. | Feature List                                                  | . 2 |

|----|---------------------------------------------------------------|-----|

| 2. | Ordering Information                                          | . 3 |

| 3. | System Overview                                               | . 7 |

|    | 3.1 Introduction                                              | . 7 |

|    | 3.2 Power                                                     | . 9 |

|    | 3.2.1 DCDC A Overview                                         |     |

|    | 3.2.2 DCDC B Overview                                         |     |

|    | 3.2.3 LDO B and LDO C Overview                                |     |

|    | 3.2.4 Coarse Regulators                                       |     |

|    | 3.3 Energy Modes                                              |     |

|    | 3.3.2 EM0                                                     |     |

|    | 3.3.3 EM2                                                     |     |

|    | 3.3.4 EM4                                                     |     |

|    | 3.4 Measurement                                               | .24 |

|    | 3.4.1 Coulomb Counter                                         |     |

|    | 3.4.2 Analog to Digital Converter (ADC)                       | .26 |

|    | 3.5 Memory                                                    | .27 |

|    | 3.5.1 OTP                                                     |     |

|    | 3.5.2 Registers                                               | .27 |

|    | 3.6 Communications and Other Digital Peripherals              |     |

|    | 3.6.1 Inter-Integrated Circuit Interface (I <sup>2</sup> C)   |     |

|    | 3.6.2 Interrupt Output (IRQ)                                  |     |

|    | 3.7 System Protection                                         |     |

|    | 3.7.1 Under-voltage Lockout (UVLO)                            |     |

|    | 3.7.2 Power-on Reset (POR)                                    |     |

|    | 3.7.4 Short Circuit Tolerance.                                |     |

|    | 3.8 Startup & Shutdown Behavior                               |     |

|    | 3.8.1 Startup Behavior                                        |     |

|    | 3.8.2 Shutdown Behavior                                       |     |

| 4. | Typical Connection Diagrams                                   | 30  |

|    | 4.1 Device Configurations                                     |     |

|    | 4.1.1 Wired Buck Configuration (EFP0101 & EFP0102).           |     |

|    | 4.1.2 Wired Buck with LDO C Configuration (EFP0103 & EFP0104) |     |

|    | 4.1.3 Buck/Boost Configuration (EFP0106 & EFP0107)            | .32 |

|    | 4.1.4 Single-Cell Boost Configuration (EFP0108)               |     |

|    | 4.1.5 Wired Boost Configuration (EFP0109 & EFP0110)           |     |

|    | 4.1.6 Boost Bootstrap Configuration (EFP0111)                 | .35 |

| 5. | Electrical Specifications                                     | 36  |

|    | 5.1 Electrical Characteristics                                | .36 |

|    | 5.1.1 Absolute Maximum Ratings     | 3    | 37 |

|----|------------------------------------|------|----|

|    | 5.1.2 Thermal Characteristics      | 3    | 38 |

|    | 5.1.3 General Operating Conditions | 3    | 39 |

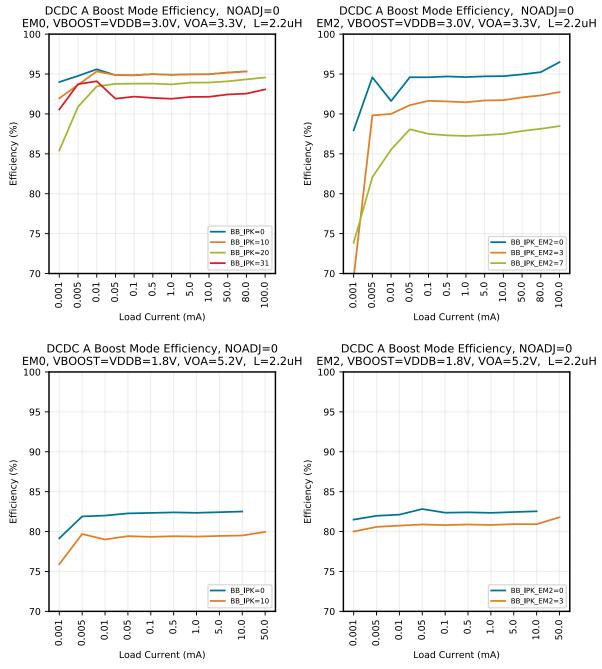

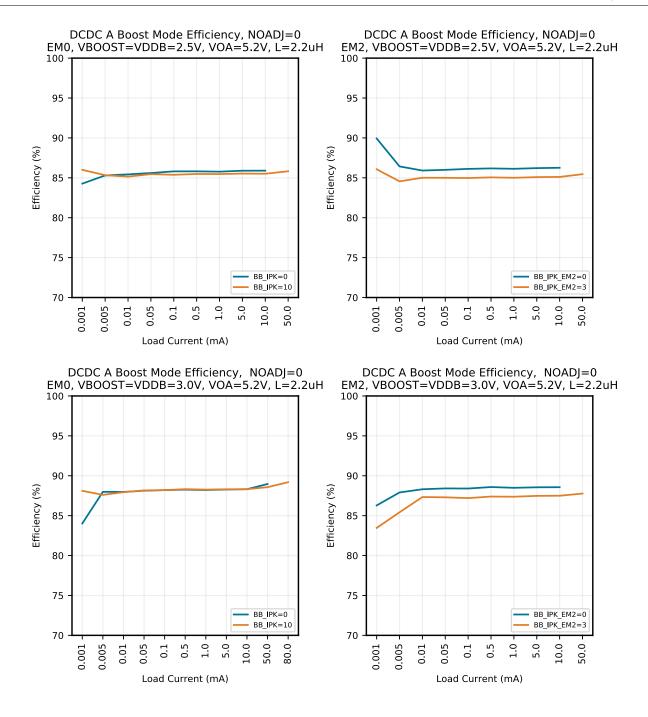

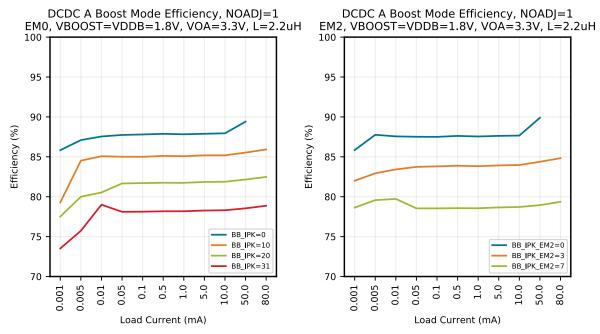

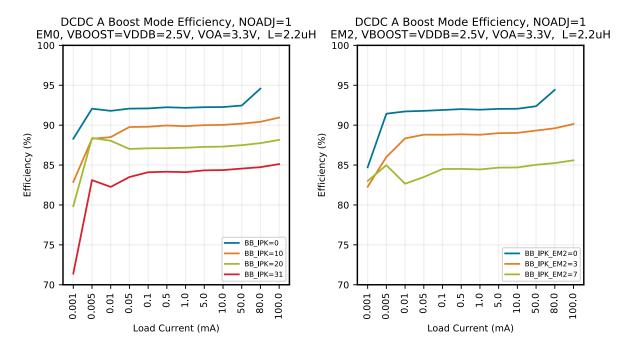

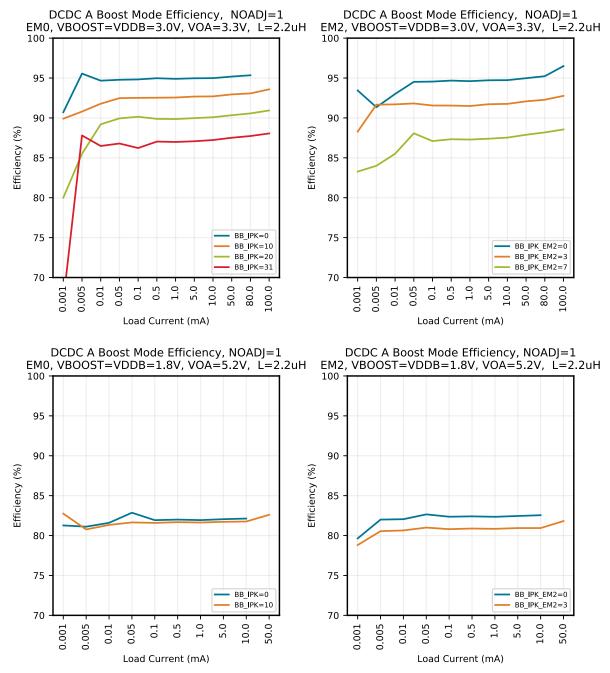

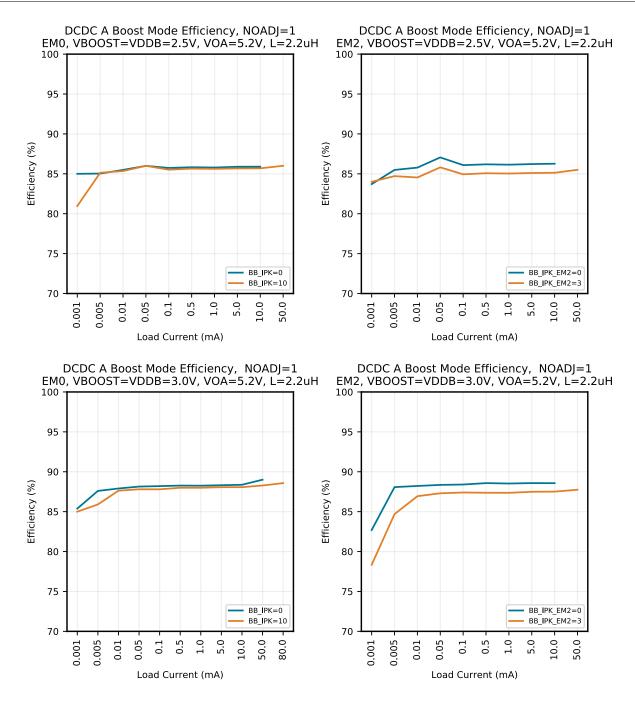

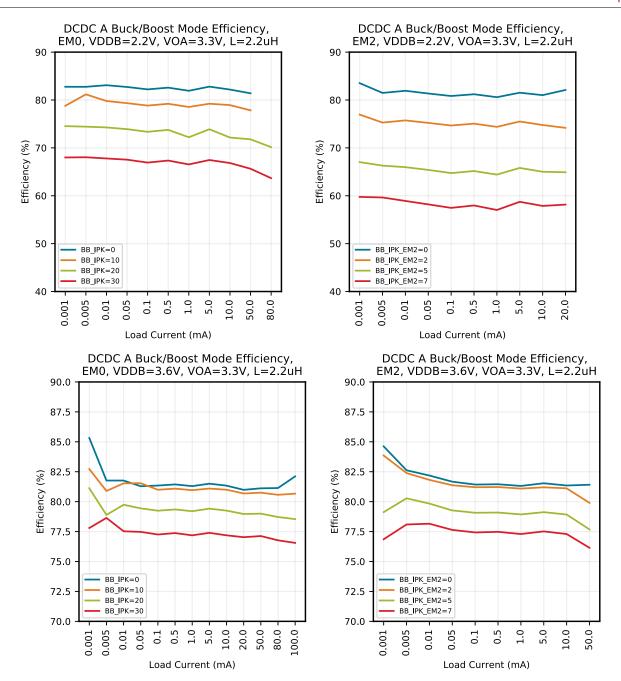

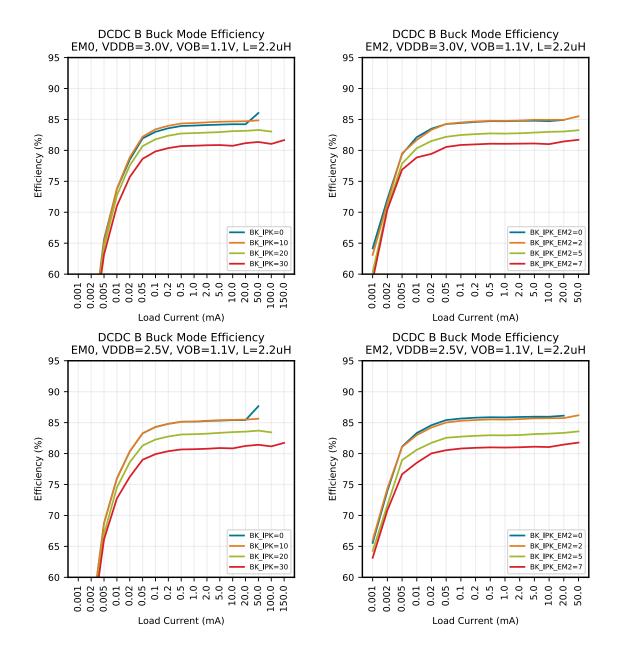

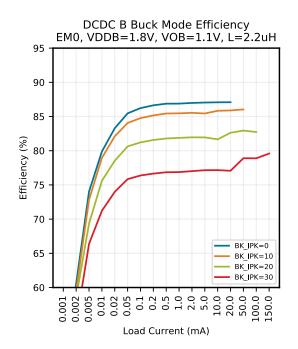

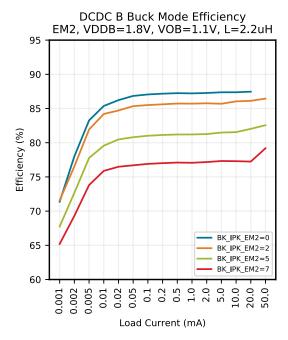

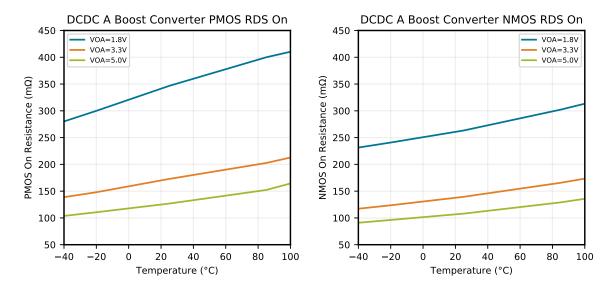

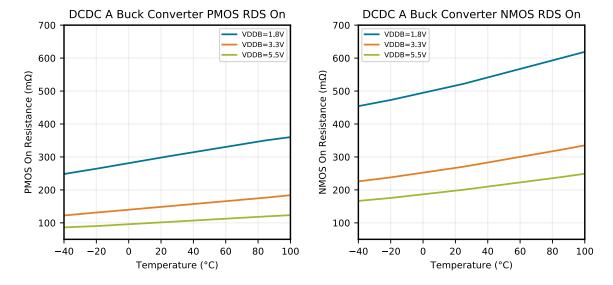

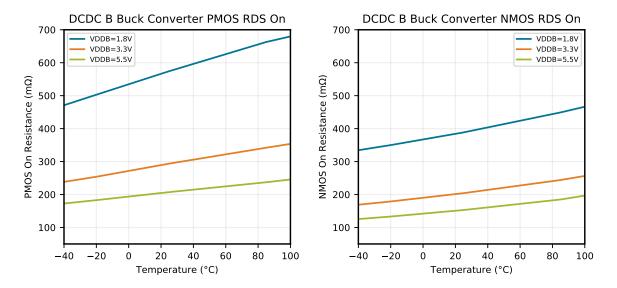

|    | 5.2 Typical Performance Curves     | -    | 74 |

|    | 5.2.1 DCDC A Efficiency            |      |    |

|    | 5.2.2 DCDC B Efficiency            |      |    |

|    | 5.2.3 Quiescent Current            |      |    |

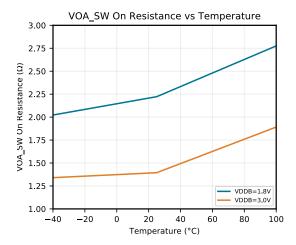

|    | 5.2.4 RDS ON                       |      |    |

|    |                                    |      |    |

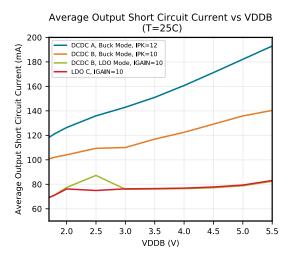

|    | 5.2.5 Short Circuit Current        |      |    |

|    | 5.2.6 ADC                          | 8    | 39 |

| 6. | Register Definitions               | . 9  | €0 |

|    | 6.1 Register Map                   | 9    | 90 |

|    | 6.2 Register Description           | 9    | 92 |

|    | 6.2.1 STATUS G                     |      |    |

|    | 6.2.2 STATUS V                     |      |    |

|    | 6.2.3 STATUS_GM                    |      |    |

|    | 6.2.4 STATUS VM                    |      |    |

|    | 6.2.5 STATUS_LIVE                  |      |    |

|    | 6.2.6 DEVREV ID                    |      |    |

|    | 6.2.7 CC_CAL                       |      |    |

|    | 6.2.8 OTP_ADDR                     |      |    |

|    | 6.2.9 OTP_ADDK                     |      |    |

|    | 6.2.10 OTP_RDATA                   |      |    |

|    | 6.2.11 CMD                         |      |    |

|    | 6.2.12 CC MODE                     |      |    |

|    | <del>-</del>                       |      |    |

|    | 6.2.13 CCA_MSBY                    |      |    |

|    | 6.2.14 CCA_LSBY                    |      |    |

|    | 6.2.15 CCB0_MSBY                   |      |    |

|    | 6.2.16 CCB0_LSBY                   |      |    |

|    | 6.2.17 CCB2_MSBY                   |      |    |

|    | 6.2.18 CCB2_LSBY                   |      |    |

|    | 6.2.19 CCC_MSBY                    |      |    |

|    | 6.2.20 CCC_LSBY                    |      |    |

|    | 6.2.21 VDD_AVG_MSN                 |      |    |

|    | 6.2.22 VDD_AVG_LSBY                |      |    |

|    | 6.2.23 VDD_MIN_MSN                 |      |    |

|    | 6.2.24 VDD_MIN_LSBY                |      |    |

|    | 6.2.25 VDD_MAX_MSN                 | 11   | 18 |

|    | 6.2.26 VDD_MAX_LSBY                | 11   | 19 |

|    | 6.2.27 TEMP_MSN                    | 12   | 20 |

|    | 6.2.28 TEMP_LSBY                   | . 12 | 21 |

|    | 6.2.29 VOA_SW_STAT                 | . 12 | 22 |

|    | 6.2.30 I2C_CTRL                    | . 12 | 22 |

|    | 6.2.31 CC_CTRL                     |      |    |

|    | 6.2.32 EM CRSREG CTRL              |      |    |

|    | 6.2.33 VOA V                       |      |    |

|    | 6.2.34 VOC V                       |      |    |

| 6.2.35 VOB_EM0_V                | 126 |

|---------------------------------|-----|

| 6.2.36 VOB_EM2_V                | 127 |

| 6.2.37 BIAS_SW                  | 128 |

| 6.2.38 BB_IPK                   | 130 |

| 6.2.39 BB_CTRL3                 | 132 |

| 6.2.40 BB_CTRL5                 |     |

| 6.2.41 BB_CTRL6                 |     |

| 6.2.42 LDOB_CTRL                |     |

| 6.2.43 LDOC_CTRL                |     |

| 6.2.44 LDOC_BB_CTRL             |     |

| 6.2.45 BK_CTRL0                 |     |

| 6.2.46 BK_CTRL1                 |     |

| 6.2.47 BK_IPK                   |     |

| 6.2.48 BK_CTRL2                 |     |

| 6.2.49 ADC_CC_CTRL              |     |

| 6.2.50 ADC_LIMITS               | 145 |

| 7. OTP Definitions              | 146 |

| 7.1 OTP Definition              | 146 |

| 7.2 OTP Defaults                | 147 |

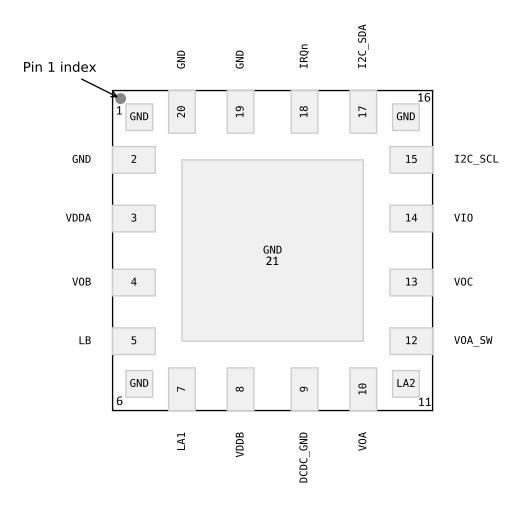

| 8. Pin Definitions              | 148 |

| 8.1 EFP01 Device Pinout         | 148 |

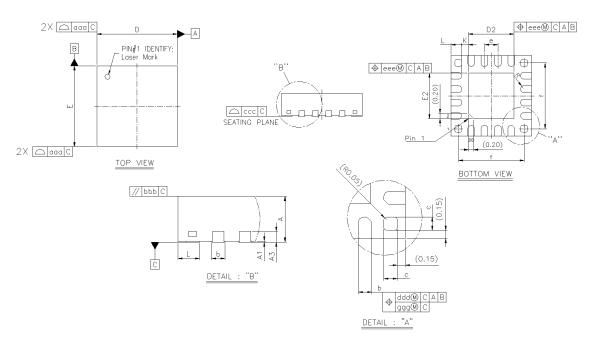

| 9. QFN20 Package Specifications | 150 |

| 9.1 QFN20 Package Dimensions    |     |

| ·                               |     |

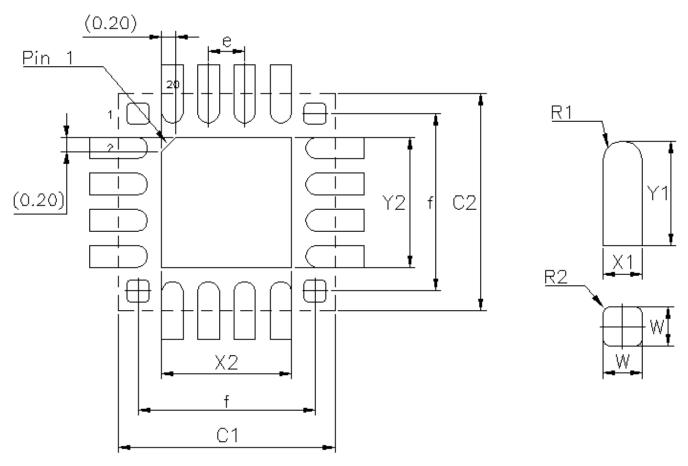

| 9.2 QFN20 PCB Land Pattern      | 152 |

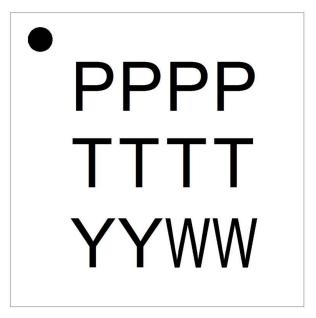

| 9.3 QFN20 Package Marking       | 154 |

| 10. Revision History            | 155 |

# 3. System Overview

#### 3.1 Introduction

The EFP01 Energy Friendly PMIC product family is designed to support a range of battery-powered applications, as well as other systems requiring high performance and low energy consumption.

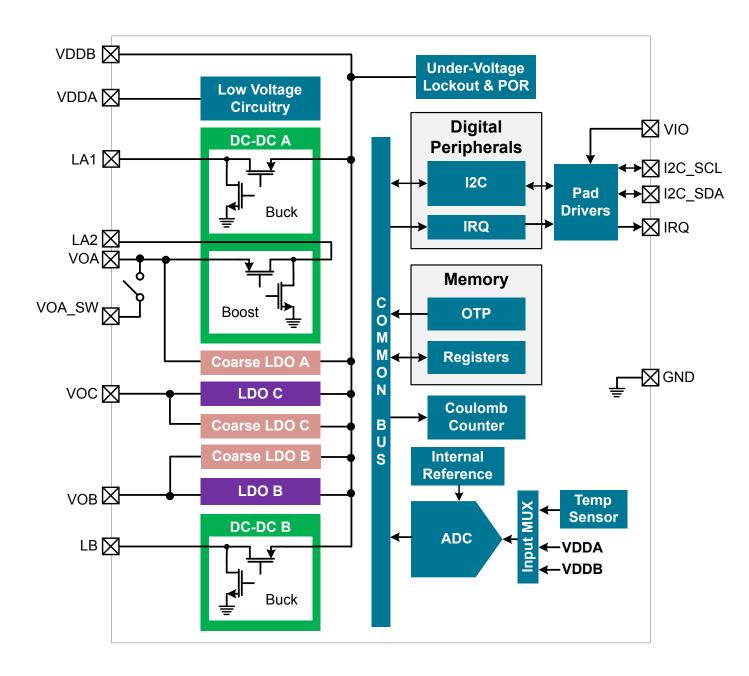

A block diagram of the EFP01 family is shown in Figure 3.1 EFP01 Block Diagram on page 7. The diagram shows a superset of features available on the family, which vary by part number. For more information about specific device features, consult Ordering Information.

Figure 3.1. EFP01 Block Diagram

Table 3.1. OPN-Specific Features

| OPN                           | Supported<br>Input Volt-<br>age Range                             | VOA Out-<br>put at<br>Startup | VOA<br>DCDC<br>Mode at<br>Startup                      | VOB Out-<br>put at<br>Startup | VOB Pro-<br>gramma-<br>ble Range | VOC Out-<br>put at<br>Startup           | EM4 Sup-<br>port                                     | Battery<br>Voltage<br>Monitor-<br>ing |

|-------------------------------|-------------------------------------------------------------------|-------------------------------|--------------------------------------------------------|-------------------------------|----------------------------------|-----------------------------------------|------------------------------------------------------|---------------------------------------|

| EFP0101                       | 1.8 V-5.5 V                                                       | 1.860 V                       | Wired Buck                                             | 1.858 V                       | 0.8 V -3.3<br>V                  | 1.870 V                                 | Supported                                            | Yes, on<br>VDDB                       |

| Wired Buck                    |                                                                   |                               |                                                        |                               | V                                |                                         |                                                      | VDDB                                  |

| EFP0102<br>Wired Buck         | 1.8 V-5.5 V                                                       | 1.860 V                       | Wired Buck                                             | OFF                           | 0.8 V -1.26<br>V                 | 1.870 V                                 | Supported,<br>VOB<br>Coarse<br>Regulator<br>disabled | Yes, on<br>VDDB                       |

| EFP0103 Wired Buck with LDO C | 1.8 V-5.5 V                                                       | 1.860 V                       | Wired Buck<br>with LDO                                 | 1.858 V                       | 0.8 V -3.3<br>V                  | Not availa-<br>ble (Paired<br>with VOA) | Supported                                            | Yes, on<br>VDDB                       |

| EFP0104 Wired Buck with LDO C | 1.8 V-5.5 V                                                       | 1.860 V                       | Wired Buck<br>with LDO                                 | OFF                           | 0.8 V -1.26<br>V                 | Not availa-<br>ble (Paired<br>with VOA) | Supported,<br>VOB<br>Coarse<br>Regulator<br>disabled | Yes, on<br>VDDB                       |

| EFP0106<br>Buck/Boost         | 1.8 V-5.5 V                                                       | 1.860 V                       | Buck/Boost                                             | 1.858 V                       | 0.8 V -3.3<br>V                  | 1.870 V                                 | Supported                                            | Yes, on<br>VDDB                       |

| EFP0107<br>Buck/Boost         | 1.8 V-5.5 V                                                       | 1.860 V                       | Buck/Boost                                             | OFF                           | 0.8 V -1.26<br>V                 | 1.870 V                                 | Supported,<br>VOB<br>Coarse<br>Regulator<br>disabled | Yes, on<br>VDDB                       |

| EFP0108<br>Single-Cell Boost  | 0.8 V-1.8 V                                                       | 1.860 V                       | Wired<br>Boost                                         | OFF                           | 0.8 V -1.26<br>V                 | OFF                                     | Not sup-<br>ported                                   | Yes, on<br>VDDA                       |

| EFP0109<br>Wired Boost        | 1.8 V-3.6 V                                                       | 3.327 V                       | Wired<br>Boost                                         | 1.858 V                       | 0.8 V -3.3<br>V                  | 1.870 V                                 | Supported                                            | Yes, on<br>VDDB                       |

| EFP0110<br>Wired Boost        | 1.8 V-3.6 V                                                       | 3.327 V                       | Wired<br>Boost                                         | OFF                           | 0.8 V -1.26<br>V                 | 1.870 V                                 | Supported,<br>VOB<br>Coarse<br>Regulator<br>disabled | Yes, on<br>VDDB                       |

| EFP0111<br>Boost Bootstrap    | 1.5 V-5.5 V<br>(after start-<br>up),<br>2.5V-5.5V<br>(at startup) | 5.222 V                       | Wired<br>Boost, Cur-<br>rent Limi-<br>ted Ena-<br>bled | 1.858 V                       | 0.8 V -3.3<br>V                  | 1.870 V                                 | Supported<br>when sup-<br>ply voltage<br>>= 2.5V.    | Not sup-<br>ported                    |

#### 3.2 Power

The EFP01 can provide up to three voltage rails for EFR32 and EFM32 devices from a single input supply voltage.

The EFP01 has two independent DCDC converters: DCDC A and DCDC B, each requiring an external inductor. DCDC A can use buck/boost, wired buck, or wired boost configurations, while DCDC B only supports buck configuration.

In addition, the EFP01 has two integrated LDOs supplied from the VDDB pin: LDO B and LDO C. LDO B is internally wired in parallel with DCDC B. LDO C can be used independently or externally wired in parallel with DCDC A.

Finally, each EFP01 output (VOA, VOB, VOC) has its own coarse regulator in parallel for use in EM4. The coarse regulators have very low quiescent current draw, but have poor output regulation (e.g., the output may range from  $\sim$ 1.7 to 3.4 V) and can only support very light loads ( $\sim$ 100  $\mu$ A).

The EFP01 Configuration Tool in Simplicity Studio can generate recommended settings and a configuration header file to simplify development.

#### 3.2.1 DCDC A Overview

The EFP01's DCDC A can be configured for buck/boost, wired buck, or wired boost modes.

Table 3.2. DCDC A Configuration and Modes Summary

| Hardware Configuration | DCDC A Operating Mode      | Required Register Setting        | Compatible OPNs   |

|------------------------|----------------------------|----------------------------------|-------------------|

| Buck                   | Wired Buck                 | BB_CTRL3.BB_MODE = 6             | EFP0101 / EFP0102 |

| Buck with LDO          | Wired Buck with LDO        | BB_CTRL3.BB_MODE = 5             | EFP0103 / EFP0104 |

| Buck/Boost             | Autonomous<br>(Buck/Boost) | BB_CTRL3.BB_MODE = 1 (typically) | EFP0106 / EFP0107 |

| Single-Cell Boost      | Wired Boost                | BB_CTRL3.BB_MODE = 7             | EFP0108           |

| Wired Boost            | Wired Boost                | BB_CTRL3.BB_MODE = 7             | EFP0109 / EFP0110 |

| Boost Bootstrap        | Wired Boost                | BB_CTRL3.BB_MODE = 7             | EFP0111           |

# 3.2.1.1 Output Voltage Configuration

The DCDC A output target voltage is set by the VOA\_V register according to the below equation:

$VOA (V) = 1.7374V + (VOA_V \times 0.0306V)$

Unlike DCDC B, there is only a single VOA output voltage register that is used in both EM0 and EM2 modes.

Note that in Boost modes it is possible to program the VOA output voltage to a voltage higher than the Maximum Output Voltage in the Electrical Characteristics table. Firmware should ensure that the Maximum Output Voltage isn't exceeded.

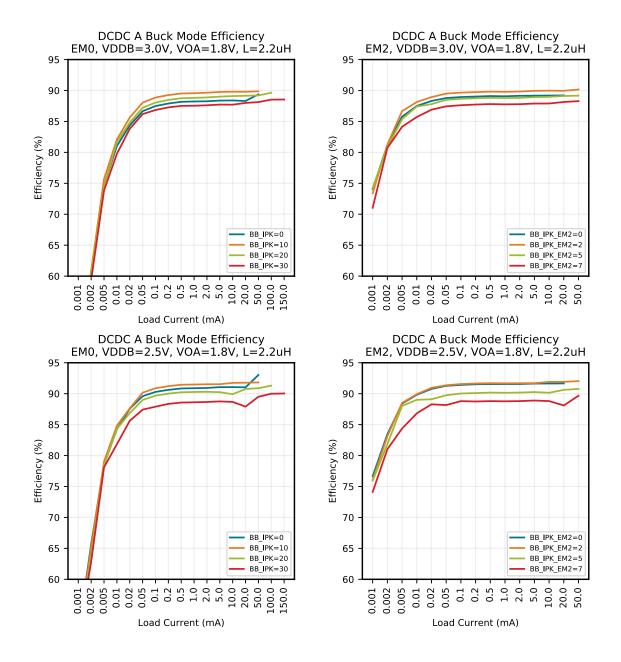

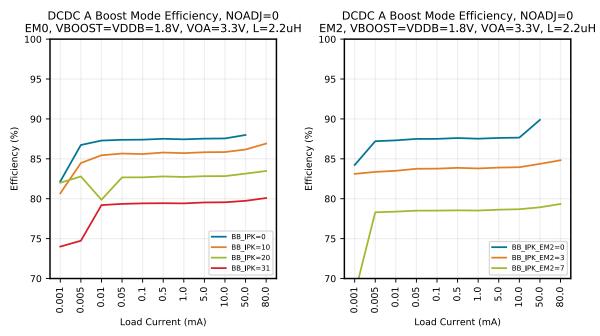

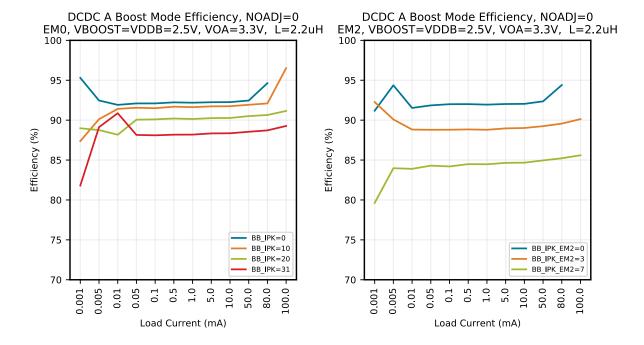

#### 3.2.1.2 Peak Current Configuration

DCDC A has a configurable peak current adjustment set by the BB\_IPK and BB\_IPK\_EM2 fields of the BB\_IPK register. The BB\_IPK and BB\_IPK\_EM2 settings are used differently depending on the operating mode of the DCDC A converter (as shown below), but the resulting peak currents for all modes are derived from the following base peak current (IPK\_BASE) equations.

In EM0, IPK\_BASE is determined by:  $IPK_BASE = 0.090A + (0.009A \times BB_IPK)$

In EM2, IPK\_BASE is determined by:  $IPK_BASE = 0.090A + 0.009A \times (4 \times BB_IPK_EM2 + 2)$

Typically, the peak current can be lowered in EM2 for greater efficiency. However, unlike DCDC B there is only a single Coulomb counter for DCDC A that is used in both EM0 and EM2 modes. Therefore, if Coulomb counting is used with DCDC A, BB\_IPK\_EM2 must be set such that the peak current in EM2 is the same as the peak current in EM0 to ensure the charge per pulse is the same in both energy modes. Roughly equivalent peak currents in EM2 and EM0 can be achieved by setting BB\_IPK\_EM2 = (BB\_IPK - 2) / 4.

**Note:** The Maximum Output Current formulas below provide useful guidance but are not a guarantee of performance. The final authority for the Maximum Output Current will be the Output Load Current specifications in the Electrical Characteristics tables.

#### **Buck Mode**

- Register Programming: BB\_CTRL3.BB\_MODE = WiredBuck or Autonomous

- Peak Current  $A = IPK_BASE + \frac{25ns \times (VDDB VOA)}{L_A}$

- Maximum Output Current (A) = 0.5 × IPK\_BASE

Buck/Boost Mode (NTM Operation)

- Register Programming: BB\_CTRL3.BB\_MODE = Autonomous

- Peak Current  $A = 1.15 \times IPK\_BASE + \frac{25ns \times VDDB}{L_A}$

- Maximum Output Current (A) = 0.5 × 1.15 × IPK\_BASE

Boost Mode (with no peak current adjustment)

- Register Programming: BB\_CTRL3.BB\_MODE = WiredBoost or Autonomous, BB\_CTRL6.BB\_IPK\_NOADJ = 1

- Peak Current  $A = 2.35 \times IPK\_BASE + \frac{25ns \times VBOOST}{L_A}$

- Maximum Output Current  $A = efficiency \times 0.5 \times 2.35 \times IPK\_BASE \times \frac{VBOOST}{VOA}$

Boost Mode (with peak current adjustment)

- Register Programming: BB\_CTRL3.BB\_MODE = WiredBoost or Autonomous,BB\_CTRL6.BB\_IPK\_NOADJ = 0,

BB\_CTRL5.BB\_IPK\_BOOST\_ADJ is programmed as recommended in its register description, ADC\_CC\_CTRL.ADC\_INTERVAL >

0 to enable ADC operations.

- When operating in Boost Mode with peak current adjustment, the peak current will be adjusted to maintain a near constant output load current over the battery voltage range. Note that peak current adjustment only affects EM0 operation. In EM2, the Boost Mode (with no peak current adjustment) equations apply.

- Peak Current  $A = 2.35 \times MIN \left( \frac{IPK\_BASE \times VOA}{2 \times VBOOST}, 385mA \right) + \frac{25ns \times VBOOST}{L_A}$

- Maximum Output Current  $(A) = efficiency \times 0.5 \times 2.35 \times MIN \left( \frac{IPK\_BASE \times VOA}{2 \times VBOOST}, 385mA \right) \times \frac{VBOOST}{VOA}$

#### 3.2.1.3 Peak Current Adjustment

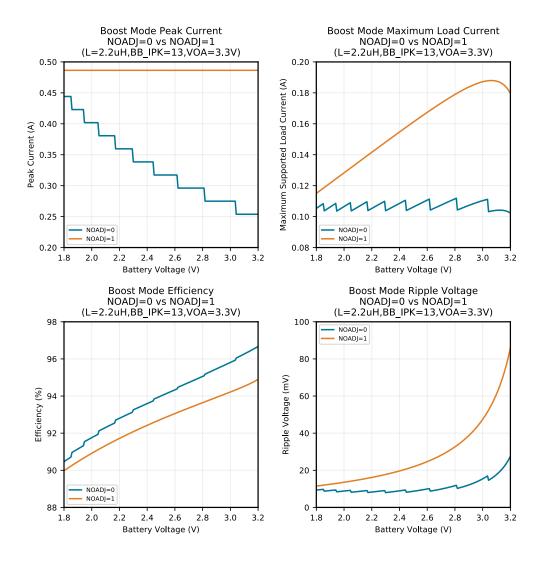

In boost mode, the EFP01 can be configured to automatically adjust the DCDC A peak current based on the battery voltage to support a near-constant maximum output load current (where the maximum output load current is ~ IPK\_BASE / 2). This feature allows the boost converter to lower the peak current at higher battery voltages, resulting in more efficient operation and lower output ripple voltage, as shown in Figure 3.2 Peak Current Adjustment Comparison on page 11.

Because the peak current adjustment feature requires battery voltage monitoring, the ADC must be enabled (i.e., the ADC\_INTERVAL field of the ADC\_CC\_CTRL register is set to a non-zero value). This also means that peak current adjustment is not available in the Boost Bootstrap configuration, because battery monitoring is not support in that configuration.

If peak current adjustment is enabled, it will only affect peak current in EM0, and not EM2.

To use peak current adjustment:

- 1. Set BB\_IPK\_NOADJ = 0 in the BB\_CTRL6 register

- 2. Program BB\_IPK\_BOOST\_ADJ in the BB\_CTRL5 register as recommended in its register description. Note that because the BB\_IPK\_BOOST\_ADJ value is dependent on both the VOA target voltage and the BB\_IPK setting, the BB\_IPK\_BOOST\_ADJ value should be updated whenever the VOA target or the peak current settings are changed.

- Set ADC\_INTERVAL in the ADC\_CC\_CTRL register to a non-zero value to enable ADC operations

To disable peak current adjustment, set BB\_IPK\_NOADJ = 1 in the BB\_CTRL6 register.

Figure 3.2. Peak Current Adjustment Comparison

#### 3.2.1.4 Current Limiting

When powering EFP01 from weak power sources or sources with a high internal impedance, peak load currents at the converter output can cause a large supply voltage droop at the input, increasing the risk of an unintended power-on reset. To alleviate these issues, it may be necessary to limit the input current.

Note: EFP0111 is the only OPN that has its current limit enabled by default (on DCDC A).

**Note:** Because enabling the current limit will essentially current-starve the output, the system designer should validate the application under the worst-case output load current.

On EFP01, the current limit is controlled by forcing a minimum time between the start of pulse events ( $T_{SW\_MIN}$ ) and is configured by BB\_IRI\_CON in the BB\_CTRL6 register. BB\_IRI\_CON can be calculated based on the mode, the input voltage (VDDB), output voltage (VOA), DCDC A inductor value ( $L_A$ ), peak current ( $I_{PK}$ , set by BB\_IPK), and the desired limited battery current ( $I_{BATT\_LIMIT}$ ) as follows:

In buck mode:

$$I_{BATT\_LIMIT} = \frac{L \times I_{PK}^2}{2 \times T_{SW\ MIN}} \times \frac{1}{(VDDB - VOA)}$$

In boost mode:

$$I_{BATT\_LIMIT} = \frac{L \times I_{PK}^2}{2 \times T_{SW\_MIN}} \times \left(\frac{1}{VOA - VBOOST} + \frac{1}{VBOOST}\right)$$

where  $T_{SW\_MIN}$  is programmed by BB\_IRI\_CON as follows:

$$T_{SW\_MIN} = 300ns \times (2 \times BB\_IRI\_CON + 1)$$

Note that the required BB\_IRI\_CON setting for a given current limit varies with the VDDB or VBOOST voltages and the peak current, both variables that can change over battery voltage. An application requiring a fixed current limit over the entire range of the battery may need to occasionally measure the VDDB voltage and recalculate / reprogram the BB\_IRI\_CON setting.

Note also that in configurations where the VOC LDO is used in parallel with the VOA output (e.g., Buck with LDO configuration), the BB\_IRI\_CON bitfield in the BB\_CTRL6 register will control the current limit when the converter is in DCDC mode and the VOC IRI CON bitfield in the LDOC BB CTRL register will control the current limit when the converter is in LDO mode.

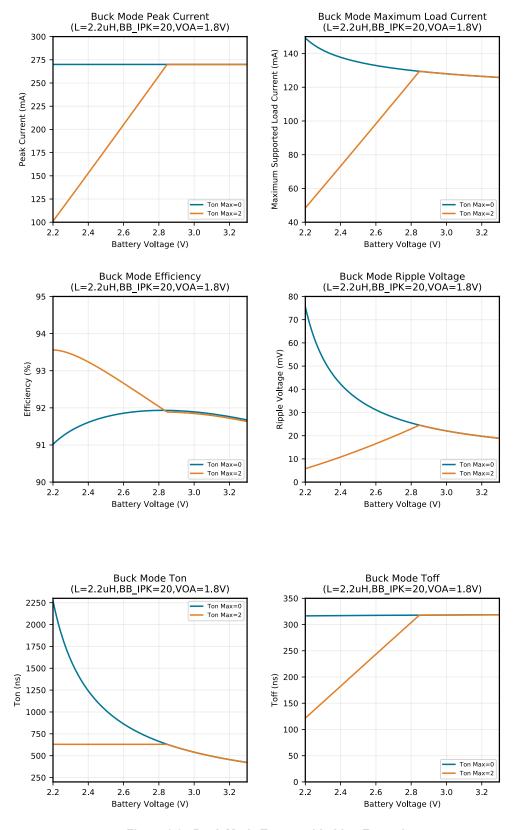

#### 3.2.1.5 T<sub>ON</sub> Maximum Limiting

# **Buck Mode Ton\_MAX**

In Buck mode, the pulse frequency modulation (PFM) pulse on time ( $T_{ON}$ ) required to charge the inductor is given by:  $T_{ON} = \frac{L \times I_{PK}}{VDDB - VOA}$  As VDDB approaches VOA, the resulting  $T_{ON}$  can become quite large, resulting in sizable output ripple voltage or, in the worst case, the DCDC stalling altogether.

When the BB\_TON\_MAX field in the LDOC\_BB\_CTRL register is set to a non-zero value, the PFM pulse  $T_{ON}$  will be limited as shown:  $T_{ON\_MAX} = 70 \quad ns + (1 + (4 \times BB\_TON\_MAX))$  A limited  $T_{ON}$  will terminate the inductor charging before the programmed peak current value is reached, and limit the maximum available load current and the actual peak current values.

Because the time-measuring circuitry required to limit T<sub>ON</sub> costs some small amount of power, BB\_TON\_MAX should be set to set a nonzero value only under specific conditions:

- If the subsequent reduction in max available load current can be tolerated and the reduction in ripple voltage is desired.

- When operating with low input voltage headroom (i.e., VDDB VOA is very small) and there is no LDO enabled in parallel with the DCDC output.

Figure 3.3. Buck Mode  $T_{\mbox{ON\_MAX}}$  Limiting Example

# **Boost Mode Ton\_MAX**

In Boost mode, the BB\_TON\_MAX field in the LDOC\_BB\_CTRL register should be set to a non-zero value to ensure a finite on-time under all conditions. Without this protection, in certain scenarios (e.g., where the inductor peak current may be limited by battery impedances and inductor and power train resistances), the inductor current may not reach the threshold of the peak current detector and the Boost converter power train NMOS will not turn off.

#### 3.2.1.6 Boost Mode Toff Maximum Limiting

In certain scenarios, the battery voltage at the input to the EFP01 in boost mode can be as high as, or higher than, the desired output. For example:

- A Li/FeS<sub>2</sub> battery can have an output voltage as high as 1.8 V at the very start of its life, which would be problematic in an application where the regulated output needs to be 1.8 V.

- Two alkaline or Li/FeS<sub>2</sub> batteries in series can provide a voltage as high as 3.6 V. If a 3.3 V regulated output is desired, the buck/boost configuration can be used, but the buck/boost configuration efficiency is ~5-8% less than the wired boost configuration.

A PFM converter, such as the EFP01, cannot typically operate in a boost mode with an input voltage even slightly higher than the output. In this scenario, the inductor current during the T<sub>OFF</sub> interval may never reach zero (a requirement for the converter to signal the end of the discharge phase), resulting in an inaccurate and poorly regulated output voltage.

To address this issue, the EFP01 has a T<sub>OFF</sub> maximum limiting feature to enforce a maximum discharge interval time. When the BB\_TOFF\_MAX field in the BB\_CTRL6 register is set to a nonzero value, the T<sub>OFF</sub> discharge interval is ended after a set period of time, even if the inductor current has not reached zero, with any residual inductor current is discharged into the VOA pin.

To avoid extremely large ripple voltage, T<sub>OFF</sub> maximum limiting should only be enabled when the maximum battery voltage is no higher than 0.3V above the programmed VOA voltage.

#### 3.2.1.7 NTM Buck/Boost Transitional Mode

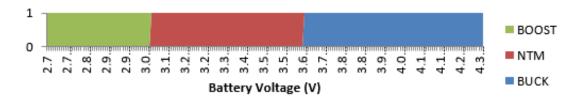

When DCDC A is in the Buck/Boost configuration and programmed to Autonomous (or Buck/Boost) mode, (i.e, BB\_CTRL3.BB\_MODE = 1), the DCDC converter will automatically switch between one of three operating modes:

- · Buck: Traditional Buck operation used when VDDB is much greater than VOA

- Boost: Traditional Boost operation used when VDDB is much lower than VOA

- NTM: Transitional mode between Buck and Boost modes, used when VDDB is close to VOA

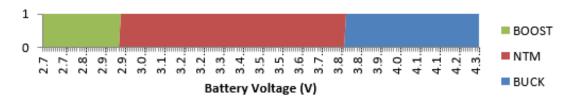

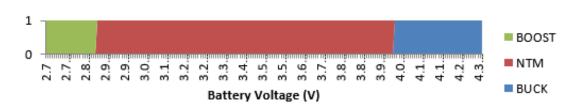

The Boost-to-NTM and NTM-to-Buck mode transition voltage thresholds are controlled by the NTM\_LDO\_THRSH bit field in the BB\_CTRL3 register. For example, the figures below show the DCDC A operating mode versus the battery voltage for various NTM\_LDO\_THRSH settings for a Buck/Boost application with a 3.3V output.

Figure 3.4. Operating Mode vs Battery Voltage, NTM\_LDO\_THRSH=3

Figure 3.5. Operating Mode vs Battery Voltage, NTM\_LDO\_THRSH=5

Figure 3.6. Operating Mode vs Battery Voltage, NTM\_LDO\_THRSH=7

# 3.2.1.8 VOA Switch (VOA\_SW)

The VOA output has an internal switch connecting it to the VOA\_SW pin. This optional VOA\_SW output can be used to completely power down high-leakage external circuitry when entering the 3.3.3 EM2 and/or 3.3.4 EM4 modes. The VOA\_SW state is controlled by the VOA\_SW\_CON bitfield in the BIAS\_SW register.

Note that if a large capacitive load is attached to the VOA\_SW output, the VOA output may see momentary voltage droops when VOA SW is enabled.

#### 3.2.1.9 DCDC A with LDO C in Parallel

In certain configurations, DCDC A is connected in parallel with LDO C on the printed circuit board, such as 4.1.2 Wired Buck with LDO C Configuration (EFP0103 & EFP0104) . This configuration is advantageous when the minimum input supply voltage approaches the VOA output voltage (e.g., VDDB<sub>MIN</sub> - VOA  $\leq$  300mV) as it allows EFP01 to continue to regulate the output voltage over a wider input voltage range than is possible with DCDC A alone.

When LDO C is used in parallel with DCDC A:

- The DCDC mode must be set to WIREDBUCKLDO (i.e., BB MODE = 3 in the BB CTRL3 register)

- The input voltage threshold for transition from Buck-to-LDO mode can be adjusted by the NTM\_LDO\_THRSH bitfield in the BB\_CTRL3 register.

- If inrush current limiting is desired, the BB\_IRI\_CON bitfield in the BB\_CTRL6 register controls the current limit when the converter is

in DCDC mode and the VOC\_IRI\_CON bitfield in the LDOC\_BB\_CTRL register controls the current limit when the converter is in

LDO mode.

- When Coulomb counting is enabled, the resulting pulse counts will be split between the CCA\_MSBY/LSBY result registers (when the converter is in DCDC mode) and the CCC\_MSBY/LSBY result registers (when the converter is in LDO mode).

Note that when using LDO C in parallel with DCDC A, LDO C is not available as an independent LDO.

#### 3.2.1.10 Low Voltage Charge Pump

The EFP0108 Single-Cell Boost mode enables the use of battery voltages between 0.8V and 1.8V. Because this is below the 1.8V minimum VDDB operating voltage, the EFP0108 must temporarily generate an internal voltage sufficient to supply VDDB. To do this, the EFP0108 enables a charge pump supplied from its VDDA pin at startup. Once the internal charge pump output reaches a level sufficient to supply VDDB, the regular DCDC A Boost powertrain circuitry is enabled and the VOA output is boosted to its target voltage. At that point, VDDB will be powered from the DCDC A output (VOA is externally connected to VDDB as shown in Figure 4.4 Single-Cell Boost Configuration on page 33). At this point, the low voltage charge pump is no longer needed and is automatically disabled.

For all other OPNs, the low voltage charge pump is not used, and the VDDA input can safely be grounded.

#### 3.2.2 DCDC B Overview

The EFP01's DCDC B can only be configured for buck mode.

Table 3.3. DCDC B Configuration and Modes Summary

| Mode                        | Required Register Configurations |

|-----------------------------|----------------------------------|

| Buck with LDO B in parallel | BK_CTRL1.BK_MODE = 3             |

| Buck                        | BK_CTRL1.BK_MODE = 1             |

#### 3.2.2.1 Output Voltage Configuration

The DCDC B output target voltage in EM0 is set by VOB EM0 V in the VOB EM0 V register according to the below equation:

VOB in EM0 (V) =  $0.8095V + (VOB EM0 V \times 0.0223V)$

In EM2, the DCDC B output target voltage will be automatically set to value specified in the VOB\_EM2\_V register according to the below equation:

VOB in EM2  $(V) = 0.8095V + (VOB EM2 V \times 0.0223V)$

#### 3.2.2.2 Peak Current Configuration

DCDC B has configurable peak current adjustment, set by the BK IPK and BK IPK EM2 fields in the BK IPK register.

In EM0, IPK\_BASE is determined by:  $IPK_BASE = 0.090A + (0.009A \times BK_IPK)$

In EM2, IPK BASE is determined by: IPK BASE = 0.090A + 0.009A × (4 × BK IPK EM2 + 2)

The DCDC B buck converter peak current is determined by:  $Peak \ Current \ A = IPK\_BASE + \frac{25ns \times (VDDB - VOB)}{L_B}$

Typically, the peak current can be lowered in EM2 for improved efficiency.

**Note:** The Maximum Output Current formula below provides useful guidance but is not a guarantee of performance. The final authority for the Maximum Output Current will be the Output Load Current specifications in the Electrical Characteristics tables.

The DCDC B buck converter maximum output current is determined by: Maximum Output Current (A) = 0.5 × IPK\_BASE

#### 3.2.2.3 Current Limiting

When powering EFP01 from weak power sources or sources with a high internal impedance, peak load currents at the converter output can cause a large supply voltage droop at the input, increasing the risk of an unintended power-on reset. To alleviate these issues, it may be necessary to limit the input current.

**Note:** Because enabling the current limit will essentially current-starve the output, the system designer should validate the application under the worst-case output load current.

On EFP01, the current limit is controlled by forcing a minimum time between the start of pulse events and is configured by the BK\_IRI\_CON field in BK\_CTRL2. BK\_IRI\_CON can be calculated based on the mode, the input voltage (VDDB), output voltage (VOB), DCDC B inductor value (L<sub>B</sub>), peak current (I<sub>PK</sub>, set by BK\_IPK), and the desired limited battery current (I<sub>BATT\_LIMIT</sub>) as follows:

$$I_{BATT\_LIMIT} = \frac{L \times I_{PK}^2}{2 \times T_{SW} \times (VDDB - VOB)}$$

where T<sub>SW</sub> is programmed by BK IRI CON as follows:

$$T_{SW} = 300$$

ns × (2 × BK\_IRI\_CON + 1)

The maximum output load current is going to be limited accordingly, and can be determined by:  $I_{LOAD\_MAX} = \frac{VDDB}{VOB} \times efficiency \times I_{BATT\_LIMIT}$

Note that the required BK\_IRI\_CON setting for a given current limit varies with the VDDB voltage and the peak current, both variables that can change over battery voltage. An application requiring a fixed current limit over the entire range of the battery may need to occassionally measure the VDDB voltage and recalculate / reprogram the BK\_IRI\_CON setting.

# 3.2.2.4 Ton Maximum Limiting

In Buck mode, the pulse frequency modulation (PFM) pulse on time ( $T_{ON}$ ) required to charge the inductor is roughly (L × IPK)/(VDDB-VOB). As VDDB approaches VOB, the resulting  $T_{ON}$  can become quite large, resulting in large output ripple voltage or, in the worst case, the DCDC stalling altogether.

When the BK\_TON\_MAX field in the BK\_CTRL1 register is set to a non-zero value, the PFM pulse  $T_{ON}$  is limited to no more than 70 ns  $\times$  (1 + 4  $\times$  BK\_TON\_MAX), which terminates the inductor charging before the programmed peak current value is reached. When operating in this  $T_{ON}$  limiting mode, the maximum available load current and the actual peak current values are reduced from the otherwise expected value.

Because the time measuring mechanism costs some power, BK\_TON\_MAX should be set to set a nonzero value only under specific conditions:

- · If the subsequent reduction in max available load current can be tolerated and the reduction in ripple voltage is desired.

- When operating with low input voltage headroom (i.e., VDDB VOB is very small) and there is no LDO enabled in parallel with the DCDC output.

Comparison plots of T<sub>ON</sub> limiting can be found in Figure 3.3 DCDC A TON Max Limiting Example on page 14.

#### 3.2.2.5 DCDC B with LDO B in Parallel

DCDC B is internally connected in parallel with LDO B, and the two can optionally be used in parallel. This configuration is advantageous when the minimum input supply voltage (VDDB) approaches the VOB output voltage (e.g., VDDB<sub>MIN</sub> - VOB  $\leq$  300mV) as it allows EFP01 to continue to regulate the output voltage over a wider input voltage range than is possible with DCDC B alone.

When LDO B is used in parallel with DCDC B:

- The DCDC mode must be set to BUCKLDO (i.e., BK\_MODE = 3 in the BK\_CTRL1 register).

- The input voltage threshold for transition from Buck-to-LDO mode can be adjusted by the BK\_LDO\_THRESH bit field in the BB\_CTRL2 register. It is recommended that this setting be left at power-on default value.

#### 3.2.3 LDO B and LDO C Overview

The EFP01 has two integrated LDOs supplied from the VDDB pin. Instead of being continously on, each LDO operates in a pulsed-current mode that minimizes quiescent current and is compatible with the internal Coulomb counter.

#### 3.2.3.1 LDO B

LDO B is hard-wired in parallel with DCDC B, with an output sharing the VOB pin. When used in parallel with DCDC B, DCDC B will automatically switch to LDO B to provide better efficiency as the input voltage approaches the output voltage. LDO B can also be used as a standalone LDO (i.e. without DCDC B).

LDO B shares the DCDC B output voltage target registers, VOB\_EM0\_V and VOB\_EM2\_V.

#### Table 3.4. LDO B Summary

| Mode                    | Required Register Configuration(s) | Output Pin | Output Target Voltage Registers |

|-------------------------|------------------------------------|------------|---------------------------------|

| In parallel with DCDC B | BK_CTRL1.BK_MODE = 3               | VOB        | VOB_EM0_V and VOB_EM2_V         |

| Standalone, no DCDC     | BK_CTRL1.BK_MODE = 2               |            |                                 |

#### 3.2.3.2 LDO C

Similar to LDO B, LDO C can be used as an independent standalone supply (with the LDO output on the VOC pin) or may be connected in parallel with DCDC A (with the LDO output sharing the VOA pin with DCDC A). When used in parallel with DCDC A, DCDC A will automatically switch to LDO C to provide better efficiency as the input voltage approaches the output voltage.

LDO C's output voltage register depends on the mode:

- In standalone mode, the output voltage target is set in the VOC\_V register.

- In parallel mode, the LDO C shares DCDC A's output voltage register, VOA V.

# Table 3.5. LDO C Summary

| Mode                    | Required Register Configuration(s)                  | Output Pin                                  | Output Target Voltage Register |

|-------------------------|-----------------------------------------------------|---------------------------------------------|--------------------------------|

| In parallel with DCDC A | BB_CTRL3.BB_MODE = 5                                | VOA = VOC (must be shorted together on PCB) | VOA_V                          |

| Standalone, no DCDC     | LDOC_CTRL.LDOC_ENA_SA = 1 and BB_CTRL3.BB_MODE != 5 | VOC                                         | VOC_V                          |

#### 3.2.3.3 Maximum Output Current

After startup, the maximum output current for LDO B and LDO C is set by the LDOB\_IGAIN and LDOC\_IGAIN fields in the LDOB\_CTRL and LDOC\_CTRL registers, respectively. The LDOx\_IGAIN fields should be set to the required output current plus margin, but no higher than necessary. LDOx IGAIN can be computed as follows:

**Note:** The Maximum Output Current formula below provides useful guidance but is not a guarantee of performance. The final authority for the Maximum Output Current will be the Output Load Current specifications in the Electrical Characteristics tables.

$$LDOx\_IGAIN = ROUND \left( 17 - \frac{V_{OUT}}{2.76 \times I_{OUT\_MAX}} \right)$$

At startup, and prior to the LDO reaching its target voltage, the available output current for LDO B and LDO C is determined by the LDOB\_VMIN and LDOC\_VMIN fields in the LDOB\_CTRL and LDOC\_CTRL registers, respectively. To ensure the LDO output current at startup is always at least the desired amount (as configured by LDOx\_IGAIN, above), the settings for the LDOx\_VMIN fields should be programmed based on the output target voltage as shown below:

Table 3.6. LDOx\_VMIN Settings

| V <sub>OUT</sub> Range         | LDOx_VMIN Setting |

|--------------------------------|-------------------|

| V <sub>OUT</sub> ≥ 2.7V        | 3                 |

| 2.4V ≤ V <sub>OUT</sub> < 2.7V | 2                 |

| 2.0V ≤ V <sub>OUT</sub> < 2.4V | 1                 |

| V <sub>OUT</sub> < 2.0V        | 0                 |

Table 3.7 Example LDOx\_IGAIN and LDOx\_VMIN settings on page 20 shows the recommended LDOx\_IGAIN and LDOx\_VMIN settings for some example applications. Note that in the calculations below, I<sub>OUT\_MAX</sub> has been increased by 20% to provide some margin.

Table 3.7. Example LDOx\_IGAIN and LDOx\_VMIN settings

| V <sub>OUT</sub> (V) | I <sub>OUT_MAX</sub> (mA) | LDOx_IGAIN | LDOx_VMIN |

|----------------------|---------------------------|------------|-----------|

| 1.8                  | 50                        | 6          | 0         |

| 1.8                  | 100                       | 12         | 0         |

| 3.0                  | 50                        | 0          | 3         |

| 3.0                  | 100                       | 8          | 3         |

| 1.2 (LDO B only)     | 50                        | 10         | 0         |

#### 3.2.3.4 LDO Current Limiting

On EFP01, the current limit is controlled by forcing a minimum time between the start of pulse events (T<sub>SW\_MIN</sub>) and is configured by the BK\_IRI\_CON bitfield in the BK\_CTRL2 register (for LDO B) or the VOC\_IRI\_CON bitfield in the LDOC\_BB\_CTRL register (for LDO C). The (I<sub>BATT\_LIMIT</sub>) can be determined from the IRI\_CON setting as follows:

$$I_{BATT\_LIMIT} = \frac{I_{OUT\_MAX}}{(2 \times IRI\_CON + 1)}$$

where I<sub>OUT MAX</sub> is determined by LDOx\_IGAIN as shown in 3.2.3.3 Maximum Output Current.

Because the current limit is essentially current-starving the output, most applications will likely want to disable the current limit after the output is stable (which can be determined by polling the STATUS LIVE.VOx INREG LIVE bits).

#### 3.2.3.5 LDO Startup

In some configurations, the LDO input supply (i.e., the VDDB pin) is powered from the VOA output. The VOA output may see momentary voltage droops when the LDO is enabled due to instantaneous current required to charge the  $10\mu$ F capacitors on the LDO outputs. To avoid this, the current limit can be enabled before the LDO is enabled and then disabled after the LDO output is stable. Consult 3.2.3.4 LDO Current Limiting for more information.

#### 3.2.3.6 DCDC to LDO Transition

When DCDC A or B is operating with a LDO in parallel, at some point the VDDB input supply voltage approaches the LDO output voltage causing the controller to switch from DCDC mode to LDO mode. The dropout voltage (VDDB-VOB for LDO B or VDDB-VOC for LDO C) at which this transition from DCDC to LDO occurs is controlled by the BK\_LDO\_THRESH bit field in the BK\_CTRL2 register for DCDC B / LDO B, and by the NTM LDO THRSH bit field in the BB CTRL3 register for DCDC A / LDO C.

# 3.2.3.7 Bypass Mode

Both LDO B and LDO C support a bypass mode, in which the VDDB pin input voltage is shorted directly to the corresponding output pin (VOB and VOC, respectively). By default, both LDOs automatically enter bypass mode when the input supply voltage at VDDB drops too low to maintain regulation accuracy. This behavior can be disabled for both LDOs by setting the LDO\_NO\_AUTO\_BYP bit in the LDOB\_CTRL register.

In addition, both LDO B and LDO C can be forced into bypass mode by setting the BYP bit in the LDOB\_CTRL and LDOC\_CTRL registers, respectively. When forcing bypass mode, care must be taken to ensure that any loads attached to the LDO output pins (VOB and VOC) are tolerant of the VDDB pin input voltage.

#### 3.2.4 Coarse Regulators

Each EFP01 output (VOA, VOB, VOC) has its own coarse regulator in parallel for use in EM4. The coarse regulators have very low quiescent current draw but poor output regulation — the outputs may range from 1.69V to 3.4V — and can only support very light loads (100μA).

The coarse regulator for each output can be enabled by setting the corresponding CRSREG\_EN\_x bit in the EM\_CRSREG\_CTRL register. If the CRSREG\_BYP bit is set, any enabled coarse regulator's output (VOA, VOB, or VOC pin) is shorted to its input (the VDDB pin).

For certain OPNs (EFP0102/04/07/08/10) the maximum VOB output is limited to 1.26V, which is incompatible with both the coarse regulator and the bypass mode. For this reason, the VOB coarse regulator and VOB coarse regulator bypass features are disabled on these OPNs.

# 3.3 Energy Modes

The EFP01 operates in 3 different energy modes to optimize efficiency based on the expected load.

Table 3.8. Energy Modes Overview

| Energy Mode | Maximum Out-<br>put Current (per<br>output)                                | BIAS_SW Register Programming | Coarse Regula-<br>tor                                               | DCDCs and<br>LDOs                                                                                                        | ADC       | Coulomb Counter |

|-------------|----------------------------------------------------------------------------|------------------------------|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-----------|-----------------|

| ЕМО         | Full Output Cur-<br>rent (value de-<br>pends on mode<br>and configuration) | BIAS0 = 7                    | Disabled                                                            | On, if enabled                                                                                                           | Available | Available       |

| EM2         | ~20 mA (value depends on mode and configuration)                           | BIAS2 = 1                    | Disabled                                                            | On, if enabled. Note that if BB_CTRL6.BB_I PK_NOADJ is set in Boost modes, no peak current adjustment will occur in EM2. | Available | Available       |

| ЕМ4         | ~100 uA                                                                    | N/A                          | Enabled according to setting of CRSREG_EN_X bits in EM_CRSREG_C TRL | All DCDCs and<br>LDOs disabled                                                                                           | Disabled  | Not supported   |

# 3.3.1 Energy Mode Control

The energy mode state of EFP01 can be changed either by I<sup>2</sup>C or via direct pin control.

# 3.3.1.1 I<sup>2</sup>C Control

Using standard  $I^2C$  control, the EFP01's energy mode can be set by writing the EM\_STSEL bitfield in the EM\_CRSREG\_CTRL register. The EFP01's internal pull up resistors on  $I^2C_SDA$  and  $I^2C_SCL$  pins will continue to be enabled in EM2 and EM4 modes when using this method.

#### 3.3.1.2 Direct Mode Control

In direct mode, the internal pull-ups on the I2C\_SDA and I2C\_SCL pins are disabled, and the pins become high-impedance inputs that the host processor can drive to quickly change energy modes.

Once enabled by setting the EM\_DIRECTEN bit in the EM\_CRSREG\_CTRI register, direct mode allows the energy mode to be selected by driving the I2C\_SDA and I2C\_SCL pins according to Table 3.9 Direct Mode Energy Mode States on page 23. When I2C\_SCL and I2C\_SDA enter the I<sup>2</sup>C Start Condition, direct mode is automatically disabled, and the EFP01 optionally enters EM0 if FORCE\_EM0 = 1 in the EM\_CRSREG\_CTRL register.

Note: Use of Direct Mode is not recommended unless the host processor has dedicated hardware support for EFP01 (e.g., EFR32xG22 and later devices). Although Direct Mode state control can be bit-banged, there can be some undesireable side effects. For example, if the host processor receives a system reset (hard or soft) while in the Direct Mode EM0 or EM2 state, the host's  $I^2C$  outputs can be disabled and can float to logic low levels (because the EFP01's internal pull-ups are disabled in Direct Mode). Because  $I^2C_SCL = I^2C_SDA = 0$  is recognized by EFP01 as the EM4 state in Direct Mode, EFP01 disables its DCDC converters and LDO outputs and enters EM4 where it can only supply ~100  $\mu$ A. This low current output is insufficient for a host processor to boot, resulting in an unusable state from which recovery is not possible without disconnecting and then reconnecting the power supply.

**Note:** Direct Mode is primarily intended for applications where the EFP01 is the only device on the  $I^2C$  bus; other  $I^2C$  devices may not tolerate the non-standard  $I^2C$  states used by Direct Mode.

| Direct Mode State                | I2C_SCL Level | I2C_SDA Level | Allowed State Transitions          |

|----------------------------------|---------------|---------------|------------------------------------|

| EM0                              | 1             | 1             | • EM2 <sup>1</sup>                 |

|                                  |               |               | • I <sup>2</sup> C Start Condition |

| EM2                              | 0             | 1             | • EM0                              |

|                                  |               |               | • EM4                              |

| EM4                              | 0             | 0             | • EM2 <sup>1</sup>                 |

| I <sup>2</sup> C Start Condition | 1             | 0             | • EM0 <sup>2</sup>                 |

Table 3.9. Direct Mode Energy Mode States

# Note:

- 1. Direct mode transitions between EM0 and EM4 are not allowed. The system must briefly go through the EM2 state on EM4 exit or entrance.

- 2. If the FORCE\_EM0 bit in the EM\_CRSREG\_CTRL register is set, the internal device state will be set to EM0 automatically whenever the I<sup>2</sup>C start condition appears.

#### 3.3.2 EM0

The EFP01 defaults to EM0 out of reset. In EM0, all features are enabled, and the maximum output current can be supported on any enabled DCDC converters.

#### 3.3.3 EM2

Functionally, EM2 is very similar to EM0, with the proviso that in EM2 bias currents are reduced for improved efficiency at the expense of maximum supported output current.

DCDC A and DCDC B have independent peak current configuration bit fields for EM2 (in BB\_IPK\_EM2 and BK\_IPK\_EM2, respectively). In addition, the VOB output target voltage has its own independent configuration in EM2 (VOB\_EM2\_V).

DCDC B has an independent result register for storing the Coulomb counter result in EM2 (CCB2\_MSBY/LSBY). However, DCDC A shares one set of registers for Coulomb counting in both EM0 and EM2. Because of this, DCDC A must should use the same peak current setting in both EM0 and EM2 in order for the Coulomb count to be accurate.

# 3.3.4 EM4

In EM4, the EFP01 disables all enabled DCDCs and LDOs, and enables any desired coarse regulators (i.e., those with their CRSREG\_EN\_x bits set in the EM\_CRSREG\_CTRL register). ADC voltage and temperature measurements are disabled in EM4. Coulomb counting is not supported in EM4.

While in EM4, the EFP01's registers can be read or written via I<sup>2</sup>C transactions, but the EFP01 will not generate any IRQs in EM4.

Several device configurations have restrictions on EM4 operation:

- In Figure 4.4 Single-Cell Boost Configuration on page 33, EM4 is not supported at all.

- In Figure 4.6 Boost Bootstrap Configuration on page 35, EM4 is supported only when the supply voltage > 2.5V

**Note:** Unless the host processor has dedicated EM4 hardware support for 3.3.1.2 Direct Mode Control, EM4 should not be used. Once the EFP01 is in EM4, it is only able to source 100 µA per output, which may not be sufficient to power the host while it exits EM4 and sends the necessary I<sup>2</sup>C command to place the EFP01 in EM2 or EM0. Dedicated EFP01 EM4 hardware support is available on EFR32xG22 and later devices.

#### 3.4 Measurement

#### 3.4.1 Coulomb Counter

#### Note:

Refer to AN1188: EFP01 Coulomb Counting for a more detailed discussion of the Coulomb counter and example code.

The EFP01 has an integrated Coulomb counter that can losslessly measure the charge drawn from the battery for each DCDC and LDO.

Before normal operation can begin, the Coulomb counter must go through a calibration phase. Periodically, recalibration may be necessary due to changes in operating conditions (e.g., battery voltage or operating temperature).

#### 3.4.1.1 Calibration

#### Overview

During calibration, a known internal current load is applied to the selected output, and the device counts the number of 10 MHz clock cycles required for a fixed number of pulse-frequency modulation (PFM) pulses to occur. The CC\_CAL register CCL\_SEL, CC\_CAL\_NREQ, and CCL\_LVL fields respectively determine the output used (VOA, VOB, or VOC), the number of PFM pulses to count, and the current load applied to the output. The CCC\_MSBY and CCC\_LSBY registers are retasked during calibration to store the resulting number of 10 MHz clock cycles counted (note that only the CCC\_MSBY and CCC\_LSBY registers are used regardless of which output is being calibrated). Based on these results, the charge-per-pulse (CPP) can be determined.

After configuration, calibration is initiated by setting the CC\_CAL\_STRT bit in the CMD register. If enabled, the Coulomb counter should be disabled prior to calibration by setting writing a 0 to the CC\_EN bit in the CC\_CTRL register.

For accurate calibration, any devices or loads powered by the EFP01's outputs are expected to be in a stable, steady-state of operation during this calibration phase. In practice, occasional recalibration of the Coulomb counter is expected, particularly when either the input voltage or the temperature has changed significantly.

#### **Factors Affecting the Charge-Per-Pulse**

The charge-per-pulse (CPP) may vary depending on the operating mode of the converter. For example, if DCDC B is configured in buck with LDO mode (i.e., the converter automatically switches between buck and LDO modes depending on input voltage), the CPP when the converter is in buck can differ from the CPP when the converter is operating in LDO mode. For this reason, it may be necessary to calibrate a given DCDC converter in each of its expected operating modes. Thus if DCDC B is in buck with LDO mode, and the battery voltage is sufficiently close to the output voltage such that the converter may switch to LDO mode, calibration should be performed on DCDC B once in buck mode and again in LDO mode.

The current DCDC operating modes of DCDC A and DCDC B are reported by the CCA\_MODE and CCB\_MODE fields of the CC\_MODE register, respectively. For calibration purposes, the operating modes can be temporarily forced using the BB\_MODE and BK\_MODE fields in the BB\_CTRL3 and BK\_CTRL1 registers for DCDC A and DCDC B, respectively. Host firmware is expected to maintain a CPP for each operating mode of the converter.

In addition, the energy mode can affect the charge-per-pulse. The VOB output has independent result registers for EM0 and EM2, and will need to be calibrated in each energy mode. The VOA and VOC outputs each have only a single result register pair used in both EM0 and EM2. If Coulomb Counting is use with VOA, the BB\_IPK and BB\_IPK\_EM2 peak current values are expected to be the same to ensure an accurate count on VOA regardless of energy mode.

#### 3.4.1.2 Recalibration

In addition, certain changes in external conditions may affect the charge-per-pulse. The below list contains conditions that may necessitate a recalibration event:

- · Significant change in input supply voltage

- · Significant change in temperature

#### 3.4.1.3 Operation

#### Note:

Refer to AN1188: EFP01 Coulomb Counting for a more detailed discussion of the Coulomb counter and example code.

PFM pulse counts for the VOA, VOB (separately for EM0 and EM2), and VOC outputs are stored in the CCA\_MSBY/CCA\_LSBY (VOA), CCB0\_MSBY/CCB\_LSBY (VOB in EM0), CCB2\_MSBY/CCB2\_LSBY (VOB in EM2), and CCC\_MSBY/CCC\_LSBY (VOC) most significant/least significant byte register pairs, respectively, during normal operation. Note that when DCDC A is operating with LDO C in parallel, the resulting counts will be split between the CCA result registers (when the DCDC A is powering the load) and the CCC result registers (when LDO C is powering the load).

# **Prescaler**

The actual value stored in a given Coulomb counter result register pair is scaled according to the CC\_PRESCL field in the CC\_CTRL register. This setting applies globally such that the count in a given result register pair represents 2<sup>(16-2×CC\_PRESCL)</sup> PFM pulses. Note that the prescaler setting does not affect the CCC\_MSBY/LSBY registers during calibration.

#### **Enabling / Disabling**

Start Coulomb counting by writing a 1 to the CC\_EN bit in the CC\_CTRL register; stop counting by writing a 0 to CC\_EN.

#### Servicing

Once enabled, the Coulomb counter result registers will eventually overflow, so some amount of firmware maintenance is required. The CC\_THRSH field in the CC\_CTRL register sets the desired threshold (50%, 62.5%, 75%, or 87%) for setting the STATUS\_G register CC\_FULL flag. Note that the CC\_FULL\_UNMASK bit in the STATUS\_GM register must be written to 1 so that an interrupt can be requested when the CC\_FULL flag is set. When firmware receives an interrupt, and discovers that CC\_FULL is set, all relevant Coulomb counter result registers should be read and added to local variable counts. Additionally, each converter's operating mode should be determined (by reading the CCA\_MODE or CCB\_MODE field in the CC\_MODE register for DCDC A or DCDC B, respectively) in order to perform battery life calculations using the relevant CPP value. Clear the Coulomb counter result registers after reading them by writing a 1 to the CC\_CLR bit in the CMD register.

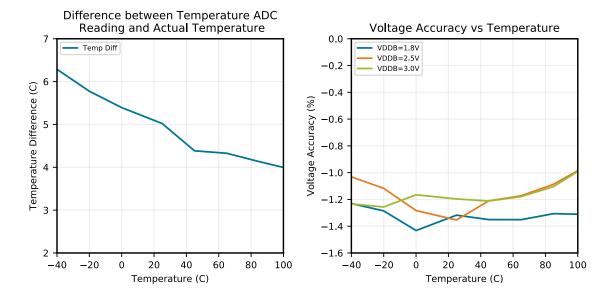

#### 3.4.2 Analog to Digital Converter (ADC)

An internal ADC can monitor the internal die temperature and the battery voltage. The battery voltage is determined by reading the voltage at the either the VDDA or VDDB pins of the device. The determination of which pin to read is made automatically by hardware - if a valid voltage is present on VDDA (e.g., CC MODE.SC MODE==1), VDDA will be measured; otherwise, VDDB will be measured.

#### **ADC Result Registers**

The measured 12-bit ADC readings are automatically loaded into 8-bit register pairs, divided into the most significant nibble and the least significant byte. Because these ADC results are spread over two registers and the result may be continuously updated, addressing any of these ADC result registers causes an inhibition in the updating of the register to prevent corruption. To ensure coherence when reading the most significant and least significant bytes, a MSBY register read causes the corresponding LSBY register value to be stored into a shadow register. Reading the LSBY register will then return the value stored in the LSBY shadow register.

There are three ADC voltage result register pairs and one ADC temperature result register pair, as described below:

- VDD\_AVG\_MSN, VDD\_AVG\_LSBY: These registers hold the 12-bit filtered average voltage reading. The IIR averaging low-pass filter time constant is set by the ADC\_CC\_CTRL.ADC\_IIR\_TAU bitfield (time constant = 2<sup>ADC\_IIR\_TAU</sup>). It is recommended to set ADC\_IIR\_TAU = 7 to provide the slowest filtering.

- VDD\_MIN\_MSN, VDD\_MIN\_LSBY: These registers hold the 12-bit minimum voltage reading since the device was powered on or since the last ADC\_CLR event.

- VDD\_MAX\_MSN, VDD\_MAX\_LSBY: These registers hold the 12-bit maximum voltage reading since the device was powered on, or since the last ADC\_CLR event.

- TEMP MSN, TEMP LSBY: These registers hold the last 12-bit temperature reading.

When the CMD.ADC\_CLR bit is set, on the next subsequent ADC trigger (whether manual or automatic), all three of the ADC result register pairs will be set to the same read value.

#### **ADC Triggering**

Each ADC triggering will cause a reading of both the voltage and temperature. The ADC readings can be triggered manually or automatically:

- The CMD.ADC START bit can be set to manually trigger an ADC reading.

- The ADC can be configured to trigger automatically based off the number of counted pulse events in all enabled converters by configuring ADC\_CC\_CTRL.ADC\_INTERVAL. If ADC\_INTERVAL > 0, the rate of automatic ADC readings is determined by the number of counted pulse events (2<sup>(ADC\_INTERVAL + 3)</sup>). Note in certain scenarios (e.g., EM2 with very light loading) it is possible to have very long periods of time with few or no pulse events. For that reason, whenever ADC\_INTERVAL > 0, the ADC readings will be updated at a minimum period of four refresh cycles (approximately ~400 msec at room temperature), regardless of the number of counted pulse events. It is recommended to set ADC\_INTERVAL=7.

- If ADC CC CTRL.ADC INTERVAL = 0, no automatic ADC readings will occur.

Because the ADC has multiple uses (both internally and at the application level) and ADC readings consume very little power, it is recommended to always set ADC\_INTERVAL=7 to ensure that ADC readings are always triggered periodically automatically. Some of the uses of the ADC include the following:

- If BB\_CTRL2.BB\_IPK\_NOADJ=0, the ADC is used internally to to adjust the boost converter peak current as the battery voltage drops, providing a near-constant output load current over the entire battery range.

- The ADC is used to determine whether a Low Battery Fault (STATUS\_G.VDD\_LOW) has occurred. The threshold for a Low Battery Fault is set in ADC LIMITS.ADC\_V\_LIM.

- · The battery voltage reading is used to determine the charge per pulse during Coulomb counting.

- The ADC temperature readings are used to optimize the internal bias refresh rate over temperature and to determine whether an Over Temperature Fault (STATUS\_G.TEMP\_FAULT) has occurred (where the threshold for the Over Temperature condition is set by ADC LIMITS.ADC T LIM).

If enabled (i.e., ADC\_CC\_CTRL.ADC\_INTERVAL > 0), the ADC will continue to take measurements in EM0 and EM2 energy modes. In EM4, the ADC will be automatically disabled and no measurement updates will occur.

#### **ADC Calculations**

To convert from the result register values to usable units:

- VDDB (mV) = ((VDD\_xxx\_MSN<<8) + VDD\_xxx\_LSBY) × 1.49

- VDDA (mV) = ((VDD xxx MSN<<8) + VDD xxx LSBY) × 1.01</li>

- Temperature (C) = 40 + (convert\_from\_2s\_complement((TEMP\_MSN<<8) + TEMP\_LSBY) + 2) / 6.04236</li>

#### 3.5 Memory

#### 3.5.1 OTP

The EFP01 has contains OTP memory that is programmed at the factory to load calibration constants and configuration defaults into the registers. The default configuration may be modified after power-up by overwriting the corresponding register via I<sup>2</sup>C write. Additionally, any OTP address can be directly read through register I<sup>2</sup>C accesses.

The out-of-reset default OTP configuration can be restored by three methods:

- 1. A VDDA/VDDB/VBOOST power-cycle, resulting in a POR

- Setting the CMD.OTP REREAD bit. This will cause the EFP01 registers to be overwritten with the OTP defaults.

- 3. Setting the CMD.RESET bit. This will cause the EFP01 registers to be momentarily cleared to 0, and then overwritten with the OTP defaults.

**Note:** When the converter mode bitfields are cleared to 0, any enabled converters or LDOs will be disabled for ~400us, which can result in a supply brown-out. For this reason, use of CMD.OTP\_REREAD is recommended instead.

**Note:** When the EFP01 DCDC B is powering the EFR32 DECOUPLE supply, the out-of-reset mode for DCDC B is Disabled. If the EFR32 is not also getting reset, the EFR32 internal LDO must be re-enabled before resetting the OTP to its default values.

Refer to the OTP Definition section for more details and default OTP programming.

#### 3.5.2 Registers

The EFP01 is controlled and configured via access to its Registers. Register access is supported in all of EFP01's energy modes (i.e., EM0, EM2, and EM4).

Default configuration and calibration register values are automatically loaded from OTP at boot (see 7.2 OTP Defaults).

Refer to the Register Definitions section for more details.

# 3.6 Communications and Other Digital Peripherals

# 3.6.1 Inter-Integrated Circuit Interface (I<sup>2</sup>C)

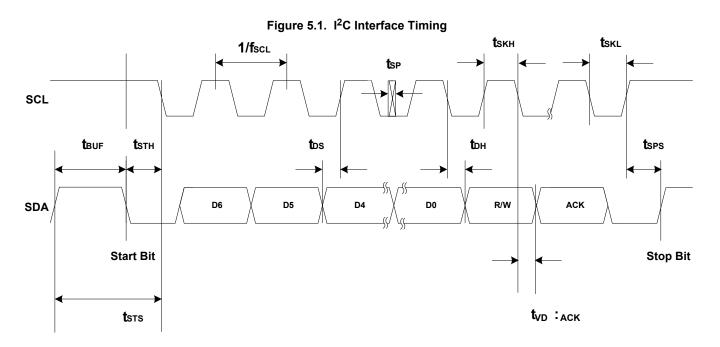

The  $I^2C$  module provides an interface between the EFP01 and the host MCU. It is capable of operating in  $I^2C$  secondary/device mode only, with transmission rates from 10 kbit/s up to 5 Mbit/s, and can function in EM0, EM2, and EM4. The EFP01 uses a fixed  $I^2C$  address of 0x60.

The I<sup>2</sup>C module has internal pull ups on its SDA and SCL pins that are enabled automatically at startup. These internal pull ups can be disabled using the I<sup>2</sup>C\_PU bit in the I<sup>2</sup>C\_CTRL register.

In addition, the I<sup>2</sup>C module provides an optional, non-standard Direct Mode feature to allow fast transitions between Energy Modes (described in 3.3.1 Energy Mode Control). EFP01's internal pull ups are automatically disabled when Direct Mode is enabled.

**Note:** Direct Mode is primarily intended for applications where the EFP01 is the only device on the  $I^2C$  bus - other  $I^2C$  devices may not tolerate the non-standard  $I^2C$  states used by Direct Mode.

#### 3.6.2 Interrupt Output (IRQ)

The EFP01 has an open-drain Interrupt Output (IRQ) that can be used to notify the host processor. Out of reset, an internal pull-up will be enabled on the IRQ pin - this pull-up will always remain enabled and cannot be disabled.

An IRQ will be generated whenever both of the following conditions are true:

- A status flag is set in either the STATUS G or STATUS V registers

- · The flag's corresponding UNMASK bit in either the STATUS\_GM or STATUS\_VM registers is also set to one.

When an IRQ is generated, the IRQ pin will be driven low until any flags that are both unmasked and set are cleared.

By default, only the STATUS\_GM.OTP\_READ\_UNMASK bit is set, which results in an IRQ whenever the OTP is read. Because the OTP is read on every EFP01 power-up and/or reset, the host firmware can use this OTP\_READ flag and resulting IRQ as an indication that an unexpected reset condition has occurred on the EFP01, and that any post-startup configuration needs to be rewritten to its registers.

#### 3.7 System Protection

# 3.7.1 Under-voltage Lockout (UVLO)

When the VDDB voltage falls below the UVLO trip point (consult Electrical Specifications table for the typical value), the EFP01 automatically transitions to an extremely low-power state to minimize power consumption. In this state, only the Power-On Reset (POR) is enabled.

#### 3.7.2 Power-on Reset (POR)

When the VDDB voltage rises above the Rising POR threshhold (consult Electrical Specifications table), the EFP01 automatically loads its OTP programmed defaults into the corresponding registers, at which point any enabled converters will begin regulation. If the VDDB voltage falls below the Falling POR threshhold, the EFP01 will go into reset and all outputs will be disabled.

#### 3.7.3 Over-Voltage Protection

By default in EM0 and EM2 modes, each output has overvoltage protection enabled. When the output voltage on a specific converter is more than ~180 mV higher than the programmed value, an internal ~2 mA load is enabled on the output until the overvoltage condition clears. This feature can be disabled on the VOB output by setting the BK\_CTRL0.BK\_DIS\_OV\_PROT bit.

In OPNs where DCDC B is providing an output that must stay between 1.1 V to 1.2 V, the coarse regulator cannot be enabled in EM4 (as the coarse LDO output can be much higher than 1.2 V). To ensure the supply voltage in EM4 does not increase beyond an acceptable level due to leakage, a simple voltage clamp can be enabled on the VOB output by setting the BK\_CTRL0.CLAMPB bit.

#### 3.7.4 Short Circuit Tolerance

The PFM operation of the DCDC converters along with the programmable peak current limit provide some inherent protection against an output short circuit. In the buck or buck/boost configuration, any output short condition will result in that DCDC output dropping out of regulation, with a maximum output current that is approximately IPK\_BASE/2 (where IPK\_BASE is defined for DCDC A in 3.2.1.2 Peak Current Configuration and DCDC B in 3.2.2.2 Peak Current Configuration).

Similarly, LDO C and LDO B under an output short condition are limited to the configured maximum output current (as defined in 3.2.3.3 Maximum Output Current).

**Note:** Depending on the converter programming, an output short circuit condition for either the DCDC or the LDO output current may still result in an unacceptable rise in on-die temperature. To minimize on-die temperature rise, the PCB designer should maximize thermal connections from the package to the PCB ground planes to optimize heat flow from the package and minimize the  $\theta_{JA}$ .

**Note:** There is no inherent output short circuit protection for DCDC A when it is configured in wired boost mode as described in the 4.1.5 Wired Boost Configuration (EFP0109 & EFP0110), 4.1.4 Single-Cell Boost Configuration (EFP0108), or 4.1.6 Boost Bootstrap Configuration (EFP0111). Shorting the VOA output to ground in one of these configurations will result in an uncontrolled battery discharge through the body diode in the boost powertrain PFET. The current, in this case, is limited only by the system impedances, such as the internal body diode resistance, the inductor resistance, and the battery internal resistance. Any desired short circuit protection for wired boost modes must be implemented in external circuitry.

Firmware can detect and manage an output short condition through the following mechanisms:

- An output short should cause the output to drop out of regulation, resulting in the corresponding VOx\_ISLOW flag being set in the STATUS V register.

- In the worst case, where the output short current has resulted in excessive on-chip power dissapation, the TEMP\_FAULT flag in the STATUS G register will be set to indicate an over temperature condition.

It is recommended that firmware unmask these bits in the STATUS\_VM and STATUS\_GM registers at start-up so that they can generate interrupt requests. Firmware can then respond appropriately to the VOx\_ISLOW and/or TEMP\_FAULT condition(s), e.g. by lowering the peak current or LDOx\_IGAIN setting, increasing the inrush current limit, or disabling the output altogether.

#### 3.8 Startup & Shutdown Behavior

#### 3.8.1 Startup Behavior

Once enabled, the EFP01's DCDC and LDO outputs will immediately begin switching to ramp up to the target output voltage without any soft-start mechanisms (besides the current limit, if enabled, for DCDC A or DCDC B).

#### 3.8.2 Shutdown Behavior

The outputs of all disabled DCDCs and LDOs are held in a high-impedance state. Note that if an output was first enabled, and then disabled, the original output voltage may be retained by the output capacitor(s) for a long period of time depending on output load current.

When the DCDC A converter is disabled on devices configured for the Wired Boost, Single-Cell Boost, or Boost Bootstrap configurations, the body diode in the boost powertrain becomes forward-biased once the VOA output voltage drops below the battery voltage. In these configurations, the VOA output (less a diode drop) tracks the battery voltage when DCDC A is disabled.

# 4. Typical Connection Diagrams

#### 4.1 Device Configurations

The EFP01's flexible configuration options support a wide variety of input supplies and output voltages.

Consult AN1187: EFP01 Hardware Design Considerations for additional information, including reference schematics and layout recommendations.

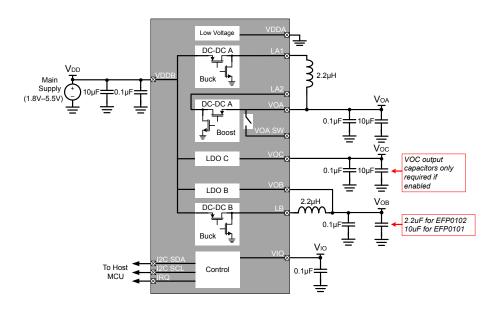

#### 4.1.1 Wired Buck Configuration (EFP0101 & EFP0102)

The wired buck configuration is targeted at batteries with a nominal voltage above 2.5V. In this mode, DCDC A bucks the supply voltage to a lower voltage.

The wired buck configuration is suitable for a wide range of batteries and input supplies. For example:

- Single lithium thionyl chloride (Li/SOCl<sub>2</sub>) primary cell (3.0 to 3.65V)

- Single li-ion/li-polymer (typically LiCoO<sub>2</sub>) rechargeable batteries (2.7 to 4.35V)

- Single lithium iron phosphate (LiFePO<sub>4</sub>) rechargeable battery (2.5 to 3.65V)

- Line power / USB (≤ 5.5V)

The supported operating mode settings for each converter in this configuration are shown below:

**Table 4.1. Supported Operating Mode Settings**

| Converter / LDO | Operating Mode Bitfield | Supported Modes                         |

|-----------------|-------------------------|-----------------------------------------|

| DCDC A          | BB_CTRL3.BB_MODE        | WiredBuck                               |

| DCDC B          | BK_CTRL1.BK_MODE        | Disabled, BuckOnly, BuckLDO, or LDOOnly |

| LDO C           | LDOC_CTRL.LDOC_ENA_SA   | Enabled or Disabled                     |

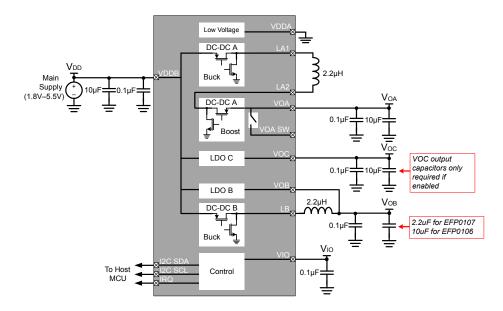

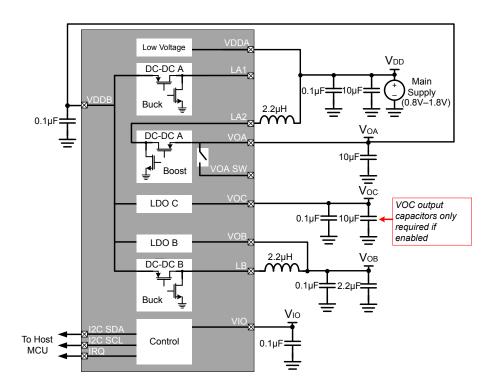

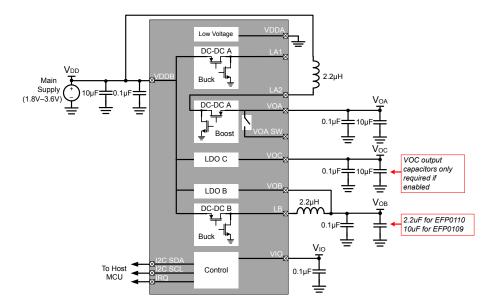

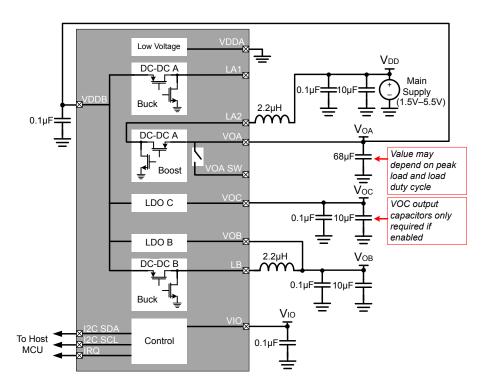

Typical power supply connections for a wired buck configuration are shown below.

Figure 4.1. Wired Buck Configuration

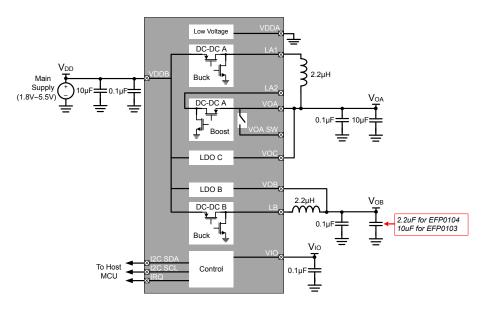

# 4.1.2 Wired Buck with LDO C Configuration (EFP0103 & EFP0104)