# Si7060 数据表

Si7060 系列 I<sup>2</sup>C 温度传感器拥有高转换速度(典型值 143 微秒), 可编程温度过高或 过低中断, 以及 200 毫秒 (典型值) 采样时间的中断极性。

输出的作用是比较器,也就是说,对于每个新温度采样,输出引脚都会变高或变低。输出 设置为开放漏极以支持有多个传感器或组件的 wire-OR。

Si7060 启动的额定温度阈值为 79.8°C, 复位阈值为 75°C, 但这些值是可编程的。

Si7060 的运行与工业标准部件相似,但功率更低,且在许多情况下精度更高。它还能在 自主采样模式下运行。

## 应用:

- HVAC/R

- 恒温器

- 大型家用电器

- 计算机设备

- 资产跟踪

- 电池保护

- Reconnine Notes

## 特性:

- 超过 ± 1 ° C 精度

- 超过 ± 0.1 ° C 可重复性

- 宽工作电压: 1.7 至 5.5 V

- 低功耗: 500 nA

- 超低功耗的睡眠模式: 50 nA

- 120 接口

- 可配置的警报输出

- 4 个出厂可配置的 I<sup>2</sup>C 地址

- 包选项:

- S0T23-5

## 1. Functional Description

The Si7060 family of I<sup>2</sup>C temperature sensors measure and digitize the local temperature at the device. 4 modes of operation are possible:

#### Sleep Mode:

This ultra-low power mode of operation is useful when temperature measurements are made infrequently and the lowest possible power is desired. In this mode, the part will remain in sleep mode until it receives a command over I<sup>2</sup>C to wake up and make a measurement. After this measurement, the part will go back to sleep.

The sleep bit is the 'master' bit. Once this bit is set, the sensor enters its sleep mode regardless of the other register configurations. Once the part is woken up by  $I^2C$ , all registers are loaded to their default value, except for 0xC6 and 0xC7, which can be saved by the usestore bit.

## How to Configure:

sleep = 1

stop = X

sltimeena = X

### **Autonomous Sampling Mode:**

In this mode of operation, the device will make measurements at a factory set rate of 5 Hz (every 200 ms). By default the part enters the Autonomous Sampling Mode upon powerup. The sensor wakes up, performs a temperature conversion, updates the output accordingly, and then goes back to sleep.

## **How to Configure:**

sleep = 0

stop = 0

sltimeena = 1 (default state after wake-up)

#### **Active Mode:**

In this mode of operation, measurements can be commanded, and the numerical value of the temperature can be read.

#### **How to Configure:**

sleep = 0

stop = 0

sltimeena = X

oneburst = 1

The stop bit will be set to 1 once the measurement is complete.

Table 1.1. Summary of Different States

| Mode       | Sleep | Stop | SItimeena |

|------------|-------|------|-----------|

| Sleep      | 1     | X    | х         |

| Autonomous | 0     | 0    | 1         |

The output pin is designed to be an open drain output, which allows you to connect multiple devices in parallel to trigger an alert. The output is driven low once the temperature crosses the operate point, and released once it goes below the release point. The temperature operate and release points are factory set to 80 °C and 75 °C but these values can be adjusted by setting the bit usestore to 1 and adjusting the data in registers 0xC6 and 0xC7 as will be described later. It is possible to adjust the output pin polarity so it goes high or low as temperature increases.

## 2. I2C Interface

The Si7060 complies with "fast" mode I<sup>2</sup>C operation and 7-bit addressing at speeds up to 400 kHz.

The I<sup>2</sup>C address is factory programmed to one of 4 values 0x30, 0x31, 0x32, or 0x33 (0110000b through 0110011b).

At power-up the registers are initialized, as will be described in the register definitions, and then they can be read or written in standard fashion for I<sup>2</sup>C devices.

The host command for writing an I<sup>2</sup>C register is:

START Address W ACK register ACK data ACK STOP

The host command for reading an I<sup>2</sup>C register is:

START Address W ACK register ACK Sr Address R Data NACK\* STOP

\*NACK by host

Where:

START is SDA going low with SCL high

sr is a repeated START

Address is 0x30 up to 0x33.

0 indicates a write and 1 indicates a read.

ACK IS SDA low.

Data is the Read or Write data.

NACK is SDA high.

STOP is SDA going high with SCL high.

Writing or Reading of sequential registers can be supported by setting the arautoinc bit of register 0xC5 (see register description). In the case of a read sequence where the arautoinc bit has been set, the data can be ACK'd to allow reading of sequential registers. For example, a two byte read of the conversion data in registers 0xC1 and 0XC2 would be:

START Address W ACK 0xC1 ACK Sr Address ACK data ACK\* data NACK\* STOP

\*ACK/NACK by host

To wake a part from sleep mode or to interrupt a measurement loop from idle mode, send the sequence:

START Address W ACK STOP

In this case, if the host continued with a register write, the Si7060 would NACK which would be unexpected. Additionally, the following sequence can be used to wake the part up or to interrupt a measurement loop:

START Address R ACK data NACK\* STOP

\*NACK by host

In this case, the Si7060 will produce 0xFF for the data. Allow for 10  $\mu$ sec between the ACK of the address and the next START for the Si7060 to wake from sleep. In most cases, this will happen automatically, due to the 400 KHz maximum speed of the I<sup>2</sup>C bus. The sequence will put the part in idle mode with the stop bit set.

To make a single conversion, having woken the part, set the <code>oneburst</code> bit of register 0xC4 to 1 and the <code>stop</code> bit to 0. The <code>stop</code> bit resets to 1 by the time the measurement is complete.

To put the part back to sleep after reading the data, set the stop bit to 0.

Putting the part to sleep with the sleep bit = 0 will result in the mode of operation where the temperature is sampled every 200 msec, and the output pin will toggle at the temperature threshold points as defined by registers 0xC6 and 0xC7 (assuming the usestore bit is also set)—that is, write 0x08 to 0xC4.

If ultra-low power sleep with no sampling is desired, set the stop bit to 0 and the sleep bit to 1—that is, write 0x00 or 0x09 (to retain the settings of 0xC6 and 0xC7) to 0xC4.

## 2.1 Operation at Very Slow I<sup>2</sup>C Bus Speeds

If the Si7060 is put to sleep with the sleep timer enabled, there will be one measurement done prior to sleep with the settings as configured in the wake period (i.e., operate and release points). This measurement starts at the falling edge of SCL prior to the ACK of the write that puts the part to sleep (i.e., writing 0x80 to register 0xC4). When the measurement concludes, the output pin will be set high or low depending on the measurement results, and the part will enter the sleep timer state.

In the sleep timer state, SDA will hold state until the next wake (either by host or due to the sleep timer, which is typically 200 msec). Thus, it is important that the ACK concludes prior to entering the sleep state, or SDA will hold low until the next wake. SDA is released at the falling edge of SCL, at the completion of the ACK time. This takes 140 µsec, and, therefore, the I<sup>2</sup>C clock speed must be fast enough that the time from SCL falling prior to ACK to SCL falling after ACK must be less than 140 usec. Depending on the host timing for this portion of the I<sup>2</sup>C sequence, this corresponds to an I<sup>2</sup>C speed of greater than 7 KHz.

For very low I<sup>2</sup>C speeds, < 7KHz where this could be an issue, if the sleep timer function is not needed, write the sleep bit of register 0xC4 to put the part to sleep. If the sleep timer is not running, there is no measurement prior to sleep. SDA is released at the completion of the ACK, and the part will enter the sleep state without the sleep timer running.

## 2.2 Measuring Temperature Over I<sup>2</sup>C

The actual temperature of the device can be calculated by reading the Dspsigm and Dspsigl registers over I2C, which correspond to the most significant and least significant bytes of the temperature measurements respectively. The complete 15b unsigned result is 256 \*Dspsigm[6:0]+Dspsigl[7:0].

A result of 16384 means the temperature is 55°C. More negative results mean lower temperature, and more positive results mean higher temperature. Temperature is calculated from the formula:

$T (^{\circ}C) = 55 + (256*Dspsigm[6:0] + Dspsigl[7:0] - 16384)/160$

Read the register interface section for more details.

## 3. Register Interface

The Si7060 has 9 registers. 0xC0 through 0xC9 not including 0xC3.

|      | 7           | 6          | 5  | 4 | 3         | 2        | 1        | 0         |

|------|-------------|------------|----|---|-----------|----------|----------|-----------|

| 0xC0 |             | chipid (RC | )) |   |           | revid    | (RO)     |           |

| 0xC1 |             |            |    |   | Ospsigm   |          |          |           |

| 0xC2 |             |            |    |   | Dspsigl   |          |          |           |

| 0xC3 |             |            |    | D | o not use |          |          |           |

| 0xC4 | meas(RO)    |            |    |   | usestore  | oneburst | stop     | sleep     |

| 0xC5 |             |            |    |   |           |          | C        | arautoinc |

| 0xC6 | sw_low4temp |            |    |   | sw_op     |          | Q)       |           |

| 0xC7 | 0x          | :3         |    |   | \$        | sw_hyst  |          |           |

| 0xC8 |             |            |    |   |           |          |          |           |

| 0xC9 |             |            |    |   |           | 1        | 1        | slTimeena |

| 0xE1 |             |            |    | C | tp_addr   | .0,      |          |           |

| 0xE2 |             |            |    | C | otp_data  |          |          |           |

| 0xE3 |             |            |    |   |           |          | otp_read | otp_busy  |

Registers 0xC0 through 0xC2 are read only registers. 0xC0 has the chip and revid information

chipid (RO) - This ID 0x1 for all Si7060 parts.

revid (RO) - This ID 0x4 for revision B.

0xC1 and 0xC2 store the result of a temperature conversion.

Dspsigm - Bits [6:0] are the most significant byte of the last conversion result. The most significant bit is a "fresh" bit, indicating the register has been updated since last read. Reading the Dspsigm register causes the register Dspsig1 to be loaded with the least significant byte of the last conversion result.

Dspsigl - The least significant byte of the last conversion result. Read Dspsigm first to align the bytes. The complete 15b unsigned result is 256\*Dspsigm[6:0]+Dspsigl[7:0].

A result of 16384 means the temperature is 55°C. More negative results mean lower temperature, and more positive results mean higher temperature.

Temperature is calculated from the formula:

$T (^{\circ}C) = 55 + (256*Dspsigm[6:0] + Dspsigl[7:0] - 16384)/160$

This result can go from -47.4 to +157.39 °C. The recommended operating temperatures is -40°C to +125°C; so, the result should never be out of range, but if operated beyond the ratings of the part, the result will clamp at -47.4 to +157.39 °C (i.e., no underflow or overflow).

Oneburst - Setting this bit initiates a single conversion. Set stop = 0 when setting oneburst = 1. The stop bit will be set to 1 when the conversion completes.

stop - Setting this bit causes the control state machine measurement loop to pause after the current measurement burst completes. Once set, clearing this bit restarts the measurement loop.

sleep - Setting this bit causes the part to enter sleep mode after the current measurement burst completes. Once set, clearing this bit restarts the measurement loop.

arautoinc – enables auto increment of the I<sup>2</sup>C register address pointer. This bit is not retained in sleep mode.

sw\_low4temp - determines the polarity of the output pin. The default setting of sw low4temp = 1 means the pin will go low at high temperature, e.g.  $sw_op + hysteresis$ .  $sw_low4temp = 0$  means the pin will go high at low temperature, e.g.,  $sw_op - hysteresis$ .

Usestore - Setting this bit causes the current state of OTP registers for the sw op, sw hyst, sw low4field, and sw fieldpolsel bits to be saved and restored during the next sleep and wakeup sequence instead of using the factory programmed default settings corresponding to 80°C set point and 75°C release point.

sw\_op - this 9 bit number sets the center point of the decision point for temperature high or low. The actual decision point is the center point plus or minus the hysteresis.

sw op of 256 corresponds to a decision point of 55°C. The decision point will go up or down by 0.4°C as sw op increases or decreases from this value.

threshold =  $55C + 0.4^{\circ}C *(sw op -256)$

sw\_hyst - The formula for hysteresis is:

hysteresis =  $0.025^{\circ}C^{*}(8 + sw_hyst[2:0]) \times 2^{sw_hyst[5:3]}$

When sw hyst = 63, the hysteresis is set to zero. These numbers can range from 0.2°C to 44.8°C

The operate point is threshold plus the hysteresis, and the release point is the threshold minus the hysteresis.

The factory default settings are sw\_op = 312 corresponding to a nominal decision point of 77.4°C and sw\_hyst = 28 corresponding to a nominal hysteresis of 2.4°C (operate at 79.8°C and release at 75°C).

slTimeena - Enables the sleep timer. 0 means the part goes into complete sleep once the sleep bit is set. 1 means the parts will wake a factory set interval between 1 and 200 msec, make a measurement, set the output pin value, and return to sleep.

The meas bit of 0xC4 indicates a measurement is in progress.

Table 3.1. Si7060 OTP Memory Map

| ADDR | 7 | 6 | 5  | 4            | 3       | 2 | 1 | 0 |

|------|---|---|----|--------------|---------|---|---|---|

| 0x14 |   |   |    | Base Part N  | lumber  |   |   |   |

| 0x15 |   |   |    | Part Number  | Variant |   |   |   |

| 0x18 |   |   |    | Serial ID [3 | 31:24]  |   |   |   |

| 0x19 |   |   |    | Serial ID [2 | 23:16]  |   |   |   |

| 0x1A |   |   |    | Serial ID [  | 15:8]   |   |   |   |

| 0x1B |   |   | 70 | Serial ID    | [7:0]   |   |   |   |

otp\_addr. This is the OTP memory address to read.

otp data: This is the data contents of the OTP memory once it is read.

otp\_read\_en: This must be set to 1 to initiate an OTP Memory read sequence. The bit auto clears.

otp\_busy: This bit indicates if the OTP is busy. For normal I<sup>2</sup>C reads, the data will be available by the time the read enable bit is set and the data is read, so in most cases this bit is not needed.

Base part number: For the Si7060, the register value is 60.

Part number variant: The variant for the part number Si7060-B00 is 00. For the part number Si7060-B01, the part number variant is 01. The register value equals the part number variant.

## 4. Electrical Specifications

Unless otherwise specified, all min/max specifications apply over the recommended operating conditions

**Table 4.1. Recommended Operating Conditions**

| Parameter    | Symbol          | Test Condition | Min  | Тур | Max | Units |

|--------------|-----------------|----------------|------|-----|-----|-------|

| Power Supply | V <sub>DD</sub> | _              | 1.71 | _   | 5.5 | V     |

| Temperature  | T <sub>A</sub>  | _              | -40  | _   | 125 | °C    |

**Table 4.2. General Specifications**

| Parameter                       | Symbol             | Test Condition                                                       | Min  | Тур      | Max             | Units |

|---------------------------------|--------------------|----------------------------------------------------------------------|------|----------|-----------------|-------|

| Operating Supply Voltage on VDD | V <sub>DD</sub>    | _                                                                    | 1.71 | _        | 5.5             | V     |

| Operating Ambient Temperature   | T <sub>A</sub>     | _                                                                    | -40  | <u>_</u> | 125             | °C    |

| Input Voltage Range             | V <sub>IN</sub>    |                                                                      | 0    |          | V <sub>DD</sub> | V     |

| Input Leakage                   | I <sub>IL</sub>    |                                                                      |      | <0.1     | 1               | μs    |

| Output Voltage Low              | V <sub>OL</sub>    | SCL, SDA IOL = 3mA                                                   |      |          | 0.4             | V     |

|                                 |                    | VDD> 2 V                                                             | 0)   |          |                 |       |

|                                 |                    | SCL, SDA IOL = 2mA                                                   |      |          | 0.2             | V     |

|                                 |                    | VDD> 1.7 V                                                           |      |          |                 |       |

|                                 |                    | SCL, SDA IOL = 6mA                                                   |      |          | 0.6             | V     |

|                                 |                    | VDD> 2 V                                                             |      |          |                 |       |

| Current consumption             | I <sub>DD</sub>    | Sleep timer enabled average IDD at VDD= 3.3V for sample rate = 200ms |      | 0.5      | 1.5             | μΑ    |

|                                 |                    | Sleep mode (typ. 25°C)                                               |      | 50       |                 | nA    |

|                                 |                    | Sleep mode 125°C                                                     |      |          | 1000            | nA    |

|                                 | <i>(</i> ),        | Conversion in progress/ Ac-                                          |      | -        | -               | μΑ    |

|                                 |                    | tive Mode                                                            |      | 600      | 800             |       |

|                                 |                    | VDD = 3.3V                                                           |      | 700      | 1000            |       |

|                                 | _                  | VDD = 5.5V                                                           |      | 440      | 400             |       |

| Conversion Time                 | T <sub>CONV</sub>  |                                                                      |      | 143      | 160             | μs    |

| Sleep Time                      | T <sub>SLEEP</sub> |                                                                      | 160  | 200      | 240             | μs    |

| Wake Up Time                    | T <sub>WAKE</sub>  | Time from VDD> 1.7V to first measurement                             |      |          | 1               | ms    |

**Table 4.3. Output Pin Specifications**

| Parameter          | Symbol            | Test Condition       | Min | Тур | Max | Units                |

|--------------------|-------------------|----------------------|-----|-----|-----|----------------------|

| Output Voltage Low | V <sub>OL</sub>   | IOL = 3mA; VDD> 2V   |     |     | 0.4 | V                    |

|                    |                   | IOL = 2mA; VDD> 1.7V |     |     | 0.2 | V                    |

|                    |                   | IOL = 6mA; VDD> 2 V  |     |     | 0.6 | V                    |

| Leakage            | I <sub>LEAK</sub> | Output High          |     |     | 1   | μA                   |

| Slew Rate          | T <sub>SLEW</sub> | Digital Output Mode  |     | 5   |     | %V <sub>DD</sub> /ns |

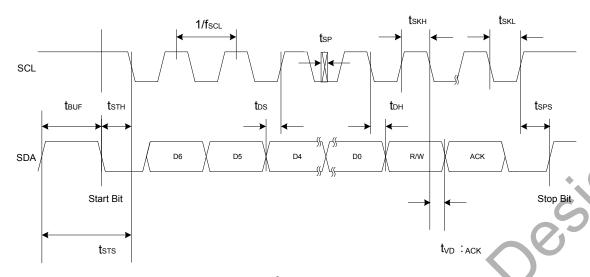

Table 4.4. I2C Interface Specifications

| Parameter                                                        | Symbol              | Test Condition                                           | Min | Тур | Max | Units |

|------------------------------------------------------------------|---------------------|----------------------------------------------------------|-----|-----|-----|-------|

| SCL Clock Frequency                                              | f <sub>SCL</sub>    |                                                          | 0   | 1   | 400 | kHz   |

| Start Condition Hold Time                                        | t <sub>SDH</sub>    |                                                          | 0.6 |     |     | μs    |

| LOW Period of SCL                                                | t <sub>SKL</sub>    |                                                          | 1.3 |     |     | μs    |

| HIGH Period of Clock                                             | t <sub>SKH</sub>    |                                                          | 0.6 |     |     | μs    |

| Set Up Time for a Repeated Start                                 | t <sub>SU:STA</sub> |                                                          | 0.6 |     |     | μs    |

| Data Hold Time                                                   | t <sub>DH</sub>     | X                                                        | 0   |     |     | μs    |

| Data Setup Time                                                  | t <sub>DS</sub>     | 7                                                        | 100 |     |     | μs    |

| Set Up Time for a STOP Condition                                 | t <sub>SPS</sub>    | 70                                                       | 0.6 |     |     | μs    |

| Bus Free Time between STOP and START                             | t <sub>BUF</sub>    | <i>'</i> V <sub>O'</sub>                                 | 1.3 |     |     | μs    |

| Data Valid Time (SCL Low to Data Valid)                          | t <sub>VD;DAT</sub> | 0                                                        |     |     | 0.9 | μs    |

| Data Valid Acknowledge<br>Time (time from SCL Low to<br>SDA Low) | t <sub>VD;ACK</sub> |                                                          |     |     | 0.9 | μѕ    |

| Hysteresis                                                       | thyst               | Digital input hysteresis SDA and SCL                     | 7   |     | 17  | %VDD  |

| Suppressed Pulse Width                                           | t <sub>SP</sub>     | Pulses up to and including this limit will be suppressed | 50  |     |     | ns    |

Figure 4.1. I<sup>2</sup>C Interface Timing

Table 4.5. Temperature Measurement Accuracy

| Parameter                             | Symbol | Test Condition   | Min | Тур   | Max | Units  |

|---------------------------------------|--------|------------------|-----|-------|-----|--------|

| Temperature Measurement               | _      | 0°C to + 70°C    |     | ±0.5  | ±1  | °C     |

| Accuracy                              |        | -40°C to + 125°C |     |       | ±2  | °C     |

| Temperature Measurement Repeatability | _      | RMS Noise        | V   | ±0.05 |     | °C RMS |

**Table 4.6. Thermal Characteristics**

| Parameter                            | Symbol           | Test Condition                            | Value | Units |

|--------------------------------------|------------------|-------------------------------------------|-------|-------|

| Junction to Air Thermal Resistance   | θ <sub>JA</sub>  | JEDEC 4 layer board no airflow<br>SOT23-5 | 212.8 | °C/W  |

| Junction to Board Thermal Resistance | $\theta_{ m JB}$ | JEDEC 4 layer board no airflow<br>SOT23-5 | 45    | °C/W  |

Table 4.7. Absolute Maximum Ratings

| Parameter                             | Symbol           | Test Condition         | Min  | Тур | Max     | Units |

|---------------------------------------|------------------|------------------------|------|-----|---------|-------|

| Ambient Temperature Under Bias        |                  | _                      | -55  |     | 125     | °C    |

| Storage Temperature                   |                  |                        | -65  |     | 150     | °C    |

| Voltage on I/O Pins                   | V <sub>IO</sub>  |                        | -0.3 |     | VDD+0.3 | V     |

| Voltage on VDD with respect to Ground | $V_{DD}$         |                        | -0.3 |     | 6       | V     |

| ESD Tolerance                         | $V_{HBM}$        | Human Body Model       |      |     | 2       | kV    |

|                                       | V <sub>CDM</sub> | Charge Discharge Model |      |     | 500     | V     |

Note: Absolute maximum ratings are stress ratings only. Operation at or beyond these conditions is not implied and may shorten the life of the device, and/or alter its performance.

## 5. Ordering Guide

| Part                                                             | I2C Address                              | Output Type                                 |

|------------------------------------------------------------------|------------------------------------------|---------------------------------------------|

| Si7060-B-00-IV(R)                                                | 0x30                                     | Open Drain                                  |

| Si7060-B-01-IV(R)                                                | 0x31                                     | Open Drain                                  |

| Si7060-B-02-IV(R)                                                | 0x32                                     | Open Drain                                  |

| Si7060-B-03-IV(R)                                                | 0x33                                     | Open Drain                                  |

| Note: The optional (R) is the designator for tape and reel tape. | (3000 pieces per reel). Parts not ordere | ed by the full reel will be supplied in cut |

## 6. Pin Description

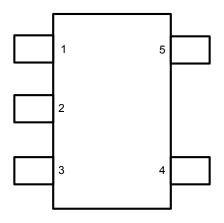

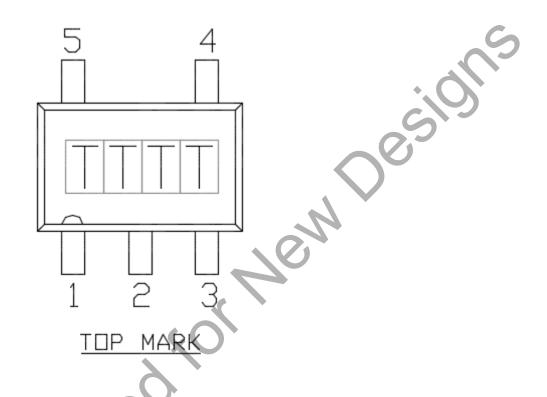

Figure 6.1. Pin Assignments

Table 6.1. 5-Pin SOT23-5 Package

|                 | SOT-23, 5-Pin Top View Figure 6.1. Pin Assignments  Table 6.1. 5-Pin SOT23-5 Package | Jew Design?                       |

|-----------------|--------------------------------------------------------------------------------------|-----------------------------------|

|                 |                                                                                      |                                   |

| Pin Name        | Pin Number                                                                           | Description                       |

| Pin Name<br>SDA | Pin Number                                                                           | Description I <sup>2</sup> C data |

|                 |                                                                                      |                                   |

| SDA             | 1 (0)                                                                                | I <sup>2</sup> C data             |

| SDA<br>GND      | 1 2                                                                                  | I <sup>2</sup> C data Ground      |

## 7. Package Outline

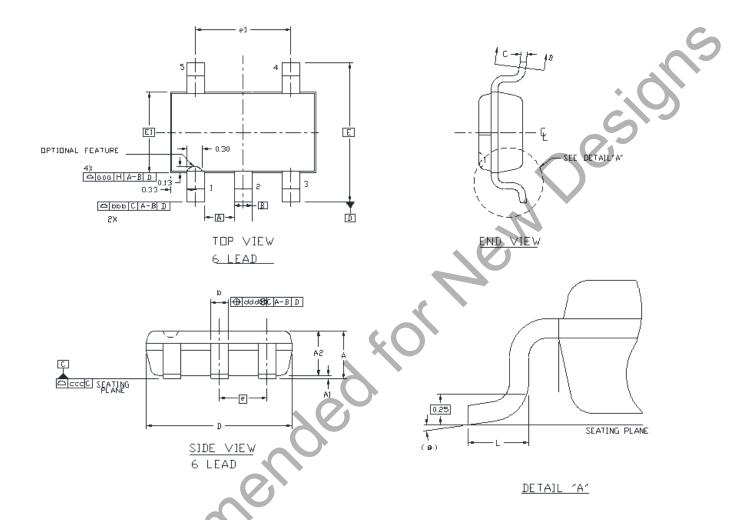

## 7.1 SOT23-5 5-Pin Package

Table 7.1. SOT23-5 5-Pin Package Dimensions

| Dimension | Min      | Max  |

|-----------|----------|------|

| A         |          | 1.25 |

| A1        | 0.00     | 0.10 |

| A2        | 0.85     | 1.15 |

| b         | 0.30     | 0.50 |

| С         | 0.10     | 0.20 |

| D         | 2.90 BSC |      |

| E         | 2.75 BSC |      |

| E1        | 1.60 BSC |      |

| е         | 0.95 BSC |      |

| e1        | 1.90 BSC |      |

| L         | 0.30     | 0.60 |

| L2        | 0.25 BSC |      |

| θ         | 0°       | 8°   |

| aaa       | 0.15     |      |

| bbb       | 0.20     |      |

| ccc       | 0.10     |      |

| ddd       | 0.20     |      |

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing per ANSI Y14.5M-1994.

- 3. This drawing conforms to the JEDEC Solid State Outline MO-193, Variation AB.

- 4. Recommended card reflow profile is per the JEDEC/IPC J-STD-020D specification for Small Body Components.

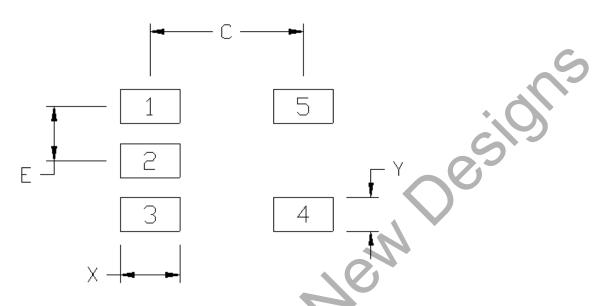

#### 8. Land Patterns

## 8.1 SOT23-5 5-Pin PCB Land Pattern

| Dimension | (mm) |

|-----------|------|

| С         | 2.70 |

| E         | 0.95 |

| X         | 1.05 |

| Y         | 0.60 |

## Note:

## General

- 1. All dimensions shown are in millimeters (mm) unless otherwise noted.

- 2. Dimensioning and Tolerancing is per the ANSI Y14.5M-1994 specification.

- 3. This Land Pattern Design is based on the IPC-7351 guidelines.

- 4. All dimensions shown are at Maximum Material Condition (MMC). Least Material Condition (LMC) is calculated based on a Fabrication Allowance of 0.05 mm.

## Card Assembly

- 1. A No-Clean, Type-3 solder paste is recommended.

- 2. The recommended card reflow profile is per the JEDEC/IPC J-STD-020D specification for Small Body Components.

## 9. Top Marking

## 9.1 SOT23-5 5-Pin Top Marking

Note: TTTT is a manufacturing code.

## 10. Revision History

## Revision 0.1

May 2018

· Initial release.

**Products**www.silabs.com/products

Quality www.silabs.com/quality

Support and Community community.silabs.com

## Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice and limitation to product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Silicon Labs shall have no liability for the consequences of use of the information supplied herein. This document does not imply or express copyright licenses granted hereunder to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any Life Support System without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons.

## Trademark Information

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga®, Bluegiga®, Cockbuilder®, CMEMS®, DSPLL®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember®, EZLink®, EZRadio®, EZRadio®, EZRadioPRO®, Gecko®, ISOmodem®, Micrium, Precision32®, ProSLIC®, Simplicity Studio®, SiPHY®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri, Z-Wave and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. All other products or brand names mentioned herein are trademarks of their respective holders.

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA