# SiWN917 NCP Single Chip Wi-Fi® and Bluetooth® LE Wireless Secure Solutions

Silicon Labs' SiWN917 Network Connectivity Processor (NCP) is a comprehensive multiprotocol wireless sub-system. It has an integrated built-in wireless subsystem, advanced security, and integrated power-management. It has Silicon Labs' ThreadArch<sup>®</sup> 4-Threaded processor running up to 160 MHz. All the networking and wireless stacks run on independent threads of the ThreadArch<sup>®</sup>. The wireless subsystem has low-cost Complementary Metal-Oxide-Semiconductor (CMOS) integration of a multi-threaded Media Access Control (MAC) processor (ThreadArch<sup>®</sup>), baseband digital signal processing, analog front-end, calibration eFuse, 2.4GHz RF transceiver and integrated power amplifier thus providing a fully-integrated solution for a range of embedded wireless applications.

SiWN917 applications include:

- · Smart Home

- · Security Cameras

- HVAC

- Smart Sensors

- · Smart Appliances

- · Health and Fitness

- Pet Tracker

- Smart Cities

- Smart Meters

- Industrial Wearable

- Smart Buildings

- Asset Tracking

- · Smart hospitals

#### KEY FEATURES

- Wi-Fi 6 Single Band 2.4 GHz 20MHz 1x1 stream IEEE 802.11 b/g/n/ax

- · Bluetooth LE 5.4

- Wi-Fi 6 Benefits: TWT for improved efficiency and longer battery life, MU-MIMO/OFDMA for Higher Throughput, network capacity and low latency

- Best in Class Device and Wireless

Security

- WLAN Tx power up to +20 dBm with integrated PA

- Bluetooth LE Tx power up to +19.5 dBm with integrated PA

- WLAN Rx sensitivity as low as -97.5 dBm

- Wi-Fi Standby Associated mode current: 55 µA @ 1-second beacon listen interval

- In-package Flash up to 4MB, and support for optional external Flash

- Embedded Wi-Fi, Bluetooth LE and networking stacks supporting wireless coexistence

- Operating temperature: -40 °C to +85 °C

- Wide operating supply range: 1.71 V to 3.63 V

# 1. Feature List

- Memory

- Embedded Static Random Access Memory (SRAM) up to 672 kB total for ThreadArch^ ${}^{\textcircled{R}}$

- Flash up to 4 MB (in-package), up to 4 MB (External Flash).

- Security

- Secure Boot

- Secure firmware upgrade through boot-loader, Secure OTA.

- · Secure Key storage and HW device identity with PUF

- Secure Zone

- Secure XIP (Execution in place) from flash

- Secure Attestation

- Hardware Accelerators: Advanced Encryption Standard (AES) 128/256/192, Secure Hash Algorithm (SHA) 256/384/512, Hash Message Authentication Code (HMAC), Random Number Generator (RNG), Cyclic Redundancy Check (CRC), SHA3, AES-Galois Counter Mode (GCM)/ Cipher based Message Authentication Code (CMAC), Cha-Cha-poly, True Random Number Generator (TRNG)

- · Software Accelerators: RSA, ECC

- Programmable Secure Hardware Write protect for Flash sectors

- Anti Rollback

- Secure Debug

- Wi-Fi

- Compliant to single-spatial stream IEEE 802.11 b/g/n/ax with single band (2.4 GHz) support

- Support for 20 MHz channel bandwidth for 802.11n and 802.11ax

- Operating Modes: Wi-Fi 4 STA, Wi-Fi 6 (802.11ax) STA, Wi-Fi 4 AP, Enterprise STA, Wi-Fi 6 STA + Wi-Fi 4 AP, Wi-Fi + BLE

- Support for 802.11ax 20 MHz non-AP STA mandatory features (such as OFDMA, MU-MIMO) and optional features of individual Target wake-up time (iTWT), Broadcast TWT (bTWT)<sup>1</sup>, Intra PPDU power save<sup>1</sup>, SU extended range (ER), DCM (Dual Carrier Modulation). DL MU-MIMO, DL/UL OFDMA, MBSSID, BFRP, Spatial Re-use, BSS Coloring, and NDP feedback upto 4 antennas

- Transmit power up to +20 dBm with integrated PA

- · Receive sensitivity as low as -97.5 dBm

- Data Rates: 802.11b: 1, 2, 5.5, 11; 802.11g: 6, 9, 12, 18, 24, 36, 48, 54Mbps; 802.11n: MCS0 to MCS7; 802.11ax: MCS0 to MCS7

- Operating Frequency Range: 2412 MHz 2484 MHz

- PTA Coexistence with Zigbee/Thread/Bluetooth

#### Intelligent Power Management

- Power optimizations leveraging multiple power domains and partitioned sub systems

- Many system-, component-, and circuit-level innovations

and optimizations

- Different Power Modes

- Deep sleep mode with only timer active with and without RAM retention

- Bluetooth

- Transmit power up to +19.5 dBm with integrated PA

- Receive sensitivity LE: -95 dBm, LR 125 Kbps: -106 dBm

- Operating Frequency Range 2.402 GHz 2.480 GHz

- Support LE (1Mbps & 2Mbps) and LR (125Kbps & 500Kbps) rates

- Advertising extensions

- Data length extensions

- LL privacy

- · LE dual role

- BLE acceptlist

- BLE 2 Peripheral & 2 Central connections or 1 Central & 1

Peripheral connection<sup>1</sup>

#### RF Features

- · Integrated baseband processor with calibration memory

- Integrated RF transceiver, high-power amplifier, balun and T/R switch

#### Embedded Wi-Fi Stack

- Support for Embedded Wi-Fi STA mode, Wi-Fi Access point mode and Concurrent (AP+STA) mode

- Supports advanced Wi-Fi Security features: WPA Personal, WPA2 Personal, WPA3 Personal, WPA/WPA2 Enterprise in STA mode

- Networking: Integrated IPv4/IPv6 stack, TCP, UDP, ICMP, ICMPv6, ARP, DHCP Client/Server, DHCPv6 Client, DNS Client, SSL3.0/TLS1.3 Client, SNTP, SNI

- Applications: HTTP/s Client, HTTP/s Server<sup>1</sup>, MQTT/s Client, AWS Client, Azure Client<sup>1</sup>

- Sockets: BSD Sockets, IoT Sockets

- Over-the-Air (OTA) Wireless firmware update

- Provisioning using Wi-Fi AP<sup>1</sup> or BLE

#### Embedded Bluetooth Stack

- Support GAP profile

- Support GATT profile

- Support SMP

- Support LE L2CAP

- Wireless Sub-System Power Consumption

- Wi-Fi 4 Standby Associated mode current: 55 µA @ 1-second beacon listen interval

- Wi-Fi 1 Mbps Listen current: 13 mA

- Wi-Fi LP chain Rx current: 18 mA

- Deep sleep current ~2.5  $\mu A,$  Standby current (384K RAM retention) ~10  $\mu A$

#### Operating Conditions

- Wide operating supply range: 1.71 V to 3.63 V

- Operating temperature: -40 °C to +85 °C

- Software and Regulatory Certifications

- Wi-Fi Alliance: Wi-Fi 4<sup>1</sup>, Wi-Fi 6<sup>1</sup>

- Bluetooth Qualification<sup>1</sup>

- Regulatory pre-certifications (FCC, IC, RED, UKCA, MIC)

#### Note:

- 1. For information about Software roadmap features and additional certification information, contact Silicon Labs for availability and timeline.

- 2. For a detailed list of software features and available profiles, refer to the Software Reference Manuals or contact Silicon Labs for availability.

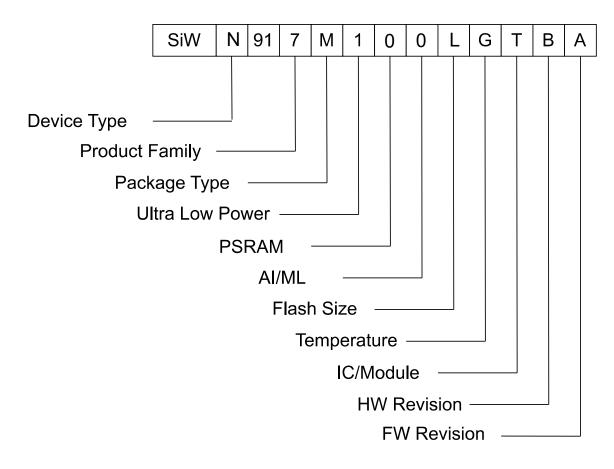

# 2. Ordering Information

Table 2.1. List of OPNs

| Part Number      | Common Features                                                    | Device Type | Flash Size           | Temperature  |

|------------------|--------------------------------------------------------------------|-------------|----------------------|--------------|

| SiWN917M100XGTBA | Wi-Fi 6 I lltra low power IC. 7x7 OFN                              | NCP         | No Stacked Flash     | -40 to 85 °C |

| SiWN917M100LGTBA | Wi-Fi 6 Ultra low power IC, 7x7 QFN, –<br>Integrated 2.4 GHz Radio | NCP         | 4MB Stacked<br>Flash | -40 to 85 °C |

Table 2.2. OPN Decoder

| Field          | Options               |

|----------------|-----------------------|

| Device Type    | T: RCP ( Transceiver) |

|                | N: NCP                |

|                | G: SoC                |

| Product Family | 7: Ultra-low power    |

|                | 5: Ultra-low cost     |

| Package Type   | M: QFN                |

# SiWN917 NCP Single Chip Wi-Fi® and Bluetooth® LE Wireless Secure Solutions Ordering Information

| Field           | Options                    |

|-----------------|----------------------------|

| Ultra Low Power | 0: ULP Features disabled   |

|                 | 1: ULP Features enabled    |

| PSRAM           | 0: No PSRAM Support        |

|                 | 1: External PSRAM          |

|                 | 2: 2 MB Internal PSRAM     |

|                 | 4: 8 MB Internal PSRAM     |

| AI/ML           | 0: Al/ML Features disabled |

|                 | 1: AI/ML Features enabled  |

| Flash Size      | X: NO Internal Flash       |

|                 | L: 4 MB Internal Flash     |

|                 | M: 8 MB Internal Flash     |

| Temperature     | <b>G</b> : -40°C to 85°C   |

|                 | N: -40°C to 105°C          |

| IC/Module       | T: IC Package              |

| HW Revision     | B: Revision B              |

| FW Revision     | A: Revision A              |

# **Table of Contents**

| 1. | Feature List                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 2                      |

|----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 2. | Ordering Information                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | . 4                      |

| 3. | Applications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | . 8                      |

| 4. | Block Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | . 9                      |

| 5. | System Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .11                      |

|    | 5.1 Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          |

|    | 5.2 WLAN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | .11                      |

|    | 5.2.2 Baseband Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                          |

|    | 5.3 Bluetooth       5.3.1 MAC         5.3.1 MAC       5.3.2 Baseband Processing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | .12                      |

|    | 5.4 RF Transceiver                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          |

|    | 5.5 Security Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | .13                      |

|    | 5.6 Embedded Wi-Fi Software                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                          |

|    | 5.7 Power Architecture       5.7.1 Highlights       5.7.1 Highlights       5.7.2 System Power Supply Configurations       5.7.2 System Power Supply Configurations       5.7.3 Power Management       5.7.1 System Power Supply Configurations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .13<br>.13               |

|    | 5.8 Memory Architecture                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                          |

|    | 5.9 Low Power Modes.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | .14                      |

| 6. | Pinout and Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | . 15                     |

|    | 6.1 Pin Diagram       6.1 Normalize         6.2 Pin Description       6.2 Normalize         6.2.1 RF and Control Interfaces       6.2 Normalize         6.2.2 Power and Ground Pins       6.2 Normalize         6.2.3 Peripheral Interfaces       6.2 Normalize         6.2.4 Miscellaneous Pins       6.2 Normalize                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .16<br>.16<br>.17<br>.18 |

| 7. | Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | . 27                     |

|    | 7.1 Absolute Maximum Ratings.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | .27                      |

|    | 7.2 Recommended Operating Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | .28                      |

|    | 7.3 DC Characteristics.       7.3 L Reset Pin       7.3 L Reset Pin | .28<br>.28               |

|    | 7.3.4 SoC Power Management Unit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                          |

| 7.3.5 Thermal Characteristics                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |   |   |   |                                               |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|---|---|-----------------------------------------------|

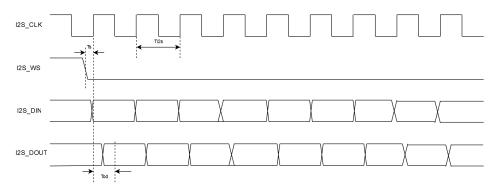

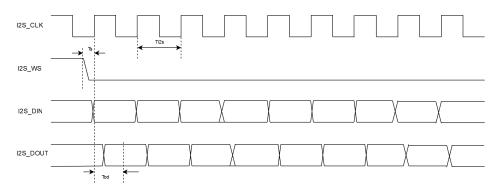

| 7.4 AC Characteristics.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <td></td> <td></td> <td></td> <td>.33<br/>.33<br/>.36<br/>.38<br/>.40<br/>.40<br/>.40</td> |   |   |   | .33<br>.33<br>.36<br>.38<br>.40<br>.40<br>.40 |

| 7.4.7 I2C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   |                                               |

| <ul> <li>7.5 RF Characteristics</li> <li>7.5.1 WLAN 2.4 GHz Transmitter Characteristics</li> <li>7.5.2 WLAN 2.4 GHz Receiver Characteristics on High-Performance (HP) RF Chain</li> <li>7.5.3 WLAN 2.4 GHz Receiver Characteristics on Low-Power (LP) RF Chain</li> <li>7.5.4 Bluetooth Transmitter - Characteristics on High-Performance (HP) RF Chain</li> <li>7.5.5 Bluetooth Transmitter Characteristics on Low-Power (LP) 8 dBm RF Chain</li> <li>7.5.6 Bluetooth Transmitter Characteristics on Low-Power (LP) 0 dBm RF Chain</li> <li>7.5.7 Bluetooth Receiver Characteristics on High-Performance (HP) RF Chain</li> <li>7.5.8 Bluetooth Receiver Characteristics on Low-Power (LP) RF Chain</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            |   |   |   | .45<br>.46<br>.49<br>.50<br>.51<br>.51<br>.52 |

| 7.6 Typical Current Consumption                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   |   |                                               |

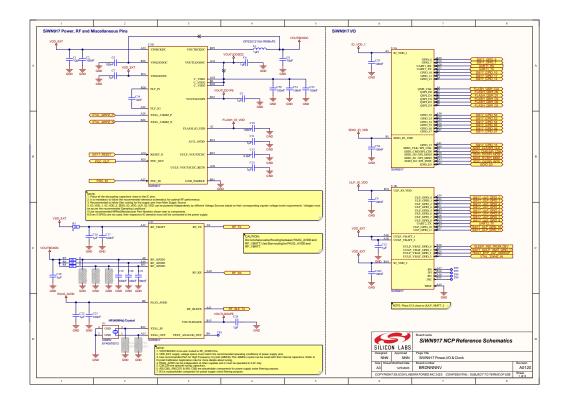

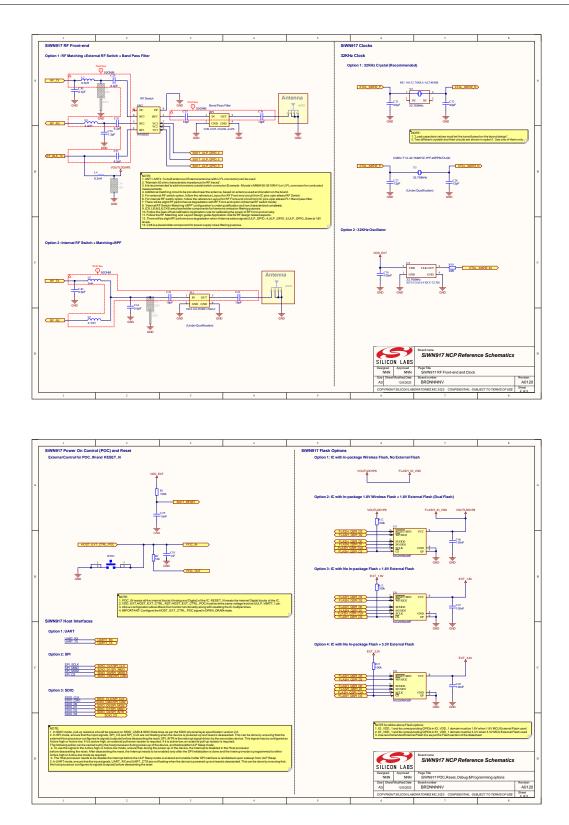

| 8. Reference Schematics, BOM and Layout Guidelines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | • | - |   | .57                                           |

| 8.1 SiWN917 QFN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   | • | .57<br>.59<br>.62                             |

| 8.3 Calibration Requirements                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |   |   |   |                                               |

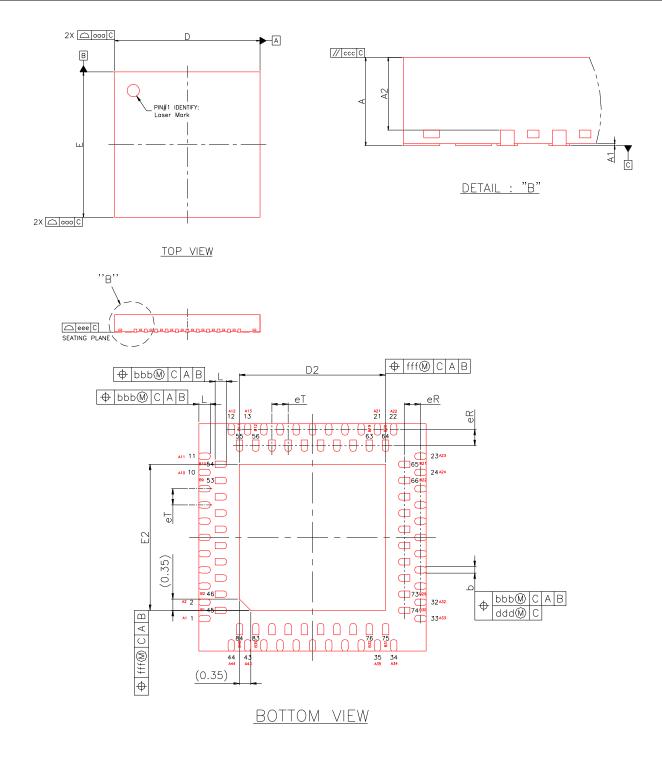

| 9. Package Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |   |   |   | .65                                           |

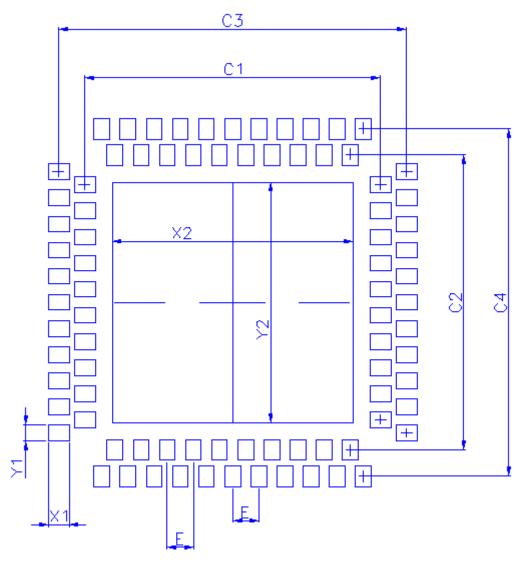

| 9.2 PCB Land Pattern                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |   |   |   |                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |   |   | .70                                           |

# 3. Applications

#### **Smart Home**

Smart Locks, Motion/Entrance Sensors, Water Leak sensors, Smart plugs/switches, Light Emitting Diode (LED) lights, Door-bell cameras, Washers/Dryers, Refrigerators, Thermostats, Consumer Security cameras, Voice Assistants, etc.

#### **Other Consumer Applications**

Toys, Anti-theft tags, Smart dispensers, Weighing scales, Fitness Monitors, Smart Glasses, Blood pressure monitors, Blood sugar monitors, Portable cameras, etc.

#### Other Applications (Medical, Industrial, Retail, Agricultural, Smart City, etc.)

Healthcare Tags, Industrial Wearables, Infusion pumps, Sensors/actuators in Manufacturing, Electronic Shelf labels, Agricultural sensors, Product tracking tags, Smart Meters, Parking sensors, Street LED lighting, Automotive After-market, Security Cameras, etc.

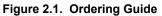

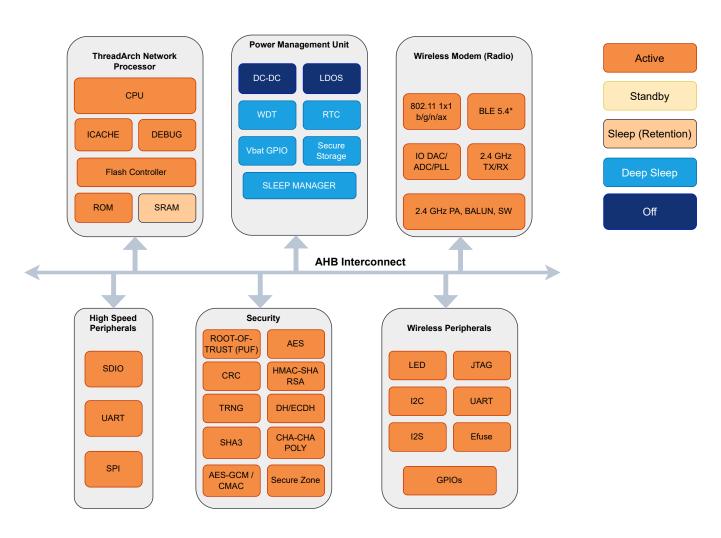

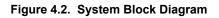

# 4. Block Diagrams

Figure 4.1. SiWN917 Hardware Block Diagram

Figure 4.3. SiWN917 NCP Software Architecture

Note: Customer can connect multiple hosts, but only one host interface can be active after power-on.

# 5. System Overview

#### 5.1 Introduction

SiWN91x NCP includes ThreadArch® 4-Threaded processor running up to 160MHz. All the networking and wireless stacks run on independent threads of the ThreadArch®. In addition, the ThreadArch® subsystem also acts as the secure processing domain and takes care of secure boot, secure firmware update and provides access to security accelerators and secure peripherals through pre-defined APIs. The ThreadArch® based "Networking, Security and Wireless subsystem" have power, clocks/PLLs, bus-matrices, and memory.

#### 5.2 WLAN

- Compliant to single-spatial stream IEEE 802.11 b/g/n/ax with single band (2.4 GHz) support

- Support for 20 MHz channel bandwidth for 802.11n and 802.11ax.

- Operating Modes: Wi-Fi 4 STA, Wi-Fi 6 (802.11ax) STA, Wi-Fi 4 AP, Enterprise STA, Wi-Fi 6 STA + Wi-Fi 4 AP, Wi-Fi + BLE

- Wi-Fi 6 Features: Individual Target wake-up time (iTWT), Broadcast TWT (bTWT),SU extended range (ER), DCM (Dual Carrier Modulation), DL MU-MIMO, DL/UL OFDMA, MBSSID, BFRP, Spatial Re-use, BSS Coloring, and NDP feedback up to 4 antennas

- Integrated PA

- Data Rates-802.11b: up to 11 Mbps; 802.11g: up to54 Mbps; 802.11n: MCS0 to MCS7; 802.11ax: MCS0 to MCS7

- Operating Frequency Range: 2412 MHz 2484 MHz

#### 5.2.1 MAC

- · Conforms to IEEE 802.11b/g/n/j/ax standards for MAC

- · Hardware accelerators for AES

- WPA, WPA2, WPA3 and WMM support

- · AMPDU aggregation for high performance

- · Firmware downloaded from host based on application

- · Hardware accelerators for DH (for WPS) and ECDH

#### 5.2.2 Baseband Processing

- Supports 11b: DSSS for 1, 2 Mbps and CCK for 5.5, 11 Mbps

- · Supports all OFDM data rates

- 802.11g: 6, 9, 12, 18, 24, 36, 48, 54 Mbps

- 802.11ax, 802.11n: MCS 0 to MCS 7

- · High-performance multipath handling in OFDM, DSSS, and CCK modes

#### 5.3 Bluetooth

**Key Features**

- · Transmit power up to +20 dBm with integrated PA

- Receive sensitivity LE: -95 dBm, LR 125 Kbps: -106 dBm

- Operating Frequency Range 2.402 GHz 2.480 GHz

- Support LE (1 Mbps & 2 Mbps) and LR (125 Kbps & 500 Kbps) rates

- Advertising extensions

- · Data length extensions

- · LL privacy

- LE dual role

- · BLE acceptlist

- BLE 2 peripheral & 2 central connections or 1 central & 1 peripheral connection, 8 peripheral & 2 central

- BLE Mesh (4 nodes) for limited switch use case.

#### 5.3.1 MAC

#### Link Manager

- · Creation, modification & release of physical links

- · Connection establishment between Link managers of two Bluetooth devices

- Link supervision is implemented in Link Manager

- · Link power control is done depending on the inputs from Link Controller

- · Enabling & disabling of encryption & decryption on logical links

- · Support for security using AES hardware accelerator

#### Link Controller

- · Encodes and decodes header of BLE packets

- · Manages flow control, acknowledgment, re-transmission requests, etc.

- · Stores the last packet status for all physical transports

- · Indicates the success status of packet transmission to upper layers

- Indicates the link quality to the LMP layer

#### **Device Manager**

- Executes HCI Commands

- Controls Scan & Connection processes

- · Controls all BLE Device operations except data transport operations

- BLE Controller state transition management

- Anchor point synchronization & management

- Scheduler

#### 5.3.2 Baseband Processing

Supports BLE 1Mbps, 2Mbps and long range 125kbps, 500kbps

#### 5.4 RF Transceiver

- SiWx917 features two highly configurable RF transceivers supporting WLAN 11b/g/n/ax and Bluetooth LE wireless protocols. Both RF transceivers together operating in multiple modes covering High Performance (HP) and Low Power (LP) operations. List of operating modes are given in next section.

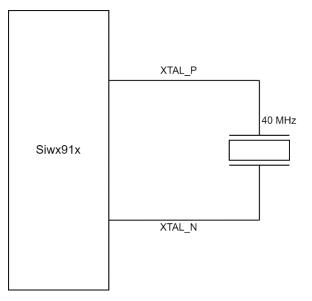

- It contains two fully integrated fractional-N frequency synthesizers having reference from internal oscillator with 40MHz crystal. One of the synthesizer is a low power architecture which also caters single-bit data modulation feature for Bluetooth LE protocols.

- There are two transmitter chains in the chip. First one uses a direct conversion architecture getting carrier signal from the high-performance frequency synthesizer. It contains an on-chip balun and its output is terminated as single-ended output at "RF\_TX" pin. This transmitter supports all the mentioned WLAN protocols, and Bluetooth LE protocol for high output power. The second transmitter is a low power architecture for supporting constant envelope modulation formats. This has two outputs differentiated by their maximum output power level. The 0dBm output is shared with "RF\_RX" pin and the 8 dBm output is terminated at "RF\_BLETX" pin.

- The receiver contains two front end paths with a configurable common LNA catering HP and LP operations. This also has two analog base-band blocks where one is zero-IF architecture supporting all the mentioned WLAN protocols and the other one is low-IF architecture supporting Bluetooth LE. Input to the pin is "RF\_RX" sharing with 0dBm Tx output.

- · Impedance matching for each RF pins need to be done separately for optimum performance.

#### 5.4.1 Receiver and Transmitter Operating Modes

The radio is highly configurable. The available radio operating modes are

- WLAN HP TX WLAN High-Performance Transmitter

- WLAN HP RX WLAN High-Performance Receiver

- WLAN LP RX WLAN Low-Power Receiver

- · BLE HP TX Bluetooth LE High-Performance Transmitter

- · BLE HP RX Bluetooth LE High-Performance Receiver

- BLE LP TX Bluetooth LE Low-Power Transmitter

- · BLE LP RX Bluetooth LE Low-Power Receiver

#### 5.5 Security Features

- Secure Boot

- Secure OTA Firmware update

- TRNG : Generates high-entropy random numbers based on RF noise, increasing the effort/time needed to expose secret keys

- Secure Zone

- · Secure Key storage : HW device identity and key storage with PUF

- Secure Debug

- Anti Rollback : Firmware downgrade to a lower version is prohibited through OTP to prevent the use of older, potentially vulnerable FW version

- Secure XIP from flash with XTS/CTR mode

- · Secure Attestation : Allows a device to authenticate its identity using a cryptographically signed token and exchange of secret keys

- · Hardware Accelerators: AES128/256/192, SHA256/384/512, HMAC, RNG, CRC, SHA3, AES-GCM/ CMAC, ChaCha-poly

- Software Accelerators: RSA and ECC

- Programmable Secure Hardware Write protect for Flash sectors

#### 5.6 Embedded Wi-Fi Software

- The wireless software package supports Embedded Wi-Fi (802.11 b/g/n/ax) Client mode, Wi-Fi Access point mode (up to 4 clients), and Enterprise Security in client mode.

- The software package includes complete firmware and application profiles.

- · It has a wireless coexistence manager to arbitrate between protocols.

#### 5.6.1 Security

Wireless software supports multiple levels of security capabilities available for the development of IoT devices.

- Accelerators: AES128/256

- WPA/WPA2/WPA3-Personal, WPA/WPA2 Enterprise for Client

#### 5.7 Power Architecture

The Power Control Hardware implements the control sequences for transitioning between different power states (Active/Standby/Sleep/Shutdown).

#### 5.7.1 Highlights

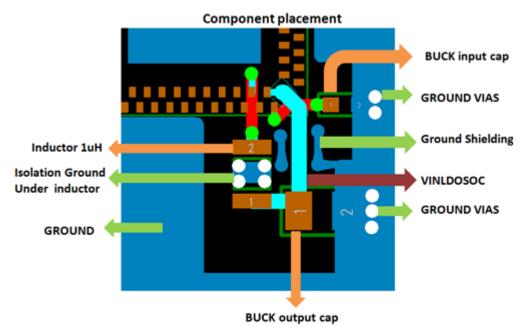

- Two integrated buck switching regulators (High performance and ULP) to enable efficient Dynamic Voltage Scaling across wide operating mode currents ranging from <1µA to 300mA</li>

- · Multiple voltage domains with Independent voltage scaling of each domain.

- Fine grained power-gating including peripherals, buses and pads, thereby reducing power consumption when the peripheral/buses/ pads are inactive.

- · Flexible switching between different Active states with controls from Software.

- · Hardware based wakeup from Standby/Sleep/Shutdown states.

- All the peripherals are clock gated by default thereby reducing the power consumption in inactive state.

- Low wakeup times as configurable by Software.

#### 5.7.2 System Power Supply Configurations

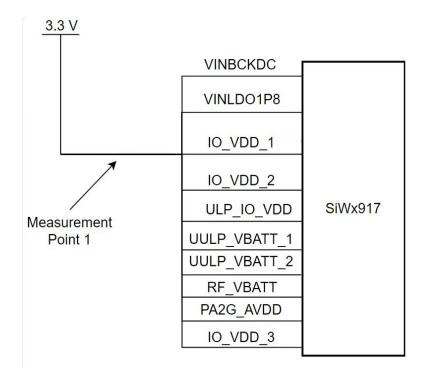

SiWx917 chipsets support highly flexible power supply configurations for various application scenarios. Two application scenarios are listed below.

- 3.3 V single supply A single 3.3 V supply derived from the system PMU can be input to all I/O supplies.

- 1.8 V and 3.3 V supply A 1.8 V supply derived from the system PMU can be input to all I/O supplies except PA2G\_AVDD. A 3.3 V supply derived from system Power Management Unit (PMU) can be fed to the power amplifier supply pin PA2G\_AVDD. In this mode, I/Os can operate at 1.8 V without a penalty in the maximum transmit power

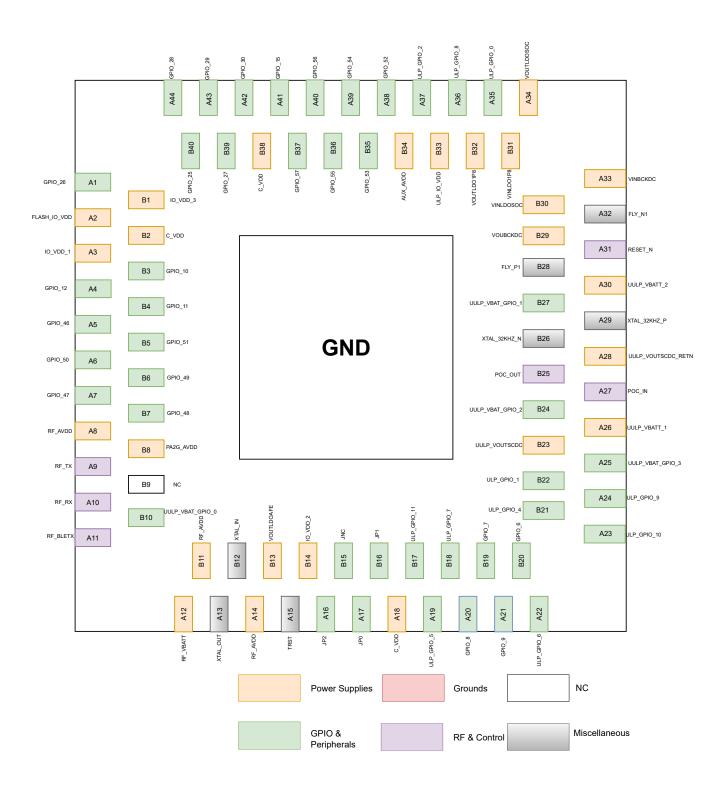

#### 5.7.3 Power Management

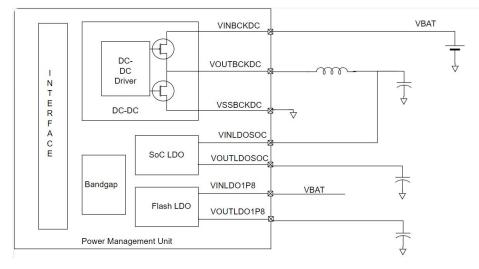

The SiWx917 chipsets have an internal power management subsystem, including DC-DC converters and linear regulators. This subsystem generates all the voltages required by the chipset to operate from a wide variety of input sources.

- · LC DC-DC switching converter for RF and digital blocks

- Input voltage (1.8 V or 3.3 V) on pin VINBCKDC

- Output 1.45 V and 300 mA maximum load on pin VOUTBCKDC

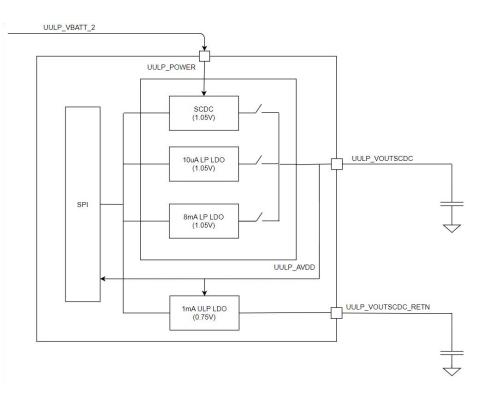

- SC DC-DC Switching converter for Always-ON core logic domain

- Input voltage (1.8 V or 3.3 V) on pin UULP\_VBATT\_1 and UULP\_VBATT\_2

- Output 1.05 V

- SoC LDO Linear regulator for digital blocks

- Input 1.45 V from LC DC-DC or external regulated supply on pin VINLDOSOC

- · Output 1.15 V and 300 mA maximum load on pin VOUTLDOSOC

- · LDO RF and AFE Linear regulator for RF and AFE

- Input 1.45 V from LC DC-DC or external regulated supply on pin RF\_AVDD

- Output 1.15 V and 20 mA maximum load on pin VOUTLDOAFE

- · Flash LDO Linear regulator for In-package flash and external flash

- Input voltage (1.8 V or 3.3 V) on pin VINLDO1P8

- Output 1.8 V and 100 mA maximum load on pin VOUTLDO1P8

#### 5.8 Memory Architecture

There are on chip Read Only Memory(ROM), Random Access Memory(RAM) and off chip FLASH connectivity. Sizes of ROM/RAM/ FLASH will vary depending on the chip configuration.

The ThreadArch® processor has following memory:

- Embedded SRAM up to 672 kB total for ThreadArch®

- · 448Kbytes of ROM which holds the Secure primary bootloader, Network Stack, Wireless stacks and security functions

- 16Kbytes of Instruction cache (I cache) enabling eXecute In Place (XIP) with quad SPI flash memory.

- Flash up to 8 MB (embedded), up to 16 MB (External Flash)

- eFuse of 1024 bytes(used to store primary boot configuration, security and calibration parameters)

#### 5.9 Low Power Modes

It supports Ultra-low power consumption with multiple power modes to reduce system energy consumption.

- Dynamic Voltage and Frequency Scaling

- Deep sleep (ULP) mode with only the sleep timer active with and without RAM retention

- · Wi-Fi standby associated mode with automatic periodic wake-up

- Automatic clock gating of the unused blocks or transit the system from Normal to ULP mode.

#### 5.9.1 ULP Mode

In Ultra Low Power mode, the deep sleep manager has control over the other subsystems and TA processors and controls their active and sleep states. During deep sleep, the always-on logic domain operates on a lowered supply and a 32 KHz low-frequency clock to reduce power consumption. The ULP mode supports the following wake-up options:

- Timeout wakeup Exit sleep state after programmed timeout value.

- GPIO Based Wakeup: Exit sleep state when GPIO goes High/Low based on programmed polarity.

- RTC Timer wakeup Exit Sleep state on timeout of RTC timer

- WatchDog Interrupt based wakeup Exit Sleep state upon watchdog interrupt timeout.

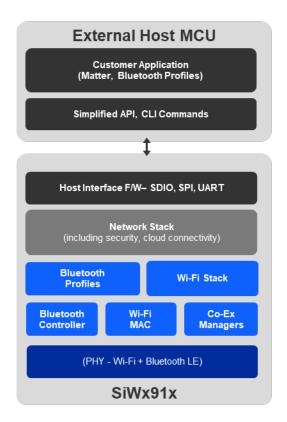

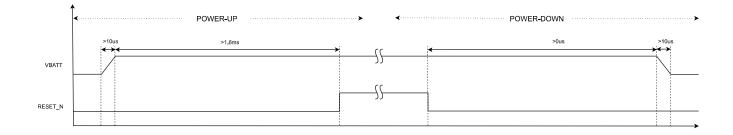

# 6. Pinout and Pin Description

#### 6.1 Pin Diagram

#### 6.2 Pin Description

# 6.2.1 RF and Control Interfaces

# Table 6.1. Chip Packages - RF and Control Interfaces

| Pin Name   | QFN Pin Number | QFN I/O Supply Do-<br>main | Direction | Initial State (Power<br>up, Active Reset) | Description                                                                                                                                                                      |

|------------|----------------|----------------------------|-----------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RF_TX      | A9             | PA2G_AVDD                  | Output    | NA                                        | 2.4 GHz RF Output.                                                                                                                                                               |

| RF_RX      | A10            | RF_AVDD                    | Inout     | NA                                        | 2.4GHz RF Input for<br>WLAN and BLE. It<br>can also be used as<br>BLE 0 dBm RF Out-<br>put                                                                                       |

| RF_BLETX   | A11            | RF_AVDD                    | Output    | NA                                        | BLE 8 dBm RF Out-<br>put                                                                                                                                                         |

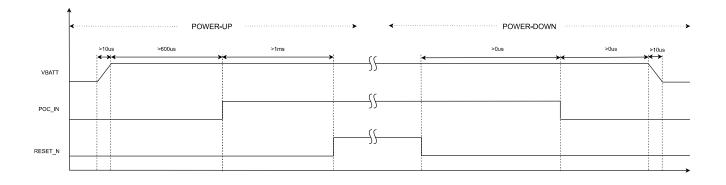

| RESET_N    | A31            | UULP_VBATT_2               | Input     | NA                                        | Active-low reset<br>asynchronous reset<br>signal. RESET_N<br>will be pulled low if<br>POC_IN is low.                                                                             |

| POC_IN     | A27            | UULP_VBATT_1               | Input     | NA                                        | This is an input to<br>the chip. It should be<br>made high only after<br>supplies are valid to<br>ensure the IC is in<br>safe state until valid<br>power supply is<br>available. |

| POC_OUT    | B25            | UULP_VBATT_1               | Output    | NA                                        | This is internally<br>generated. Initially, it<br>is low. But it be-<br>comes high when<br>the supplies<br>(UULP_VBATT_1,<br>UULP_VOUTSCDC)<br>are valid.                        |

| ULP_GPIO_0 | A35            | ULP_IO_VDD                 | Inout     | NA                                        | Antenna select pin<br>for External switch<br>configuration. Please<br>refer to Reference<br>schematics for more<br>info.                                                         |

| ULP_GPIO_4 | B21            | ULP_IO_VDD                 | Inout     | NA                                        | Antenna select pin<br>for External switch<br>configuration.Please<br>refer to Reference<br>schematics for more<br>info.                                                          |

| ULP_GPIO_5 | A19            | ULP_IO_VDD                 | Inout     | NA                                        | Antenna select pin<br>for External switch<br>configuration. Please<br>refer to Reference<br>schematics for more<br>info.                                                         |

#### 6.2.2 Power and Ground Pins

| Pin Name               | Туре   | QFN Pin Num-<br>ber | Direction | Description                                                                                                        |

|------------------------|--------|---------------------|-----------|--------------------------------------------------------------------------------------------------------------------|

| UULP_VBATT_1           | Power  | A26                 | Input     | Always-on VBATT Power supply to the UULP domains.                                                                  |

| UULP_VBATT_2           | Power  | A30                 | Input     | Always-on VBATT Power supply to the UULP domains.                                                                  |

| RF_VBATT               | Power  | A12                 | Input     | Always-on VBATT Power supply to the RF.                                                                            |

| VINBCKDC               | Power  | A33                 | Input     | Power supply for the on-chip Buck.                                                                                 |

| VOUTBCKDC              | Power  | B29                 | Output    | Output of the on-chip Buck.                                                                                        |

| VINLDOSOC              | Power  | B30                 | Input     | Power supply for SoC LDO. Connect to VOUTBCKDC as per the Reference Schematics.                                    |

| VOUTLDOSOC             | Power  | A34                 | Output    | Output of SoC LDO.                                                                                                 |

| VINLDO1P8              | Power  | B31                 | Input     | Power supply for 1.8V LDO.                                                                                         |

| VOUTLDO1P8             | Power  | B32                 | Output    | Output of 1.8V LDO which is used for Flash supply                                                                  |

| VOUTLDOAFE             | Power  | B13                 | Output    | Output of AFE LDO.                                                                                                 |

| FLASH_IO_VDD           | Power  | A2                  | Input     | I/O Supply for Flash. Connect to VOUTL-<br>DO1P8 as per the Reference Schematics.                                  |

| IO_VDD_1               | Power  | A3                  | Input     | I/O Supply for GPIOs. Refer to the GPIOs<br>section for details on which GPIOs have<br>this as the I/O supply.     |

| IO_VDD_2               | Power  | B14                 | Input     | I/O Supply for GPIOs. Refer to the GPIOs section for details on which GPIOs have this as the I/O supply.           |

| IO_VDD_3 (SDIO_IO_VDD) | Power  | B1                  | Input     | I/O Supply for SDIO I/Os. Refer to the<br>GPIOs section for details on which GPIOs<br>have this as the I/O supply. |

| ULP_IO_VDD             | Power  | B33                 | Input     | I/O Supply for ULP GPIOs.                                                                                          |

| PA2G_AVDD              | Power  | B8                  | Input     | Power supply for the 2.4 GHz RF Power Amplifier.                                                                   |

| RF_AVDD                | Power  | A8, A14, B11        | Input     | Power supply for the 2.4 GHz RF and AFE.<br>Connect to VOUTBCKDC as per the Refer-<br>ence Schematics.             |

| AUX_AVDD               | Power  | B34                 | Output    | Output supply for the Analog peripherals.                                                                          |

| UULP_VOUTSCDC          | Power  | B23                 | Output    | UULP Switched Cap DCDC Output.                                                                                     |

| UULP_VOUTSCDC_RETN     | Power  | A28                 | Output    | UULP Retention Supply Output.                                                                                      |

| C_VDD                  | Power  | B2, A18, B38        | Input     | Power supply for the digital core. Connect<br>to the VOUTLDOSOC as per the Refer-<br>ence Schematics.              |

| GND                    | Ground | GND Paddle          | GND       | Common ground pins.                                                                                                |

#### Table 6.2. Chip Packages - Power and Ground Pins

#### 6.2.3 Peripheral Interfaces

| Pin Name        | QFN Pin Num-<br>ber | QFN I/O Supply<br>Domain | Direction | Initial State<br>(Power up, Ac-<br>tive Reset) | Description <sup>1,2,3,4</sup> |                                                                   |             |                                                                     |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |      |         |       |

|-----------------|---------------------|--------------------------|-----------|------------------------------------------------|--------------------------------|-------------------------------------------------------------------|-------------|---------------------------------------------------------------------|-------|--|--|--|--|--|--|--|--|--|--|--|--|--|--|--|------|---------|-------|

| GPIO_6          | B20                 | IO_VDD_1                 | Inout     | HighZ                                          |                                | Default:HighZ                                                     |             |                                                                     |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |      |         |       |

|                 |                     |                          |           |                                                |                                | Sleep: High                                                       | Z           |                                                                     |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |      |         |       |

| GPIO_7          | B19                 | IO_VDD_1                 | Inout     | HighZ                                          |                                | Default:High                                                      | Z           |                                                                     |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |      |         |       |

|                 |                     |                          |           |                                                |                                | Sleep: High                                                       | Z           |                                                                     |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |      |         |       |

|                 |                     |                          |           |                                                |                                | an be configu<br>be any of the                                    |             |                                                                     |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |      |         |       |

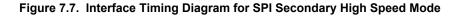

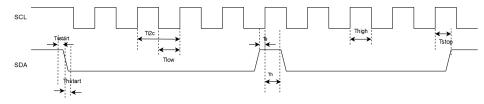

|                 |                     |                          |           |                                                | signal is p                    | ANT: "PTA G<br>art of 3-wire<br>fraffic Arbitra<br>face.          | coexistence |                                                                     |       |  |  |  |  |  |  |  |  |  |  |  |  |  |  |  |      |         |       |