# EFM8 Laser Bee EFM8LB1 Errata

This document contains information on the EFM8LB1 errata. The latest available revision of this device is revision C. Note that revision C devices omit the crystal oscillator. Applications requiring a crystal should specify a revision B part number.

Errata that have been resolved remain documented and can be referenced for previous revisions of this device.

The device data sheet explains how to identify the chip revision, either from the package marking or electronically.

Errata effective date: November, 2022.

# 1. Errata Summary

The table below lists all known errata for the EFM8LB1 and all unresolved errata of the EFM8LB1.

Table 1.1. Errata Overview

| Designator    | Title/Problem                                                               | Workaround | Exists on Revision: |   |   |

|---------------|-----------------------------------------------------------------------------|------------|---------------------|---|---|

|               |                                                                             | Exists     | Α                   | В | С |

| CLU_E101      | CLU Wake-Up Sources are Level Triggered                                     | No         | Х                   | _ | _ |

| DAC_E101      | DAC1 and DAC3 outputs are not updated                                       | Yes        | Х                   | Х | Х |

| I2CSLAVE_E101 | I2CSLAVE0 Cannot Distinguish Between Multiple Addresses                     | No         | Х                   | _ | _ |

| PKG_E101      | Top Marking Right Justified                                                 | No         | Χ                   | _ | _ |

| PKG_E102      | Devices Marked as G Grade                                                   | No         | Х                   | _ | _ |

| POR_E102      | P0.3 Drives Low During Startup                                              | No         | _                   | Х | _ |

| RST_E101      | VREF/P0.0 Not Retained through Power-On Reset                               | No         | Х                   | _ | _ |

| TEMP_E102     | Inaccurate Temperature Sensor Calibration                                   | Yes        | _                   | _ | Х |

| TEST_E101     | Devices Tested to 85 °C                                                     | No         | Х                   | _ | _ |

| TIMER_E101    | Timer 3/4 Chaining Mode in Suspend                                          | Yes        | Х                   | _ | _ |

| TIMER_E102    | High Byte Overflow Flag and Low Byte Overflow Flag are not cleared          | Yes        | Х                   | Х | Х |

| UART1_E101    | Some Data Patterns Cause Inadvertent LIN Break Detection                    | Yes        | Х                   | Х | Х |

| WDT_E101      | Restrictions on Watchdog Timer Refresh Interval                             | Yes        | Х                   | Х | Х |

| WDT_E102      | Restrictions on changing Watchdog Timer Interval                            | Yes        | Χ                   | Х | Х |

| XOSC_E101     | Crystal Mode in External Oscillator Not Available                           | No         | Х                   | _ | Х |

| XOSC_E102     | External Oscillator XFCN = 111 Setting Unavailable when XOSCMD = CMOS_DIV_2 | Yes        | _                   | Х | _ |

# 2. Current Errata Descriptions

# 2.1 DAC\_E101 - DAC1 and DAC3 outputs are not updated

# Description of Errata

When DAC1/DAC3 is configured to use non-alternating mode (D1AMEN = NORMAL, D3AMEN = NORMAL in DACGCF0) and DAC1/DAC3 is configured to use another channel as its input (D1SRC = DAC0 or DAC0\_INVERT, D3SRC = DAC2 or DAC2\_INVERT in DACGCF0), then the DAC1/DAC3 outputs are not updated.

### Affected Conditions / Impacts

Systems using DAC1/DAC3 in normal mode (non-alternating) and that use other channels as the source inputs (DAC0/DAC2) for DAC1/DAC3 will not see changes to the DAC1/DAC3 outputs, regardless of what is written to DAC0L/H and DAC2L/H.

### Workaround

For the DAC1 and DAC3 outputs to be updated, D1UDIS/D3UDIS in DACGCF1 must be toggled or DAC1H/DAC3H needs to be written.

# Resolution

There is currently no resolution for this issue.

# 2.2 TEMP\_E102 - Inaccurate Temperature Sensor Calibration

### Description of Errata

The temperature sensor production calibration value stored in device flash at addresses 0xFFD5:0xFFD4 may be incorrect on QFN32 packaged devices with date codes 2230 through 2242.

### Affected Conditions / Impacts

Affected devices may have incorrect calibration values, which can cause the temperature sensor accuracy to fall outside of the data sheet specification.

### Workaround

Firmware can compensate for inaccuracy by adjusting the production calibrated zero offset value with the following formula using unsigned 16-bit data stored in the notated flash addresses:

```

#define TEMP_COMP0_ADDRESS_LOW 0xFFD0

#define TEMP_COMPO_ADDRESS_HIGH 0xFFD1

#define TEMP_COMP1_ADDRESS_LOW 0xFFD2

#define TEMP_COMP1_ADDRESS_HIGH 0xFFD3

#define TEMP_CAL_ADDRESS_LOW 0xFFD4

#define TEMP_CAL_ADDRESS_HIGH 0xFFD5

// Calibration and compensation values for the temperature sensor at 0 degrees C, stored in CODE space

SI_LOCATED_VARIABLE_NO_INIT(TEMPSENSOR_OC_LOW, uint8_t const, SI_SEG_CODE, TEMP_CAL_ADDRESS_LOW);

SI_LOCATED_VARIABLE_NO_INIT(TEMPSENSOR_OC_HIGH, uint8_t const, SI_SEG_CODE, TEMP_CAL_ADDRESS_HIGH);

SI_LOCATED_VARIABLE_NO_INIT(TEMPSENSOR_COMPO_LOW, uint8_t const, SI_SEG_CODE, TEMP_COMPO_ADDRESS_LOW);

SI_LOCATED_VARIABLE_NO_INIT(TEMPSENSOR_COMP0_HIGH, uint8_t const, SI_SEG_CODE, TEMP_COMP0_ADDRESS_HIGH);

SI_LOCATED_VARIABLE_NO_INIT(TEMPSENSOR_COMP1_LOW, uint8_t const, SI_SEG_CODE, TEMP_COMP1_ADDRESS_LOW);

SI_LOCATED_VARIABLE_NO_INIT(TEMPSENSOR_COMP1_HIGH, uint8_t const, SI_SEG_CODE, TEMP_COMP1_ADDRESS_HIGH);

uint16_t calcNewOffset (void) {

int16_t newOffset;

uint16_t oldOffset, comp0, comp1;

comp0 = (TEMPSENSOR_COMP0_HIGH << 8) | TEMPSENSOR_COMP0_LOW;</pre>

comp1 = (TEMPSENSOR_COMP1_HIGH << 8) | TEMPSENSOR_COMP1_LOW;</pre>

oldOffset = (TEMPSENSOR_OC_HIGH << 8) | TEMPSENSOR_OC_LOW;</pre>

newOffset = comp0 - comp1;

newOffset *= 28;

newOffset /= 100;

newOffset += oldOffset;

return (uint16_t) newOffset;

```

Calculate the die temperature in °C with firmware by measuring the temperature sensor output using the ADC, subtract the calculated new offset value, then divide the result by 28:

```

dieTemperature = (ADCoutput - calcNewOffset()) / 28;

```

Refer to AN929: Accurate Temperature Sensing with the EFM8 Laser Bee MCU Family for additional information regarding temperature calculation.

### Resolution

This issue only affects revision C QFN32 devices with date codes from 2230 through 2242. All other devices have stored temperature sensor calibration values that meet data sheet accuracy specifications.

# 2.3 TIMER\_E102 - High Byte Overflow Flag and Low Byte Overflow Flag are not cleared

# Description of Errata

When TIMERn is enabled and firmware writes TMRnCN0 to 0, the TMRnCN0\_TFxH and TMRnCN0\_TFxL flags are not always cleared.

### Affected Conditions / Impacts

When TIMERn is enabled, a high byte/low byte overflow event can happen in the same cycle as the firmware is writing a 0 to TMRnCN0. It is possible that TMRnCN0\_TFxH and TMRnCN0\_TFxL are still set by hardware even after firmware writes to clear them.

### Workaround

TIMERn must be completely stopped before attempting to clear TMRnCN0. This guarantees that the TMRnCN0\_TFxH and TMRnCN0\_TFxL flags are cleared as expected.

### Resolution

There is currently no resolution for this issue.

### 2.4 UART1\_E101 - Some Data Patterns Cause Inadvertent LIN Break Detection

# Description of Errata

If UART1 is used in LIN mode (LINMDE = 1 in UART1LIN), certain data patterns consisting of a byte whose MSBs resemble a start bit (e.g. 0b101xxxxx when accounting for LSB first transmission) followed by 0x0 are improperly detected as a LIN break sequence.

### Affected Conditions / Impacts

Because LIN frames can have a variable length of 2, 4, or 8 bytes, the detection of a break when it is not actually sent on the LIN bus could result in application software expecting the arrival of a new frame. Furthermore, if autobaud is enabled (AUTOBDE = 1 in UART1LIN), the detection of a break at the wrong time would result in the interpretation of the next character as the sync character, which is not likely to be the required 0x55. By attempting to sync on the wrong character, the baud rate determined would be wrong, and communication with the master would be lost due to baud rate mismatch.

### Workaround

There is currently no workaround for this issue.

**Note:** The inadvertent triggering of the autobaud logic due to improper detection of break does not apply when UART1 is not being used in LIN mode. By following the procedure described in the reference manual, whereby it is enabled pending detection of the sync character and then disabled after the sync character is received. UART1 autobaud detection functions as expected.

### Resolution

There is currently no resolution for this issue.

### 2.5 WDT\_E101 - Restrictions on Watchdog Timer Refresh Interval

# Description of Errata

If the Watchdog Timer (WDT) is enabled, firmware will periodically write an 0xA5 value to the WDTCN register to refresh the timer and prevent the watchdog reset from occurring. However, if firmware writes to WDTCN more than once during the same LFOSC0 clock period, the refresh signal may be canceled, resulting in an unintended watchdog reset when the timer expires.

# Affected Conditions / Impacts

If firmware refreshes the watchdog more than once in the same LFOSC0 clock period, an unexpected watchdog reset can occur.

### Workaround

Systems using the Watchdog Timer (WDT) should ensure that the WDT is refreshed no more than once per LFOSC0 clock period.

Firmware can do this by using timers to count LFOSC0 clock periods. There are three methods to accomplish this:

1. If Timer 3 is not already in use, set it up to capture on the LFOSC0 clock. In this mode, the value of the Timer 3 reload registers does not matter. Instead, the WDT refresh function should check for the 16-bit timer flag (TF3H) to be set in the reset watchdog function, which indicates that a capture event occurred. If the device has another timer that can capture on the LFOSC0 clock, then that timer may be used instead of Timer 3.

```

void refresh_wdt()

{

// Only refresh if TF3H is set

if (TMR3CN0 & (0x80))

{

WDTCN = 0xA5;

TMR3CN0 &= ~(0x80);

}

}

```

2. If any timer is already in use, is clocked from the LFOSC0, and the low overflow flag is not already in use, firmware can check the low byte overflow flag (TFnL) to ensure at least one clock period has passed. For example, using Timer 3:

```

void init_wdt()

{

// whatever code needed to initialized watchdog

// intentionally set the TF3L flag (assuming SFRPAGE is correct)

TMR3CN0 |= 0x40;

}

void refresh_wdt()

{

static uint8_t last_tmr3l = 0;

if ( (TMR3CN0 & 0x40) || (last_tmr3l != TMR3L) )

{

WDTCN = 0xA5;

TMR3CN0 &= ~0x40;

last_tmr3l = TMR3L;

}

}

```

3. If the application already has an accurate and reliable time base, use that timer to establish a minimum WDT refresh interval that is longer than one LFOSC0 clock period in duration, similar to method (2) above as appropriate.

See the Knowledge Base article on this errata for more information, including examples of these firmware workarounds: https://www.silabs.com/community/mcu/8-bit/knowledge-base.entry.html/2016/11/28/wdt\_e101\_-\_restricti-Vqe5.

**Note:** The LFOSC0 does not halt while debugging. This can cause the timer overflow flag to be set more quickly than expected when debugging the watchdog refresh function.

### Resolution

There is currently no resolution for this issue.

# 2.6 WDT\_E102 - Restrictions on changing Watchdog Timer Interval

### Description of Errata

A watchdog reset can occur when the Watchdog Timer (WDT) is disabled.

### Affected Conditions / Impacts

If the WDT timeout interval is changed from a higher interval to a lower interval, regardless if the WDT is enabled or disabled, a watch-dog reset can occur

### Workaround

This can be resolved by refreshing and disabling the WDT before changing the WDT timeout interval from a higher interval to lower interval. Following is the sequence of code that needs to be followed when changing the WDT interval.

**Note:** User must insert the code to wait. It is not explicity added in the above sequence as it depends on the divided LFOSC0 clock and the SYSCLK clock selected by the user.

### Resolution

There is currently no resolution for this issue.

# 2.7 XOSC\_E101 - Crystal Mode in External Oscillator Not Available

# Description of Errata

The data sheet mentions support for an external crystal oscillator. However, the crystal mode in the external oscillator option is not available on revision A devices.

# Affected Conditions / Impacts

Systems intending to use the crystal mode in the external oscillator will not be able to do so. However, other external oscillator modes (CMOS or RC) are available.

# Workaround

Systems needing to use an external oscillator should use the available external oscillator modes (CMOS or RC) with revision A devices.

# Resolution

This issue is resolved in revision B devices only. Revision C devices do not include the crystal oscillator.

# 3. Resolved Errata Descriptions

This section contains previous errata for EFM8LB1 devices. Note that revision C devices omit the crystal oscillator. Applications requiring a crystal should specify a revision B part number.

For errata on the latest revision, refer to the beginning of this document. The device data sheet explains how to identify chip revision, either from package marking or electronically.

# 3.1 CLU\_E101 - CLU Wake-Up Sources are Level Triggered

# Description of Errata

The device reference manual describes the CLU interrupt-enabled Suspend or Snooze wake-up sources as edge triggered. However, these wake sources are level triggered on revision A devices.

# Affected Conditions / Impacts

Systems using the CLU to wake from Suspend or Snooze must disable the CLU wake-up sources following a wake event if they remain high and firmware should not execute the ISR more than once.

### Workaround

Since the CLU wake-up sources are level triggered, the CLU output causing the wake-up event will continuously trigger interrupts if the output remains active. Systems not desiring this behavior should disable the CLU wake-up sources after a wake event to ensure the ISR is executed only once. The wake-up sources can be re-enabled before re-entering Suspend or Snooze.

### Resolution

This issue is resolved in revision B devices.

# 3.2 I2CSLAVE\_E101 - I2CSLAVE0 Cannot Distinguish Between Multiple Addresses

# Description of Errata

The device reference manual mentions that the I2CSLAVE0 module can respond to multiple slave addresses and distinguish between these addresses using the receive FIFO when the ADDRCHK bit in I2C0CN0 is set to 1. The ADDRCHK bit is not available on revision A devices, and these devices cannot distinguish between multiple possible slave addresses that could have been used in the initiated transaction.

# Affected Conditions / Impacts

Systems intending to use distinguish between multiple addresses cannot do so with revision A devices.

# Workaround

There is currently no workaround for this issue.

### Resolution

This issue is resolved in revision B devices.

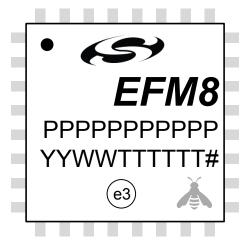

# 3.3 PKG\_E101 - Top Marking Right Justified

# Description of Errata

The Package Marking diagrams indicate that the package marking is left justified. However, QFP32 devices with the 1531 date code have package markings that are right justified.

Incorrect QFP32 Package Marking

### Affected Conditions / Impacts

Assembly houses expecting left-justified package marking may see some parts with right-justified package marking.

### Workaround

There is currently no workaround for this issue.

### Resolution

This issue only affects revision A QFP32 devices with a date code of 1531. All other devices should match the Package Marking diagrams in the device data sheet.

# 3.4 PKG\_E102 - Devices Marked as G Grade

# Description of Errata

The temperature grade of the EFM8LB1 devices is E, indicating the devices are tested to 105 °C. However, revision A devices with a date code of 1540 or 1602 are marked with G. This is in error, and these devices are tested to 105 °C.

# Affected Conditions / Impacts

Assembly houses should expect that some devices may have a part number marking including a G, rather than an E.

# Workaround

There is currently no workaround for this issue.

### Resolution

This issue only affects revision A devices with a date code of 1540 or 1602. All other devices should match the expected part number listed in the device data sheet.

# 3.5 POR\_E102 - P0.3 Drives Low During Startup

### Description of Errata

On some devices, during power-on reset (POR) with a slow power-on ramp, P0.3, the External Oscillator Output (EXTOSC) pin, may drive low until VDD rises above V<sub>VDDM</sub> max and the device begins code execution. The normal behavior for P0.3 during POR is that the pin is pulled logic high via weak pull-up.

### Affected Conditions / Impacts

External devices and peripherals connected to P0.3 requiring a logic high via weak pull-up during POR may fail to operate properly.

### Workaround

There is currently no workaround for this issue.

### Resolution

This issue is resolved in revision A and revision C devices.

### 3.6 RST\_E101 - VREF/P0.0 Not Retained through Power-On Reset

# Description of Errata

The VREF/P0.0 pin output is expected to be retained on any non-POR reset if the RSTMD bit is set to the PERSIST state in the DACnCF0 register. However, the VREF/P0.0 output on revision A devices is not retained if the PINRETAIN bit in PCON1 is set (in addition to the RSTMD bit in the DAC) and drops from its level to 0 V on any non-POR reset. All DAC SFRs and REF0CN are properly retained.

After a non-POR reset, if firmware clears the PINRETAIN bit to 0, the VREF/P0.0 pin will return back to its original level. This is true for both the 1.2 V and 2.4 V options.

# Affected Conditions / Impacts

Systems intending to use the pin retain feature for VREF/P0.0 will not be able to do so without using the proposed workaround.

### Workaround

Systems intending to use the pin retain feature for VREF/P0.0 must clear the PINRSTMD bit in the PCON1 register after a reset.

### Resolution

This issue is resolved in revision B devices.

# 3.7 TEST\_E101 - Devices Tested to 85 °C

# Description of Errata

The datasheet specifies that revision A devices are production tested to 105 °C. However, some devices with date codes of 1530, 1531, or 1532 were production tested only to 85 °C. The date code consist of the YYWW pair shown in the Package Marking diagrams in the device data sheet.

# Affected Conditions / Impacts

Applications requiring operation above 85 °C should use devices that do not have a 1530, 1531, or 1532 date code.

# Workaround

There is currently no workaround for this issue.

# Resolution

This issue only affects revision A devices with a date codes of 1530, 1531, or 1532. All other devices are production tested appropriately for the 105 °C limit.

# 3.8 TIMER\_E101 - Timer 3/4 Chaining Mode in Suspend

# Description of Errata

The Timer 3/4 32-bit counter on revision B devices will not switch to the low frequency oscillator (LFOSC0) after entering Suspend mode if the system clock divider is set to a value of divide-by-4 or greater.

### Affected Conditions / Impacts

Systems using the Timer 3/4 32-bit counter in chained mode while in Suspend should use the recommended system clock divider settings to ensure proper operation.

### Workaround

When using the Timer 3/4 32-bit counter in Suspend mode, set the system clock divider to the divide-by-1 or divide-by-2 settings before entering Suspend mode.

### Resolution

This issue is resolved in revision B devices.

# 3.9 XOSC\_E102 - External Oscillator XFCN = 111 Setting Unavailable when XOSCMD = CMOS\_DIV\_2

# Description of Errata

When the external oscillator is configured for external CMOS clock mode with divide by 2 (XOSCMD = CMOS\_DIV\_2 in XOSC0CN), it is not possible to use the 111 frequency control setting (XFCN = 111 in XOSC0CN).

# Affected Conditions / Impacts

Systems that need to use the XFCN = 111 setting cannot do so in the CMOS\_DIV\_2 (external clock divided-by-2) configuration.

### Workaround

Use other clock control options to achieve the desired divide-by-2 when using an external oscillator, e.g. set CLKDIV = SYSCLK\_DIV\_2 in CLKSEL.

### Resolution

This issue is resolved in revision A and revision C devices.

# 4. Revision History

### Revision 1.2

November, 2022

- Corrected affected revisions for POR\_E102, UART1\_E101, and XOSC\_E101.

- Added DAC\_E101, TEMP\_E102, TIMER\_E102 and XOSC\_E102.

- · Migrated to new errata document format.

### **Revision 1.1**

May, 2019

- Added UART1 E101.

- · Updated XOSC\_E101 to reflect that only revision B is fixed. The crystal oscillator is not present on revision C.

# **Revision 1.0**

December, 2018

- · Updated latest revision to C.

- Table 1.1 Errata Overview on page 2 now reflects the presence of POR\_E102 on revision A devices.

- Moved POR\_E102 from the errata to the errata history and changed XTAL2 pin reference to EXTOSC in order to conform with revision C documentation.

### Revision 0.9

November, 2018

Added WDT E102.

# Revision 0.8

August, 2018

- Merged errata history and errata into one document.

- · Updated the second workaround in WDT\_E101.

- Updated Knowledge Base article link in WDT\_E101.

- · Added POR E102.

# Revision 0.7

September, 2016

Added WDT E101.

### Revision 0.6

February, 2016

- · Updated latest revision to B.

- Moved CLU\_E101, I2CSLAVE\_E101, PKG\_E101, RST\_E101, TIMER\_E101, and XOSC\_E101 from the errata to the errata history.

### Revision 0.5

January, 2016

Updated the affected revision date codes for PKG\_E102.

# Revision 0.4

November, 2015

• Added PKG\_E102 and TEST\_E101.

# Revision 0.3

October, 2015

- Updated RST\_E101, TIMER\_E101, and XOSC\_E101 with errata designators.

- Added CLU\_E101, I2CSLAVE\_E101, and PKG\_E101.

# Revision 0.1

June, 2015

· Initial release.

**IoT Portfolio** www.silabs.com/IoT

**SW/HW** www.silabs.com/simplicity

**Quality** www.silabs.com/quality

**Support & Community** www.silabs.com/community

### Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such unauthorized applications. Note: This content may contain offensive terminology that is now obsolete. Silicon Labs is replacing these term

### morniacion, visit www.snabs.com/about-us/melasive-ic

Silicon Laboratories Inc.®, Silicon Laboratories®, Silicon Labs®, SiLabs® and the Silicon Labs logo®, Bluegiga®, Bluegiga Logo®, EFM®, EFM32®, EFR, Ember®, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Redpine Signals®, WiSeConnect, n-Link, ThreadArch®, EZLink®, EZRadio®, EZRadio®, Cecko®, Gecko®, Gecko OS, Gecko OS Studio, Precision32®, Simplicity Studio®, Telegesis, the Telegesis Logo®, USBXpress®, Zentri, the Zentri logo and Zentri DMS, Z-Wave®, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.

**Trademark Information**

Silicon Laboratories Inc. 400 West Cesar Chavez Austin, TX 78701 USA