# EFR32xG12 Wireless Gecko Reference Manual

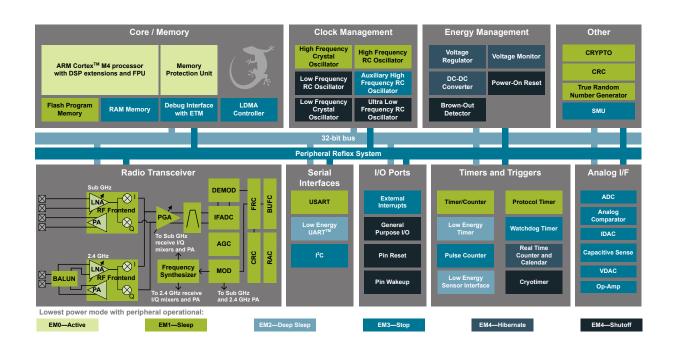

The Wireless Gecko portfolio of SoCs (EFR32) include the EFR32MG12, EFR32BG12, and EFR32FG12 families. With support for Zigbee<sup>®</sup>, Thread, Bluetooth Low Energy (BLE) and proprietary protocols, the Wireless Gecko portfolio is ideal for enabling energy-friendly wireless networking for IoT devices.

The single-die solution provides industry-leading energy efficiency, ultra-fast wakeup times, a scalable high-power amplifier, an integrated balun and no-compromise MCU features.

#### **KEY FEATURES**

- 32-bit ARM® Cortex-M4 core with 40 MHz maximum operating frequency

- Scalable Memory and Radio configuration options available in several footprint compatible QFN packages

- 12-channel Peripheral Reflex System enabling autonomous interaction of MCU peripherals

- Autonomous Hardware Crypto Accelerator and Random Number Generator

- Integrated balun for 2.4 GHz and integrated PA with up to 19.5 dBm transmit power for 2.4 GHz and 20 dBm transmit power for Sub-GHz radios

- · Integrated dc-dc with RF noise mitigation

# **Table of Contents**

| 1.1 Introduction       28         1.2 Conventions       28         1.3 Related Documentation       29         2. System Overview       30         2.1 Introduction       30         2.2 Block Diagrams       31         2.3 MCU Features Overview       32         2.4 Oscillators and Clocks       34         2.5 RF Frequency Synthesizer       34         2.6 Modulation Modes       34         2.7 Transmit Mode       35         2.8 Receive Mode       35         2.9 Data Buffering       35         2.10 Unbuffered Data Transfer       35         2.11 Frame Format Support       36         2.12 Hardware CRC Support       36         2.13 Convolutional Encoding / Decoding       36         2.14 Binary Block Encoding / Decoding       36         2.15 Data Encryption and Authentication       37         2.16 Timers       38         2.17 RF Test Modes       38         3. System Processor       39         3.1 Introduction       39         3.2 Features       40         3.3 Functional Description       40         3.3.1 Interrupt Operation       41         3.3.2 Interrupt Request Lines (IRQ)       42                                                                                                                                           | 1. | 1. About This Document                  |   | <br>  |   |   |   |   | 28   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|-----------------------------------------|---|-------|---|---|---|---|------|

| 1.3 Related Documentation       29         2. System Overview       30         2.1 Introduction       30         2.2 Block Diagrams       31         2.3 MCU Features Overview       32         2.4 Oscillators and Clocks       34         2.5 RF Frequency Synthesizer       34         2.6 Modulation Modes       34         2.7 Transmit Mode       35         2.8 Receive Mode       35         2.9 Data Buffering       35         2.10 Unbuffered Data Transfer       35         2.11 Frame Format Support       36         2.12 Hardware CRC Support       36         2.13 Convolutional Encoding / Decoding       36         2.14 Binary Block Encoding / Decoding       36         2.15 Data Encryption and Authentication       37         2.16 Timers       38         2.17 RF Test Modes       38         3. System Processor       39         3.1 Introduction       39         3.2 Features       40         3.3.1 Interrupt Operation       40         3.3.2 Interrupt Request Lines (IRQ)       42         4. Memory and Bus System       44         4.1 Introduction       45         4.2 Functional Description <td< td=""><td></td><td>1.1 Introduction</td><td></td><td></td><td></td><td></td><td></td><td></td><td>.28</td></td<>                     |    | 1.1 Introduction                        |   |       |   |   |   |   | .28  |

| 2. System Overview       30         2.1 Introduction       30         2.2 Block Diagrams       31         2.3 MCU Features Overview       32         2.4 Oscillators and Clocks       34         2.5 RF Frequency Synthesizer       34         2.6 Modulation Modes       34         2.7 Transmit Mode       35         2.8 Receive Mode       35         2.9 Data Buffering       35         2.10 Unbuffered Data Transfer       35         2.11 Frame Format Support       36         2.12 Hardware CRC Support       36         2.13 Convolutional Encoding / Decoding       36         2.14 Binary Block Encoding / Decoding       36         2.15 Data Encryption and Authentication       37         2.16 Timers       38         3.1 Introduction       37         3.2 Freatures       40         3.3 Functional Description       40         3.3.1 Interrupt Operation       41         3.3.2 Interrupt Request Lines (IRQ)       42         4. Memory and Bus System       44         4.1 Introduction       45         4.2.1 Peripheral Non-Word Access Behavior       48         4.2.2 Bit-banding       48         4.2.3 Peripheral B                                                                                                                            |    | 1.2 Conventions                         |   | <br>- | - |   |   |   | .28  |

| 2.1 Introduction       .30         2.2 Block Diagrams       .31         2.3 MCU Features Overview       .32         2.4 Oscillators and Clocks       .34         2.5 RF Frequency Synthesizer       .34         2.6 Modulation Modes       .34         2.7 Transmit Mode       .35         2.8 Receive Mode       .35         2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .38         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48                                                                                                                           |    | 1.3 Related Documentation               |   |       |   |   |   |   | .29  |

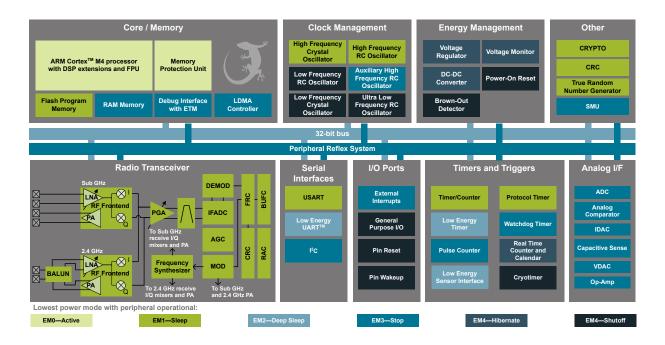

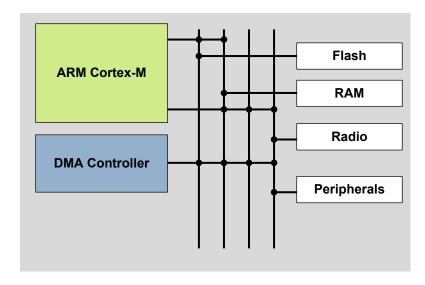

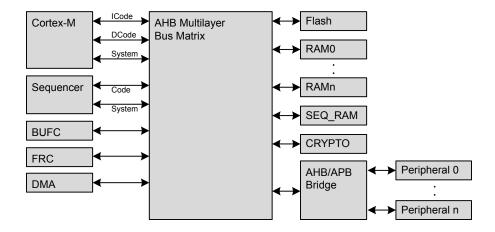

| 2.2 Block Diagrams.       .31         2.3 MCU Features Overview       .32         2.4 Oscillators and Clocks       .34         2.5 RF Frequency Synthesizer       .34         2.6 Modulation Modes.       .34         2.7 Transmit Mode       .35         2.8 Receive Mode       .35         2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .49 <t< td=""><td>2.</td><td>2. System Overview</td><td></td><td></td><td></td><td></td><td></td><td></td><td>30</td></t<> | 2. | 2. System Overview                      |   |       |   |   |   |   | 30   |

| 2.3 MCU Features Overview       32         2.4 Oscillators and Clocks       34         2.5 RF Frequency Synthesizer       34         2.6 Modulation Modes       34         2.7 Transmit Mode       35         2.8 Receive Mode       35         2.9 Data Buffering       35         2.10 Unbuffered Data Transfer       35         2.11 Frame Format Support       36         2.12 Hardware CRC Support       36         2.13 Convolutional Encoding / Decoding       36         2.14 Binary Block Encoding / Decoding       36         2.15 Data Encryption and Authentication       37         2.16 Timers       38         2.17 RF Test Modes       38         3. System Processor       39         3.1 Introduction       39         3.2 Features       40         3.3.2 Interrupt Operation       41         3.3.2 Interrupt Request Lines (IRQ)       42         4. Memory and Bus System       44         4.1 Introduction       45         4.2 Functional Description       46         4.2.1 Peripheral Non-Word Access Behavior       48         4.2.2 Bit-banding       48         4.2.4 Peripherals       50                                                                                                                                                      |    | 2.1 Introduction                        |   |       |   |   |   |   | .30  |

| 2.4 Oscillators and Clocks       .34         2.5 RF Frequency Synthesizer       .34         2.6 Modulation Modes       .34         2.7 Transmit Mode       .35         2.8 Receive Mode       .35         2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                   |    | 2.2 Block Diagrams                      |   |       |   |   |   |   | .31  |

| 2.5 RF Frequency Synthesizer       .34         2.6 Modulation Modes       .34         2.7 Transmit Mode       .35         2.8 Receive Mode       .35         2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.2 Interrupt Request Lines (IRQ)       .42         4 Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                |    | 2.3 MCU Features Overview               |   |       |   |   |   |   | .32  |

| 2.6 Modulation Modes       .34         2.7 Transmit Mode       .35         2.8 Receive Mode       .35         2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3.1 Interrupt Operation       .40         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                               |    | 2.4 Oscillators and Clocks              |   |       |   |   |   |   | .34  |

| 2.7 Transmit Mode       .35         2.8 Receive Mode       .35         2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.2 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                         |    | 2.5 RF Frequency Synthesizer            |   |       |   |   |   |   | .34  |

| 2.8 Receive Mode       .35         2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3.1 Interrupt Operation       .40         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                          |    | 2.6 Modulation Modes                    |   |       |   |   |   |   | .34  |

| 2.9 Data Buffering       .35         2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4 Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                              |    | 2.7 Transmit Mode                       |   |       | - |   |   |   | .35  |

| 2.10 Unbuffered Data Transfer       .35         2.11 Frame Format Support       .36         2.12 Hardware CRC Support       .36         2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4 Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                   |    | 2.8 Receive Mode                        |   |       | - |   |   |   | .35  |

| 2.11 Frame Format Support       36         2.12 Hardware CRC Support       36         2.13 Convolutional Encoding / Decoding       36         2.14 Binary Block Encoding / Decoding       36         2.15 Data Encryption and Authentication       37         2.16 Timers       38         2.17 RF Test Modes       38         3. System Processor       39         3.1 Introduction       39         3.2 Features       40         3.3 Functional Description       40         3.3.1 Interrupt Operation       41         3.2 Interrupt Request Lines (IRQ)       42         4 Memory and Bus System       44         4.1 Introduction       45         4.2 Functional Description       46         4.2.1 Peripheral Non-Word Access Behavior       48         4.2.2 Bit-banding       48         4.2.3 Peripheral Bit Set and Clear       49         4.2.4 Peripherals       50                                                                                                                                                                                                                                                                                                                                                                                            |    | 2.9 Data Buffering                      |   |       | - |   |   |   | .35  |

| 2.12 Hardware CRC Support       36         2.13 Convolutional Encoding / Decoding       36         2.14 Binary Block Encoding / Decoding       36         2.15 Data Encryption and Authentication       37         2.16 Timers       38         2.17 RF Test Modes       38         3. System Processor       39         3.1 Introduction       39         3.2 Features       40         3.3 Functional Description       40         3.3.1 Interrupt Operation       41         3.3.2 Interrupt Request Lines (IRQ)       42         4 Memory and Bus System       44         4.1 Introduction       45         4.2 Functional Description       46         4.2.1 Peripheral Non-Word Access Behavior       48         4.2.2 Bit-banding       48         4.2.3 Peripheral Bit Set and Clear       49         4.2.4 Peripherals       50                                                                                                                                                                                                                                                                                                                                                                                                                                     |    | 2.10 Unbuffered Data Transfer           |   |       | - |   |   |   | .35  |

| 2.13 Convolutional Encoding / Decoding       .36         2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4 Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 2.11 Frame Format Support               |   |       | - |   |   |   | .36  |

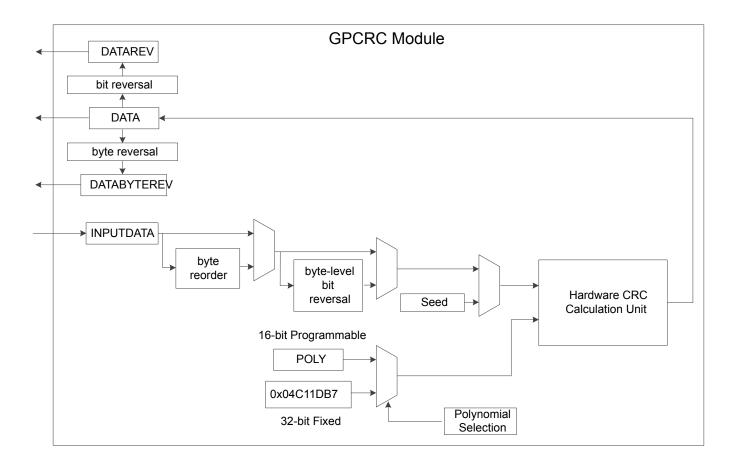

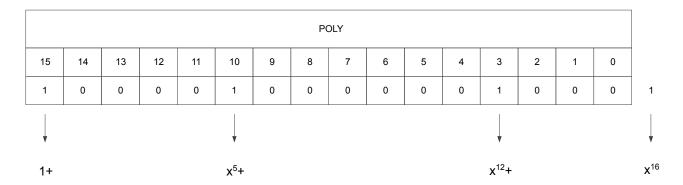

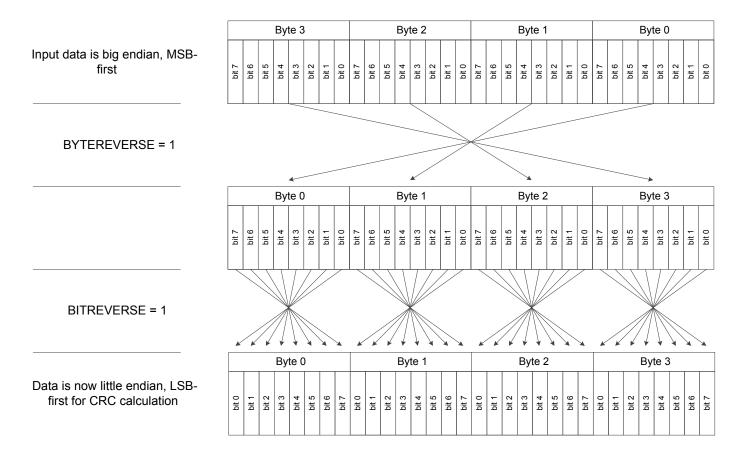

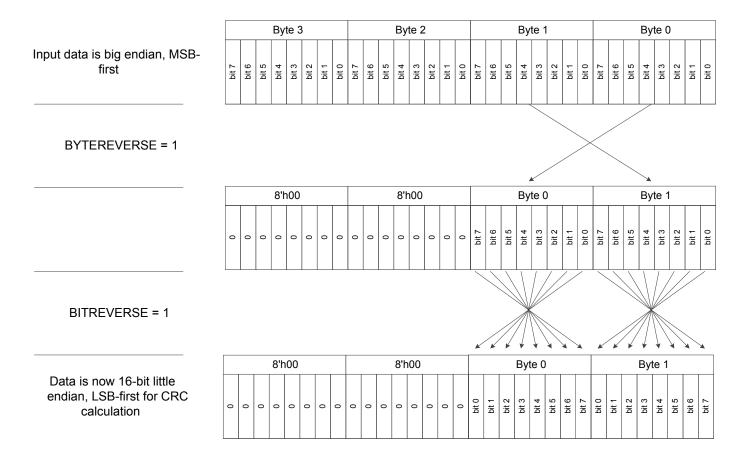

| 2.14 Binary Block Encoding / Decoding       .36         2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 2.12 Hardware CRC Support               |   |       |   |   |   |   | .36  |

| 2.15 Data Encryption and Authentication       .37         2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    | 2.13 Convolutional Encoding / Decoding  |   |       |   |   |   |   | .36  |

| 2.16 Timers       .38         2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    | 2.14 Binary Block Encoding / Decoding   |   |       |   |   |   |   | .36  |

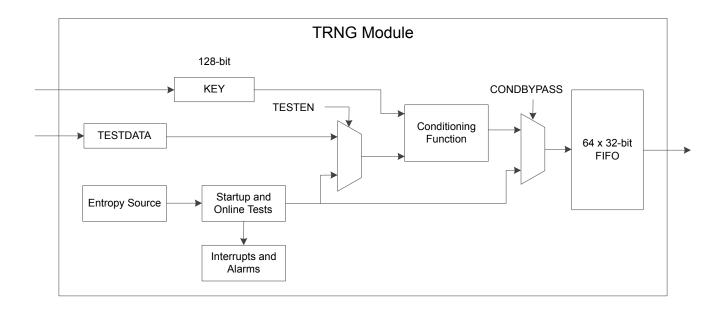

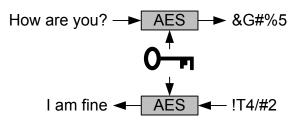

| 2.17 RF Test Modes       .38         3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    | 2.15 Data Encryption and Authentication |   |       |   |   |   |   | .37  |

| 3. System Processor       .39         3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | 2.16 Timers                             |   |       |   |   |   |   | .38  |

| 3.1 Introduction       .39         3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    | 2.17 RF Test Modes                      |   |       |   |   |   |   | .38  |

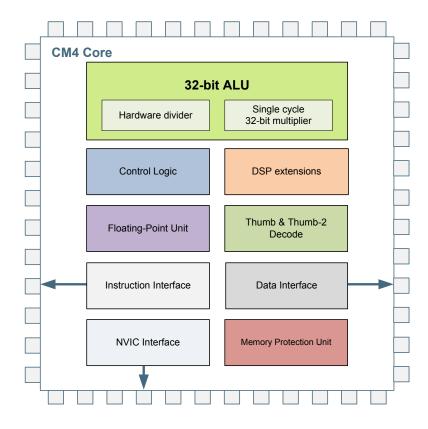

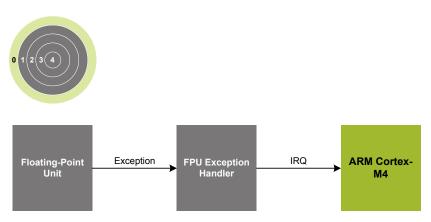

| 3.2 Features       .40         3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3. | 3. System Processor                     |   |       |   |   |   |   | . 39 |

| 3.3 Functional Description       .40         3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | 3.1 Introduction                        |   |       |   |   |   |   | .39  |

| 3.3.1 Interrupt Operation       .41         3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    | 3.2 Features                            |   |       |   |   |   |   | .40  |

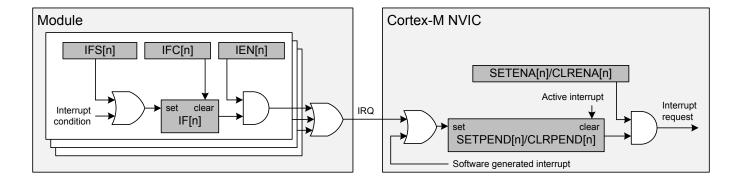

| 3.3.2 Interrupt Request Lines (IRQ)       .42         4. Memory and Bus System       .44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | 3.3 Functional Description              |   |       |   |   |   |   | .40  |

| 4. Memory and Bus System       44         4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |    | · ·                                     |   |       |   |   |   |   |      |

| 4.1 Introduction       .45         4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | 3.3.2 Interrupt Request Lines (IRQ)     |   | <br>• | • | • | • |   | .42  |

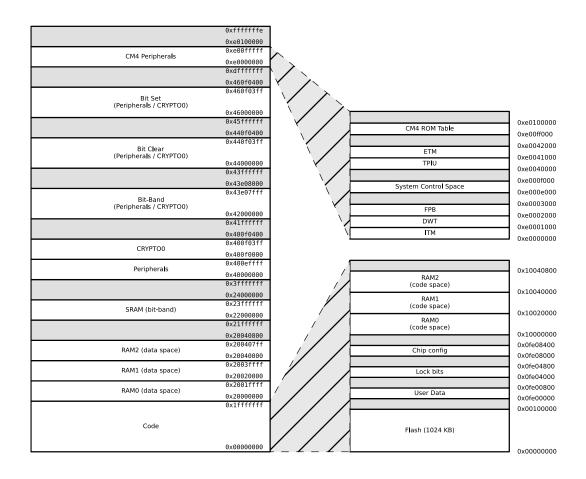

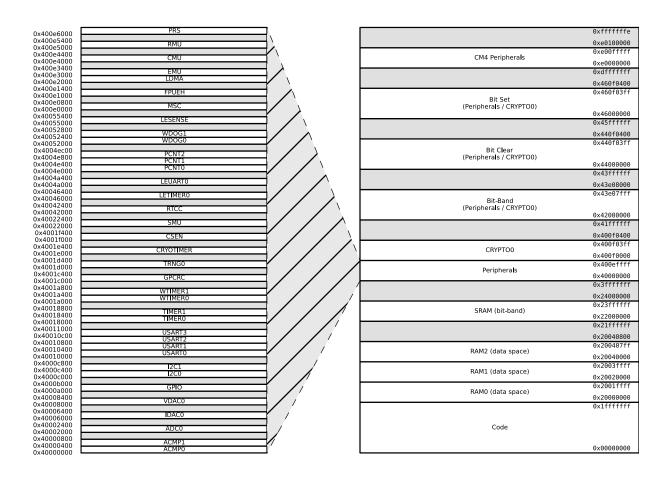

| 4.2 Functional Description       .46         4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 4. | 4. Memory and Bus System                | • |       |   |   | • | • | 44   |

| 4.2.1 Peripheral Non-Word Access Behavior       .48         4.2.2 Bit-banding       .48         4.2.3 Peripheral Bit Set and Clear       .49         4.2.4 Peripherals       .50                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    |                                         |   |       |   |   |   |   |      |

| 4.2.2 Bit-banding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    | ·                                       |   |       |   |   |   |   |      |

| 4.2.3 Peripheral Bit Set and Clear                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |    | •                                       |   |       |   |   |   |   |      |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |    |                                         |   |       |   |   |   |   |      |

| 4.2.5 Bus Matrix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |    | ·                                       |   |       |   |   |   |   |      |

| 4.3 Access to Low Energy Peripherals (Asynchronous Registers)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |                                         |   |       |   |   |   |   |      |

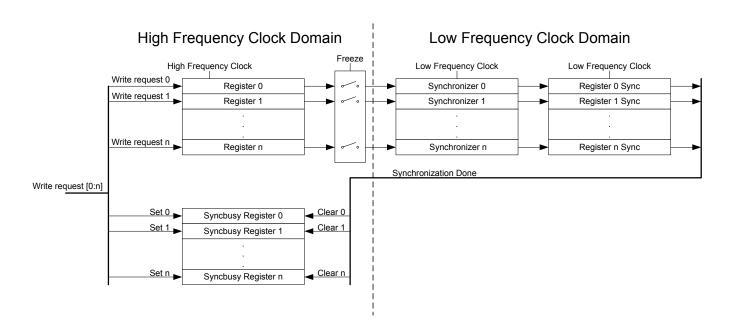

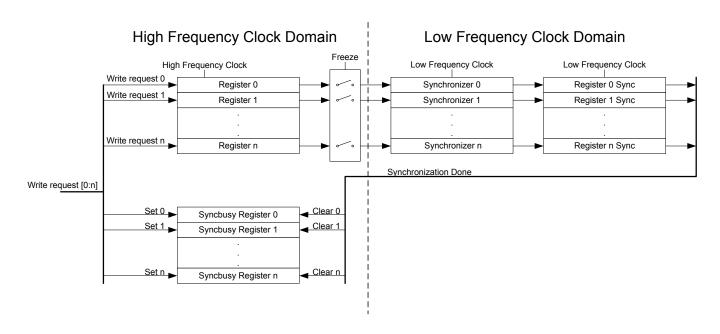

| 4.3.1 Writing                                                                                                 |   |  |  |  | .57 |

|---------------------------------------------------------------------------------------------------------------|---|--|--|--|-----|

| 4.4 Flash                                                                                                     |   |  |  |  |     |

| 4.5 SRAM                                                                                                      |   |  |  |  |     |

| 4.6 DI Page Entry Map                                                                                         |   |  |  |  | .59 |

| 4.7 DI Page Entry Description                                                                                 |   |  |  |  | .61 |

| 4.7.1 CAL - CRC of DI-page and calibration temperature                                                        |   |  |  |  |     |

| 4.7.2 MODULEINFO - Module trace information                                                                   |   |  |  |  |     |

| 4.7.3 MODXOCAL - Module Crystal Oscillator Calibration                                                        |   |  |  |  |     |

| 4.7.4 EXTINFO - External Component description                                                                |   |  |  |  |     |

| 4.7.5 EUI48L - EUI48 OUI and Unique identifier                                                                |   |  |  |  |     |

| 4.7.7 CUSTOMINFO - Custom information                                                                         |   |  |  |  |     |

| 4.7.8 MEMINFO - Flash page size and misc. chip information                                                    |   |  |  |  |     |

| 4.7.9 UNIQUEL - Low 32 bits of device unique number                                                           |   |  |  |  |     |

| 4.7.10 UNIQUEH - High 32 bits of device unique number                                                         |   |  |  |  |     |

| 4.7.11 MSIZE - Flash and SRAM Memory size in kB                                                               |   |  |  |  | .67 |

| 4.7.12 PART - Part description                                                                                |   |  |  |  | .68 |

| 4.7.13 DEVINFOREV - Device information page revision                                                          |   |  |  |  | .70 |

| 4.7.14 EMUTEMP - EMU Temperature Calibration Information                                                      |   |  |  |  |     |

| 4.7.15 ADC0CAL0 - ADC0 calibration register 0                                                                 |   |  |  |  |     |

| 4.7.16 ADC0CAL1 - ADC0 calibration register 1                                                                 |   |  |  |  |     |

| 4.7.17 ADC0CAL2 - ADC0 calibration register 2                                                                 |   |  |  |  |     |

| 4.7.18 ADC0CAL3 - ADC0 calibration register 3                                                                 |   |  |  |  |     |

| 4.7.19 HFRCOCALO - HFRCO Calibration Register (4 MHz)                                                         |   |  |  |  |     |

| 4.7.20 HFRCOCALS - HFRCO Calibration Register (7 MHz)                                                         |   |  |  |  |     |

| 4.7.21 HFRCOCAL6 - HFRCO Calibration Register (13 MHz) 4.7.22 HFRCOCAL7 - HFRCO Calibration Register (16 MHz) |   |  |  |  |     |

| 4.7.23 HFRCOCAL7 - HFRCO Calibration Register (19 MHz)                                                        |   |  |  |  |     |

| 4.7.24 HFRCOCAL10 - HFRCO Calibration Register (26 MHz)                                                       |   |  |  |  |     |

| 4.7.25 HFRCOCAL11 - HFRCO Calibration Register (32 MHz)                                                       |   |  |  |  |     |

| 4.7.26 HFRCOCAL12 - HFRCO Calibration Register (38 MHz)                                                       |   |  |  |  |     |

| 4.7.27 AUXHFRCOCAL0 - AUXHFRCO Calibration Register (4 MHz)                                                   |   |  |  |  |     |

| 4.7.28 AUXHFRCOCAL3 - AUXHFRCO Calibration Register (7 MHz)                                                   |   |  |  |  | .83 |

| 4.7.29 AUXHFRCOCAL6 - AUXHFRCO Calibration Register (13 MHz)                                                  |   |  |  |  | .84 |

| 4.7.30 AUXHFRCOCAL7 - AUXHFRCO Calibration Register (16 MHz)                                                  |   |  |  |  | .85 |

| 4.7.31 AUXHFRCOCAL8 - AUXHFRCO Calibration Register (19 MHz)                                                  |   |  |  |  |     |

| 4.7.32 AUXHFRCOCAL10 - AUXHFRCO Calibration Register (26 MHz)                                                 | ) |  |  |  | .87 |

| 4.7.33 AUXHFRCOCAL11 - AUXHFRCO Calibration Register (32 MHz)                                                 |   |  |  |  |     |

| 4.7.34 AUXHFRCOCAL12 - AUXHFRCO Calibration Register (38 MHz)                                                 |   |  |  |  |     |

| 4.7.35 VMONCAL0 - VMON Calibration Register 0                                                                 |   |  |  |  |     |

| 4.7.36 VMONCAL1 - VMON Calibration Register 1                                                                 |   |  |  |  |     |

| 4.7.37 VMONCAL2 - VMON Calibration Register 2                                                                 |   |  |  |  |     |

| 4.7.38 IDAC0CAL0 - IDAC0 Calibration Register 0                                                               |   |  |  |  |     |

| 4.7.39 IDACUCALT - IDACU Calibration Register 1                                                               |   |  |  |  | .94 |

|    | 4.7.41           | DCDCLPVCTRL0 - DCDC Low-power VREF Trim Register 0                | 95  |

|----|------------------|-------------------------------------------------------------------|-----|

|    | 4.7.42           | DCDCLPVCTRL1 - DCDC Low-power VREF Trim Register 1                | 96  |

|    | 4.7.43           | DCDCLPVCTRL2 - DCDC Low-power VREF Trim Register 2                | 97  |

|    | 4.7.44           | DCDCLPVCTRL3 - DCDC Low-power VREF Trim Register 3                |     |

|    | 4.7.45           | DCDCLPCMPHYSSEL0 - DCDC LPCMPHYSSEL Trim Register 0               |     |

|    | 4.7.46           | DCDCLPCMPHYSSEL1 - DCDC LPCMPHYSSEL Trim Register 1               |     |

|    | 4.7.47           |                                                                   |     |

|    | 4.7.48           | VDAC0ALTCAL - VDAC0 Cals for Alternate Path                       |     |

|    |                  | VDAC0CH1CAL - VDAC0 CH1 Error Cal                                 |     |

|    | 4.7.50           | OPA0CAL0 - OPA0 Calibration Register for DRIVESTRENGTH 0, INCBW=1 |     |

|    | 4.7.51           |                                                                   |     |

|    | 4.7.52           |                                                                   |     |

|    | 4.7.53           |                                                                   |     |

|    | 4.7.54           | OPA1CAL0 - OPA1 Calibration Register for DRIVESTRENGTH 0, INCBW=1 |     |

|    | 4.7.55           |                                                                   |     |

|    | 4.7.56           | OPA1CAL2 - OPA1 Calibration Register for DRIVESTRENGTH 2, INCBW=1 |     |

|    | 4.7.57           |                                                                   |     |

|    | 4.7.58           |                                                                   |     |

|    | 4.7.59           | OPA2CAL1 - OPA2 Calibration Register for DRIVESTRENGTH 1, INCBW=1 |     |

|    | 4.7.60           | OPA2CAL2 - OPA2 Calibration Register for DRIVESTRENGTH 2, INCBW=1 |     |

|    | 4.7.61           |                                                                   |     |

|    | 4.7.62           |                                                                   |     |

|    | 4.7.63           |                                                                   |     |

|    | 4.7.64           |                                                                   |     |

|    |                  | <b>y</b>                                                          |     |

|    | 4.7.65           | <b>y</b>                                                          |     |

|    | 4.7.66           | OPA0CAL7 - OPA0 Calibration Register for DRIVESTRENGTH 3, INCBW=0 |     |

|    | 4.7.67           | ,                                                                 |     |

|    | 4.7.68           | OPA1CALS - OPA1 Calibration Register for DRIVESTRENGTH 1, INCRW=0 |     |

|    | 4.7.69<br>4.7.70 | ,                                                                 |     |

|    | _                | OPA1CAL7 - OPA1 Calibration Register for DRIVESTRENGTH 3, INCRW=0 |     |

|    | 4.7.71           | ,                                                                 |     |

|    |                  | OPA2CALS - OPA2 Calibration Register for DRIVESTRENGTH 1, INCRW=0 |     |

|    |                  | OPA2CAL6 - OPA2 Calibration Register for DRIVESTRENGTH 2, INCRW=0 | _   |

|    | 4.7.74           | OPA2CAL7 - OPA2 Calibration Register for DRIVESTRENGTH 3, INCBW=0 | 127 |

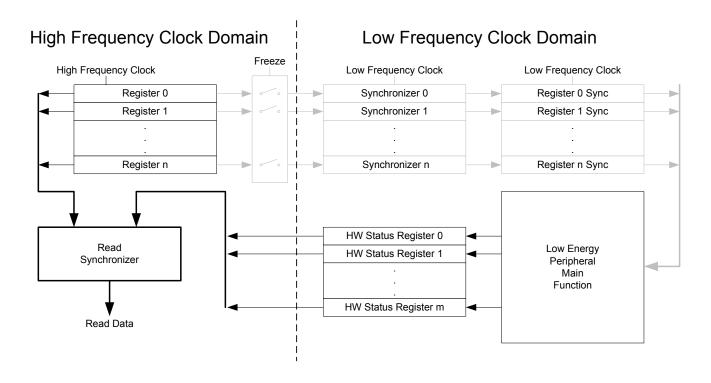

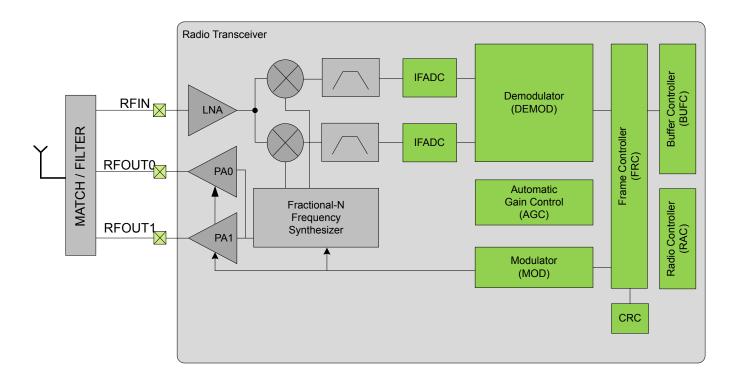

| 5. | Radio T          | ransceiver                                                        | 128 |

|    | 5.1 Introd       | duction                                                           | 129 |

|    |                  |                                                                   |     |

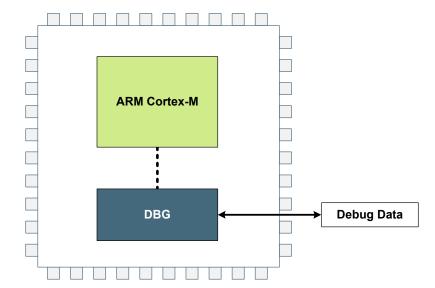

| 6. |                  | ebug Interface                                                    |     |

|    | 6.1 Introd       | duction                                                           | 130 |

|    | 6.2 Feat         | ures                                                              | 130 |

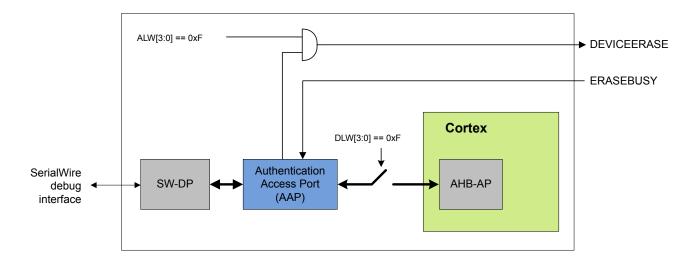

|    | 6.3 Fund         | ctional Description                                               | 130 |

|    |                  | Debug Pins                                                        |     |

|    |                  | Embedded Trace Macrocell V3.5 (ETM)                               |     |

|    |                  | Debug and EM2 Deep Sleep/EM3 Stop                                 |     |

|    |                  | Authentication Access Point                                       |     |

|    |                  | Debug Lock                                                        |     |

|    |                  | AAP Lock                                                          | 133 |

|    | 6.3.7 Debugger Reads of Actionable Registers                |       |

|----|-------------------------------------------------------------|-------|

|    | 6.3.8 Debug Recovery                                        |       |

|    | 6.4 Register Map                                            |       |

|    | 6.5 Register Description                                    |       |

|    | 6.5.1 AAP_CMD - Command Register                            |       |

|    | 6.5.2 AAP_CMDKEY - Command Key Register                     |       |

|    | 6.5.3 AAP_STATUS - Status Register                          |       |

|    | 6.5.4 AAP_CTRL - Control Register                           |       |

|    | 6.5.5 AAP_CRCCMD - CRC Command Register                     |       |

|    | 6.5.6 AAP_CRCSTATUS - CRC Status Register                   |       |

|    | 6.5.7 AAP_CRCADDR - CRC Address Register                    |       |

|    | 6.5.8 AAP_CRCRESULT - CRC Result Register                   |       |

|    | 6.5.9 AAP_IDR - AAP Identification Register                 | . 138 |

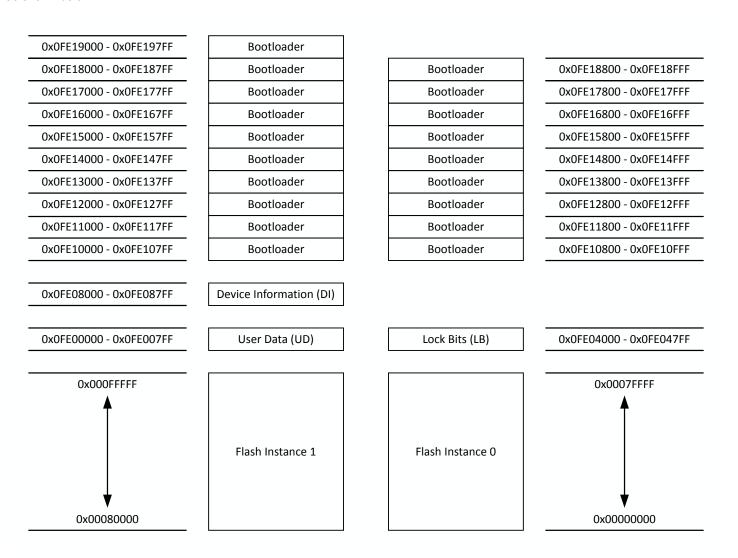

| 7. | MSC - Memory System Controller                              | 139   |

|    | 7.1 Introduction                                            | . 139 |

|    | 7.2 Features                                                | . 140 |

|    | 7.3 Functional Description                                  | 141   |

|    | 7.3.1 User Data (UD) Page Description                       |       |

|    | 7.3.2 Lock Bits (LB) Page Description                       |       |

|    | 7.3.3 Device Information (DI) Page                          |       |

|    | 7.3.4 Bootloader                                            |       |

|    | 7.3.5 Post-Reset Behavior                                   |       |

|    | 7.3.6 Flash Startup                                         | . 143 |

|    | 7.3.7 Wait States                                           | . 144 |

|    | 7.3.8 Suppressed Conditional Branch Target Prefetch (SCBTP) | . 144 |

|    | 7.3.9 Cortex-M4 If-Then Block Folding                       |       |

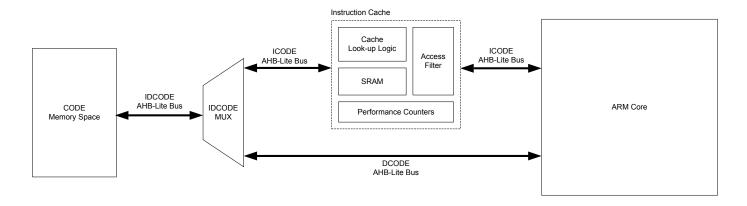

|    | 7.3.10 Instruction Cache                                    | .145  |

|    | 7.3.11 Low Voltage Flash Read                               |       |

|    | 7.3.12 Bank Switching Operation                             |       |

|    | 7.3.13 Erase and Write Operations                           | . 147 |

|    | 7.4 Register Map                                            | . 149 |

|    | 7.5 Register Description                                    | . 150 |

|    | 7.5.1 MSC_CTRL - Memory System Control Register             | . 150 |

|    | 7.5.2 MSC_READCTRL - Read Control Register                  | . 151 |

|    | 7.5.3 MSC_WRITECTRL - Write Control Register                | .152  |

|    | 7.5.4 MSC_WRITECMD - Write Command Register                 | 153   |

|    | 7.5.5 MSC_ADDRB - Page Erase/Write Address Buffer           |       |

|    | 7.5.6 MSC_WDATA - Write Data Register                       | . 154 |

|    | 7.5.7 MSC_STATUS - Status Register                          |       |

|    | 7.5.8 MSC_IF - Interrupt Flag Register                      |       |

|    | 7.5.9 MSC_IFS - Interrupt Flag Set Register                 |       |

|    | 7.5.10 MSC_IFC - Interrupt Flag Clear Register              |       |

|    | 7.5.11 MSC_IEN - Interrupt Enable Register                  |       |

|    | 7.5.12 MSC_LOCK - Configuration Lock Register               |       |

|    | 7.5.13 MSC_CACHECMD - Flash Cache Command Register          |       |

|    | 7.5.14 MSC CACHEHITS - Cache Hits Performance Counter       | 161   |

|    | 7.5.15 MSC_CACHEMISSES - Cache Misses Performance Counter                         | . 162 |

|----|-----------------------------------------------------------------------------------|-------|

|    | 7.5.16 MSC_MASSLOCK - Mass Erase Lock Register                                    | . 163 |

|    | 7.5.17 MSC_STARTUP - Startup Control                                              | 164   |

|    | 7.5.18 MSC_BANKSWITCHLOCK - Bank Switching Lock Register                          | 165   |

|    | 7.5.19 MSC_CMD - Command Register                                                 | . 166 |

|    | 7.5.20 MSC_BOOTLOADERCTRL - Bootloader Read and Write Enable, Write Once Register | 166   |

|    | 7.5.21 MSC_AAPUNLOCKCMD - Software Unlock AAP Command Register                    | 167   |

|    | 7.5.22 MSC_CACHECONFIG0 - Cache Configuration Register 0                          | . 168 |

|    | 7.5.23 MSC_RAMCTRL - RAM Control Enable Register                                  | 169   |

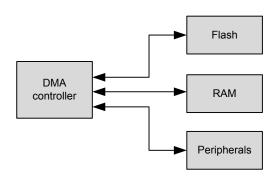

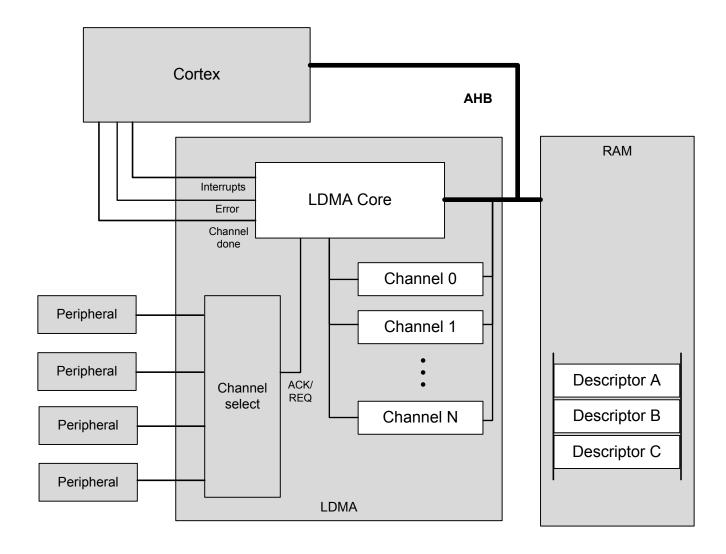

| 8. | LDMA - Linked DMA Controller                                                      | . 170 |

|    | 8.1 Introduction                                                                  | 170   |

|    | 8.1.1 Features                                                                    |       |

|    | 8.2 Block Diagram                                                                 | 172   |

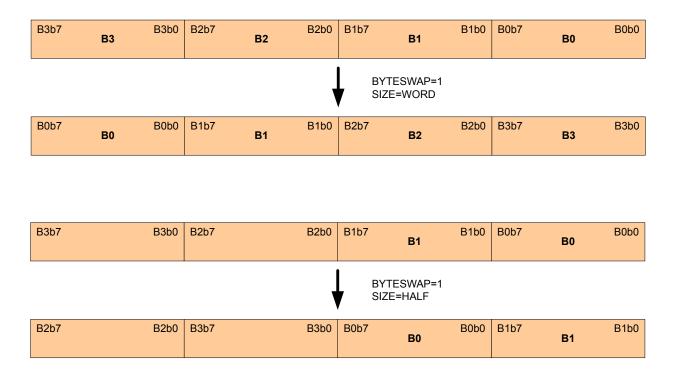

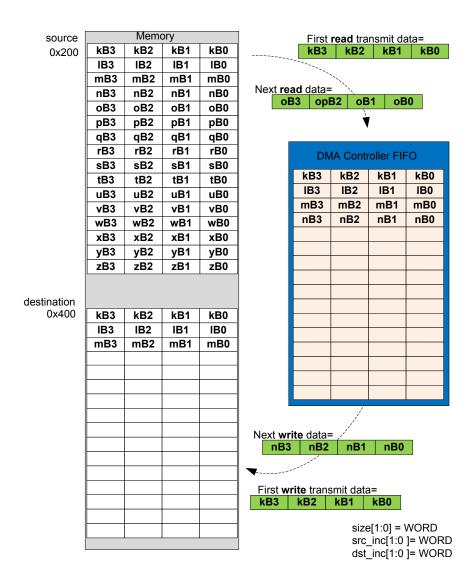

|    | 8.3 Functional Description                                                        |       |

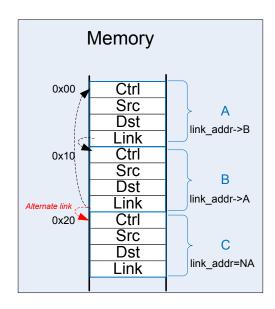

|    | 8.3.1 Channel Descriptor                                                          |       |

|    | 8.3.2 Channel Configuration                                                       |       |

|    | 8.3.3 Channel Select Configuration                                                |       |

|    | 8.3.4 Starting a Transfer                                                         |       |

|    | 8.3.5 Managing Transfer Errors                                                    |       |

|    | 8.3.6 Arbitration                                                                 |       |

|    | 8.3.7 Channel Descriptor Data Structure                                           |       |

|    | 8.3.8 Interaction With the EMU                                                    |       |

|    | 8.3.9 Interrupts                                                                  |       |

|    | 8.3.10 Debugging                                                                  |       |

|    | 8.4 Examples                                                                      |       |

|    | 8.4.1 Single Direct Register DMA Transfer                                         |       |

|    | 8.4.2 Descriptor Linked List                                                      |       |

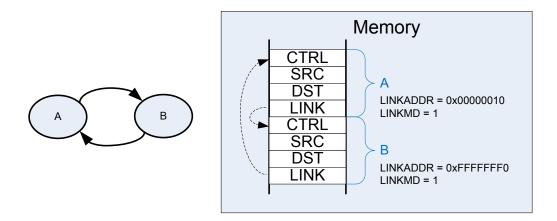

|    | 8.4.3 Single Descriptor Looped Transfer                                           |       |

|    | 8.4.4 Descriptor List With Looping                                                |       |

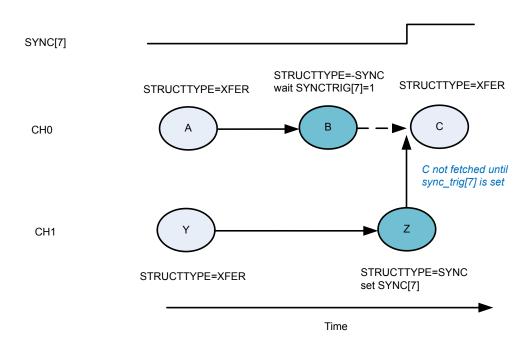

|    | 8.4.5 Simple Inter-Channel Synchronization.                                       |       |

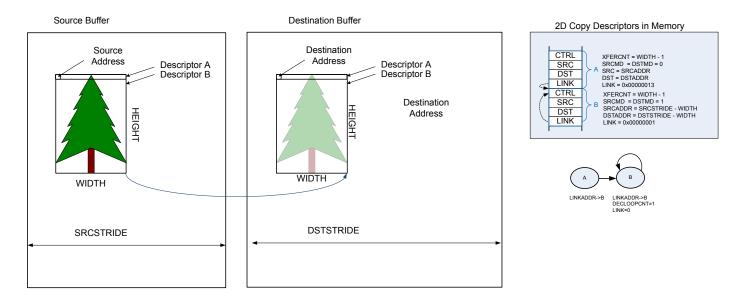

|    | 8.4.6 2D Copy                                                                     |       |

|    | 8.4.7 Ping-Pong                                                                   |       |

|    | 8.4.8 Scatter-Gather                                                              |       |

|    | 8.5 Register Map                                                                  |       |

|    | 8.6 Register Description                                                          |       |

|    | 8.6.1 LDMA CTRL - DMA Control Register                                            |       |

|    | 8.6.2 LDMA STATUS - DMA Status Register                                           |       |

|    | 8.6.3 LDMA_SYNC - DMA Synchronization Trigger Register (Single-Cycle RMW)         |       |

|    | 8.6.4 LDMA_CHEN - DMA Channel Enable Register (Single-Cycle RMW)                  |       |

|    | 8.6.5 LDMA CHBUSY - DMA Channel Busy Register                                     |       |

|    | 8.6.6 LDMA_CHDONE - DMA Channel Linking Done Register (Single-Cycle RMW)          |       |

|    | 8.6.7 LDMA DBGHALT - DMA Channel Debug Halt Register                              |       |

|    | 8.6.8 LDMA_SWREQ - DMA Channel Software Transfer Request Register                 |       |

|    | 8.6.9 LDMA REQDIS - DMA Channel Request Disable Register                          |       |

|    | 8.6.10 LDMA REQPEND - DMA Channel Requests Pending Register                       |       |

|    | 8.6.11 LDMA_REGREND - DMA Channel Link Load Register                              |       |

|    |                                                                                   |       |

|    | 8.6.12     | LDMA_REQCLEAR - DMA Channel Request Clear Register                  | .204  |

|----|------------|---------------------------------------------------------------------|-------|

|    | 8.6.13     | LDMA_IF - Interrupt Flag Register                                   | . 205 |

|    | 8.6.14     | LDMA_IFS - Interrupt Flag Set Register                              | .205  |

|    | 8.6.15     | LDMA_IFC - Interrupt Flag Clear Register                            | 206   |

|    | 8.6.16     | LDMA_IEN - Interrupt Enable Register                                | . 206 |

|    | 8.6.17     | LDMA_CHx_REQSEL - Channel Peripheral Request Select Register        | .207  |

|    | 8.6.18     | LDMA_CHx_CFG - Channel Configuration Register                       | .211  |

|    |            | LDMA_CHx_LOOP - Channel Loop Counter Register                       |       |

|    | 8.6.20     | LDMA_CHx_CTRL - Channel Descriptor Control Word Register            | . 213 |

|    | 8.6.21     | LDMA_CHx_SRC - Channel Descriptor Source Data Address Register      | . 216 |

|    | 8.6.22     | LDMA_CHx_DST - Channel Descriptor Destination Data Address Register | .216  |

|    | 8.6.23     | LDMA_CHx_LINK - Channel Descriptor Link Structure Address Register  | . 217 |

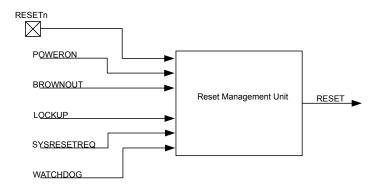

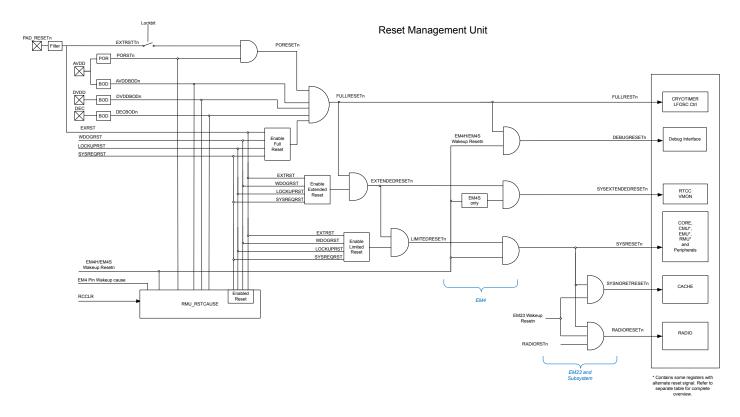

| ۵  | DMII_D     | eset Management Unit                                                | 212   |

| ٥. |            | duction                                                             |       |

|    |            |                                                                     |       |

|    |            | ıres                                                                |       |

|    |            | tional Description                                                  |       |

|    |            | Reset Levels                                                        |       |

|    |            | RMU_RSTCAUSE Register                                               |       |

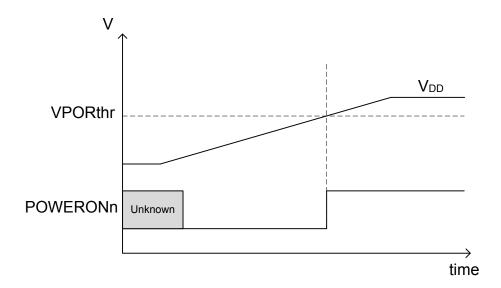

|    |            | Power-On Reset (POR)                                                |       |

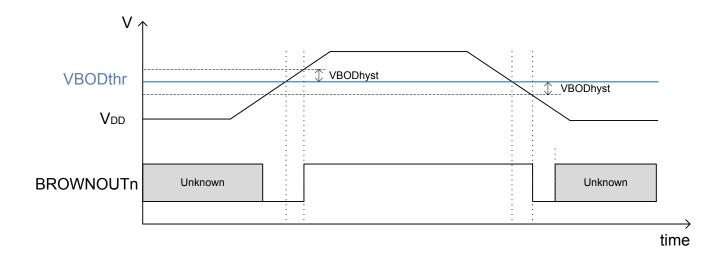

|    |            | Brown-Out Detector (BOD)                                            |       |

|    |            | RESETn Pin Reset                                                    |       |

|    |            | Vatchdog Reset                                                      |       |

|    |            | ockup Reset                                                         |       |

|    |            | System Reset Request                                                |       |

|    |            | Reset State                                                         |       |

|    | 9.3.10     | Register Reset Signals                                              | 223   |

|    | 9.4 Regis  | ster Map                                                            | 225   |

|    | 9.5 Regis  | ster Description                                                    | .226  |

|    | 9.5.1 F    | RMU_CTRL - Control Register                                         | . 226 |

|    |            | RMU_RSTCAUSE - Reset Cause Register                                 |       |

|    | 9.5.3 F    | RMU_CMD - Command Register                                          | . 229 |

|    |            | RMU_RST - Reset Control Register                                    |       |

|    | 9.5.5 F    | RMU_LOCK - Configuration Lock Register                              | . 230 |

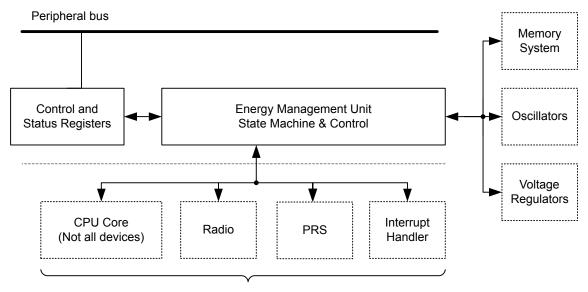

| 10 | ). EMU - E | Energy Management Unit                                              | . 231 |

|    |            | oduction.                                                           |       |

|    | 10.2 Fea   |                                                                     |       |

|    |            |                                                                     |       |

|    |            | ctional Description                                                 |       |

|    |            | Energy Modes                                                        |       |

|    |            | Entering Low Energy Modes                                           |       |

|    |            | Exiting a Low Energy Mode                                           |       |

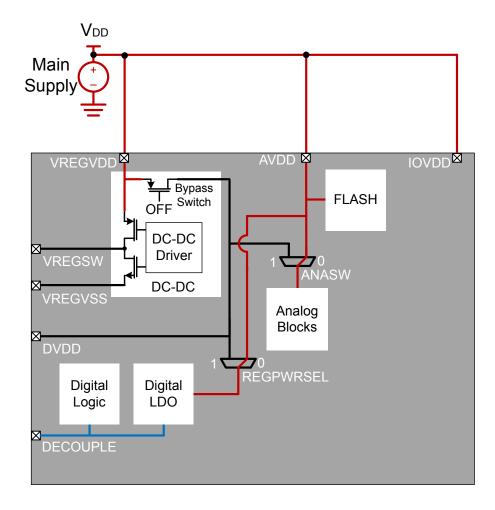

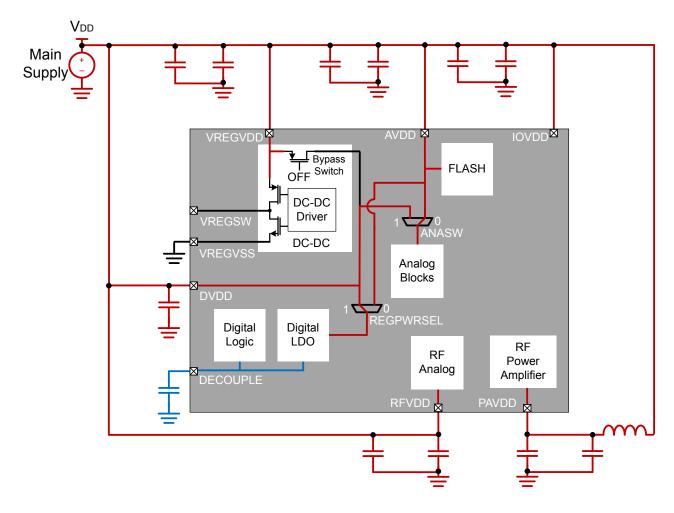

|    |            | Power Configurations                                                |       |

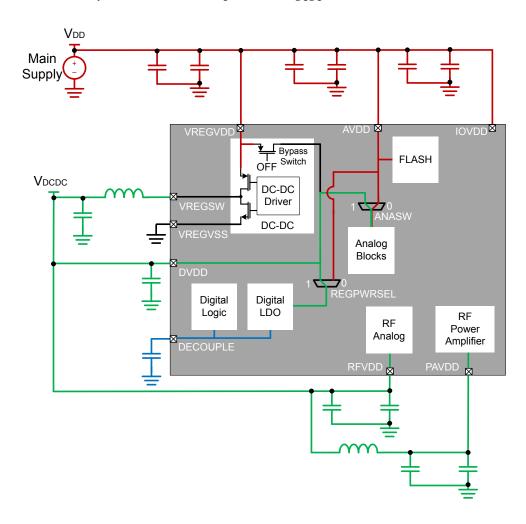

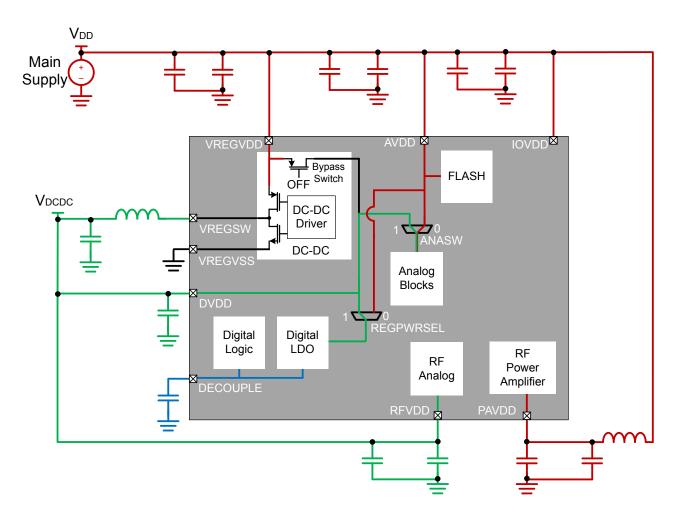

|    |            | DC-to-DC Interface                                                  |       |

|    |            | Analog Peripheral Power Selection                                   |       |

|    |            | Digital LDO Power Selection                                         |       |

|    | 10.38      | IOVDD Connection.                                                   | . 248 |

| 10.3.9 Voltage Scaling                                                                 | . 249 |

|----------------------------------------------------------------------------------------|-------|

| 10.3.10 EM2/EM3 Peripheral Retention Disable                                           | .251  |

| 10.3.11 Brown Out Detector (BOD)                                                       | 251   |

| 10.3.12 Voltage Monitor (VMON)                                                         | 252   |

| 10.3.13 Powering Off SRAM Blocks                                                       | 253   |

| 10.3.14 Temperature Sensor                                                             |       |

| 10.3.15 Registers latched in EM4                                                       | .254  |

| 10.3.16 Register Resets                                                                | .254  |

| 10.4 Register Map                                                                      | . 255 |

| 10.5 Register Description                                                              | . 257 |

| 10.5.1 EMU_CTRL - Control Register                                                     | 257   |

| 10.5.2 EMU_STATUS - Status Register                                                    | 259   |

| 10.5.3 EMU_LOCK - Configuration Lock Register                                          | .261  |

| 10.5.4 EMU_RAM0CTRL - Memory Control Register                                          |       |

| 10.5.5 EMU_CMD - Command Register                                                      | 263   |

| 10.5.6 EMU_EM4CTRL - EM4 Control Register                                              | . 264 |

| 10.5.7 EMU_TEMPLIMITS - Temperature Limits for Interrupt Generation                    | 265   |

| 10.5.8 EMU_TEMP - Value of Last Temperature Measurement                                | 265   |

| 10.5.9 EMU_IF - Interrupt Flag Register                                                | 266   |

| 10.5.10 EMU_IFS - Interrupt Flag Set Register                                          | .268  |

| 10.5.11 EMU_IFC - Interrupt Flag Clear Register                                        | 270   |

| 10.5.12 EMU_IEN - Interrupt Enable Register                                            | 272   |

| 10.5.13 EMU_PWRLOCK - Regulator and Supply Lock Register                               | .274  |

| 10.5.14 EMU_PWRCFG - Power Configuration Register                                      |       |

| 10.5.15 EMU_PWRCTRL - Power Control Register                                           | 276   |

| 10.5.16 EMU_DCDCCTRL - DCDC Control                                                    | .277  |

| 10.5.17 EMU_DCDCMISCCTRL - DCDC Miscellaneous Control Register                         | . 278 |

| 10.5.18 EMU_DCDCZDETCTRL - DCDC Power Train NFET Zero Current Detector Control         |       |

| Register                                                                               |       |

| 10.5.19 EMU_DCDCCLIMCTRL - DCDC Power Train PFET Current Limiter Control Register .    |       |

| 10.5.20 EMU_DCDCLNCOMPCTRL - DCDC Low Noise Compensator Control Register               |       |

| 10.5.21 EMU_DCDCLNVCTRL - DCDC Low Noise Voltage Register                              |       |

| 10.5.22 EMU_DCDCLPVCTRL - DCDC Low Power Voltage Register                              |       |

| 10.5.23 EMU_DCDCLPCTRL - DCDC Low Power Control Register                               |       |

| 10.5.24 EMU_DCDCLNFREQCTRL - DCDC Low Noise Controller Frequency Control               |       |

| 10.5.25 EMU_DCDCSYNC - DCDC Read Status Register                                       |       |

| 10.5.26 EMU_VMONAVDDCTRL - VMON AVDD Channel Control                                   |       |

| 10.5.27 EMU_VMONALTAVDDCTRL - Alternate VMON AVDD Channel Control                      |       |

| 10.5.28 EMU_VMONDVDDCTRL - VMON DVDD Channel Control                                   |       |

| 10.5.29 EMU_VMONIO0CTRL - VMON IOVDD0 Channel Control                                  |       |

| 10.5.30 EMU_RAM1CTRL - Memory Control Register                                         |       |

| 10.5.31 EMU_RAM2CTRL - Memory Control Register                                         | . 292 |

| 10.5.32 EMU_DCDCLPEM01CFG - Configuration Bits for Low Power Mode to Be Applied During | ാറാ   |

| EM01, This Field is Only Relevant If LP Mode is Used in EM01                           | . 293 |

| EMOODEDNOODETAINOTATUO III. III. A                                                     | . 294 |

| 10.5.34 EMU_EM23PERNORETAINSTATUS - Status Indicating If Peripherals Were Powered      | . 207 |

| Down in FM23. Subsequently Locking Access to It                                        | 296   |

| 10.5.35 EMU_EM23PERNORETAINCTRL - When Set Corresponding Peripherals May Get Powered Down in EM23 | . 298 |

|---------------------------------------------------------------------------------------------------|-------|

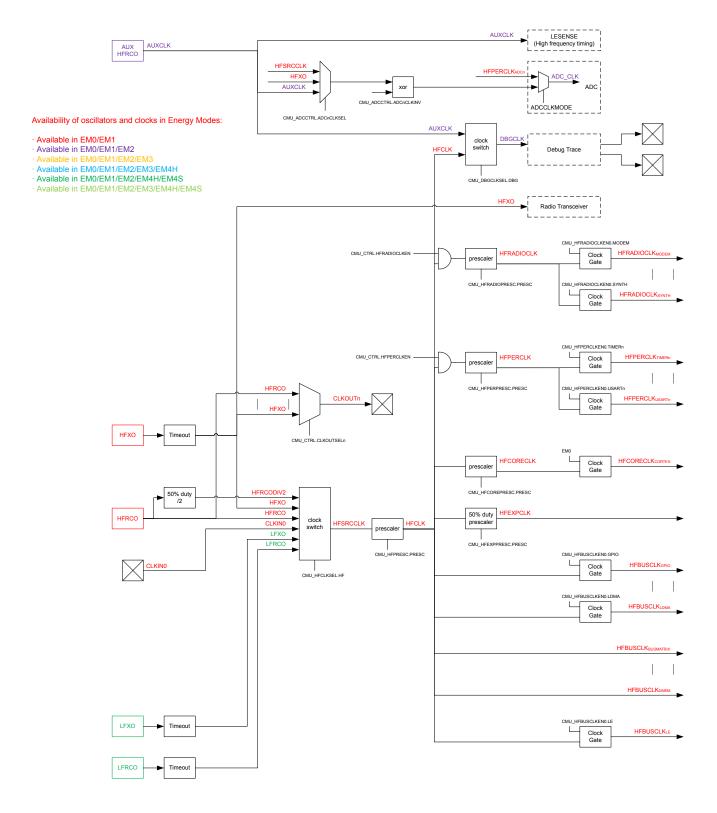

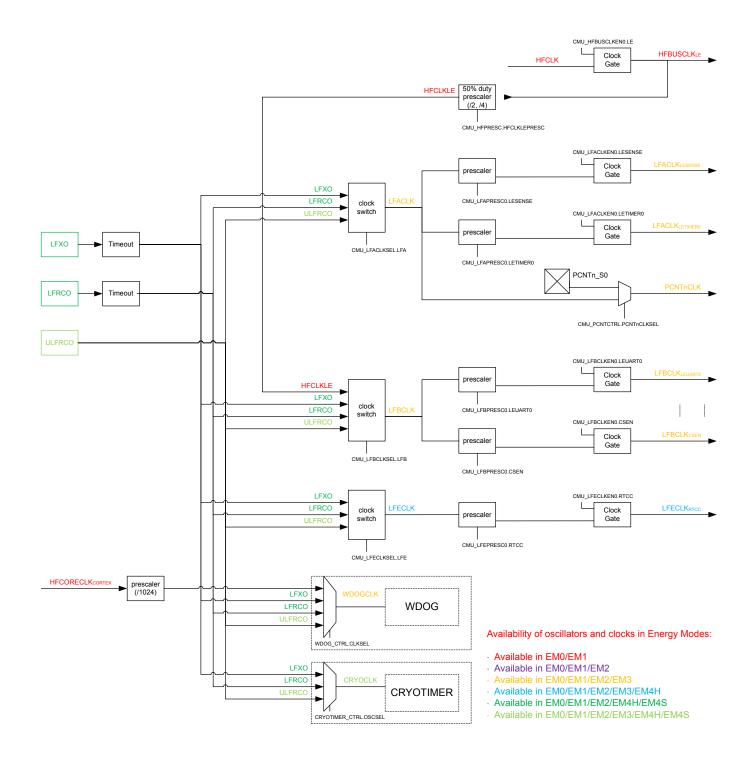

| I1. CMU - Clock Management Unit                                                                   | .300  |

| 11.1 Introduction                                                                                 | . 300 |

| 11.2 Features                                                                                     | . 300 |

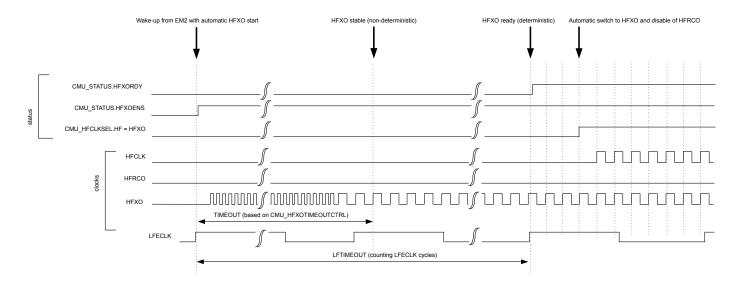

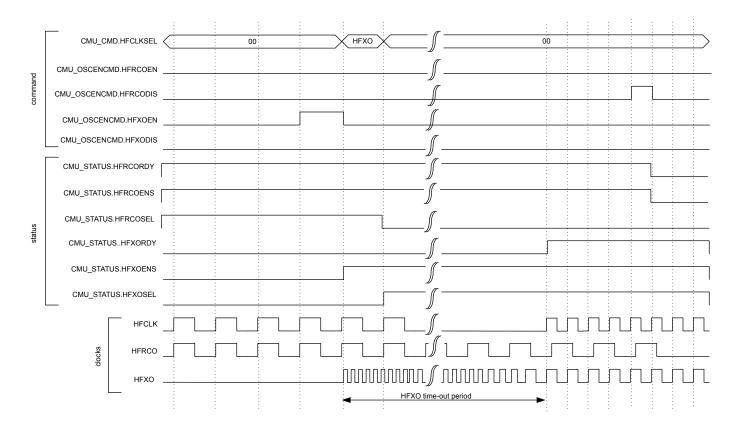

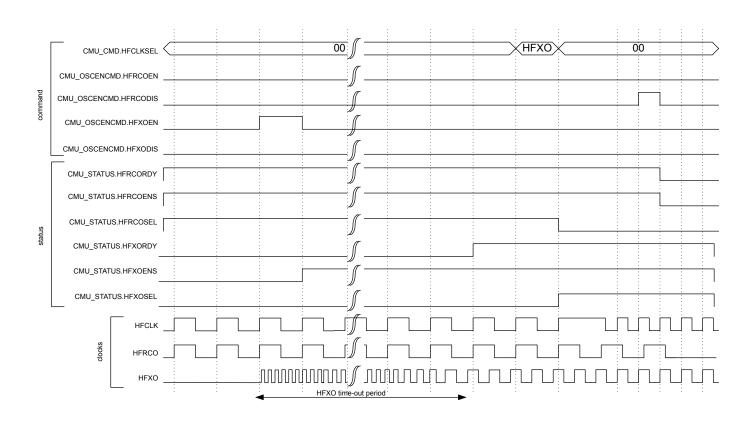

| 11.3 Functional Description                                                                       | . 301 |

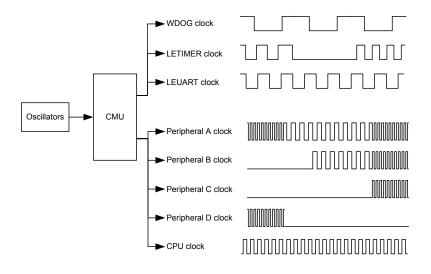

| 11.3.1 System Clocks                                                                              |       |

| 11.3.2 Oscillators                                                                                |       |

| 11.3.3 Configuration for Operating Frequencies                                                    | . 323 |

| 11.3.4 Energy Modes                                                                               |       |