# **UG460: EFR32 Series 1 Long Range Configuration Reference**

To help customers achieve the crucial design element of maximum effective range, Silicon Labs has developed a Long Range radio profile for the EFR32 Series 1 family of Wireless MCU devices. This guide introduces the profile, describes its development, and examines underlying details that enable it to realize extended range. It also includes an exercise to build a Range Test example using Simplicity Studio 5 and to explore the Long Range profile, so that you can guickly begin implementation in your next project.

This guide is designed for developers who would like to test long range performance on EFR32 Series 1 devices using Simplicity Studio 5 and Silicon Labs development hardware. It provides instructions to get started using the example applications provided with the Gecko SDK Suite (GSDK) v3.

#### **KEY FEATURES**

- Learn about DSSS

- Learn about the Long Range Profile

- Learn about the Radio Configurator

- Create a Range Test application with a long range PHY

#### 1 Introduction

One of the most important performance metrics for an IoT application is maximum usable range. Practically speaking, this refers to the maximum distance at which messages can be received without a loss of information. The achievable range is impacted by many different factors:

- Hardware influences, including:

- Antenna physical parameters (size, shape, directivity, gain)

- Battery physical parameters (size, capacity, load current, and so on)

- Propagation attributes of the radio signal (carrier frequency, humidity, obstacles, and so on)

- Transmit power

- Receiver sensitivity

To maximize usable range, when developing the Long Range (LR) profile Silicon Labs targeted the last item above, receiver sensitivity, which is affected by multiple input parameters:

- Frame length: The amount of data to be transported

- Data rate: The timeframe available to transport the data

- Data rate offset tolerance: How much the data rate can change during reception

- · Frequency offset tolerance: How severely the carrier frequency can vary during the reception

- Selectivity and blocking: Robustness against interferer signals

Though many paths can be taken to improve RX sensitivity, Silicon Labs avoided hardware changes and instead focused on radio configuration modifications. This reliance on PHY development insulated the Long Range profile from additional external hardware dependencies, making the LR PHY benefits available to a broader selection of applications.

The construction of these PHYs is detailed in the next chapter. Chapter 3 provides instructions on evaluating the Long Range Profile using new Silicon Labs development tools and hardware. Chapter 4 reviews real-world measured performance with the LR PHYs.

# 2 Development of the EFR32 Long Range PHYs

The fundamental approach to extend usable range in the LR Profile was to decrease receiver bandwidth, while keeping key signal parameters for the demodulator, such as modulation index for FSK, intact. A few rules of thumb help to visualize what was available for this effort:

- Reducing bandwidth by half improves sensitivity by 3 dB

- Reducing bandwidth by 90% (to 1/10th of the original) boosts sensitivity by 10 dB

A straightforward compromise to achieve bandwidth reduction is to decrease the data rate. By cutting bandwidth in favor of sensitivity, one has to also contend with the resulting degradation in frequency offset tolerance. Moreover, such narrow-band PHYs require very accurate and stable clock references (for example, a 0.5 ppm TCXO), and those elements are more costly. In terms of RF immunity, the effect of going narrow band is mixed, with some improvement in selectivity and blocking offset by extended exposure time to interferers due to the reduced data rate.

Importantly, all of these drawbacks can be mitigated by using Direct Sequence Spectral Spreading (DSSS). This technique, which is available for all major modulation formats on the EFR32, is explored in the following section.

### 2.1 DSSS: Theory of Operation

DSSS is a technique to increase the bandwidth of a transmitted signal, and thereby decrease its power spectral density. It is beneficial for the receiver side as well, as the robustness (immunity against interferer signals) significantly improves. This section reviews the DSSS implementation on EFR32 Series 1 devices.

#### 2.1.1 TX Side

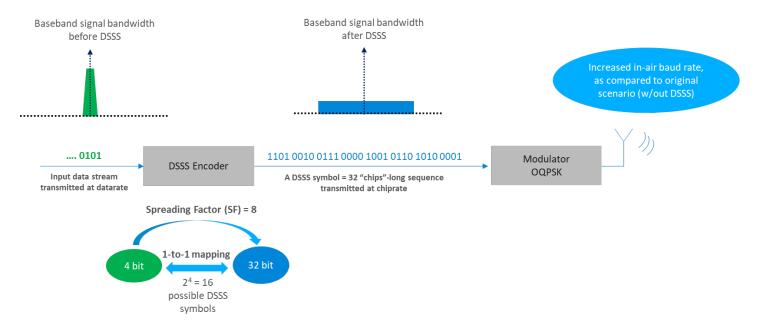

Figure 2-1. Transmission of 802.15.4 Signals Using DSSS

The above figure shows how a DSSS-based signal is constructed. As a practical demonstration vehicle, this example uses the 802.15.4 Zigbee packet format.

The baseband input signal is a narrow band, low data rate signal stream (its spectrum plot represented by the green cone). This bitstream is fed into a DSSS encoder, which replaces every 4 bits of the bitstream with a 32-bit symbol, often referred to as 32 "chips".

Transmitting 1 symbol takes the same amount of time as transmitting 4 bits of the original data stream. This means that the "chip rate" is 8x higher than the original data rate, a multiplier often referred to as the Spreading Factor.

The blue rectangle (spectrum plot of baseband input signal after DSSS encoding) demonstrates that the original narrow band signal has become much wider (though not quite 8x), with less power density. The resulting data stream with the chip rate is then fed into the

modulator and radiated over the air. Therefore, by increasing the link's in-air baud rate, the same data can be transmitted with the same net data rate, over the same period of time, but using a much wider band and lower power spectral density.

#### 2.1.2 RX Side

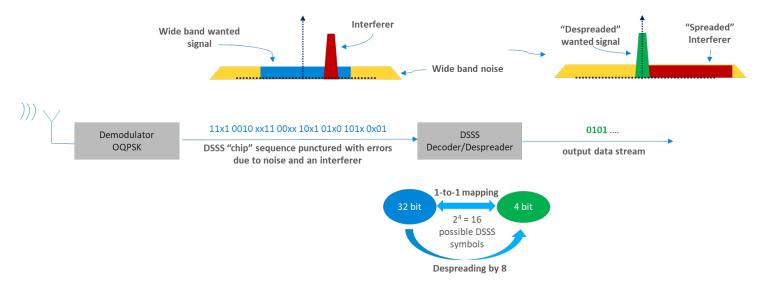

Figure 2-2. Reception of 802.15.4 Signals Using DSSS

The above figure shows reception of the DSSS-encoded transmission detailed in the previous section. The demodulator retrieves the data stream from the OQPSK signal. The bits are changing with the chip rate, and the stream may contain errors due to the presence of noise and interferers in the air.

The plot at the top left corner of the above figure demonstrates the spectral conditions while receiving a DSSS packet. The red pyramid indicates the presence of a strong narrowband interferer, while the yellow trapezium represents the wideband noise.

This corrupted chip stream is fed into the DSSS Decoder, which replaces every 32-chip long symbol with a 4 bit pattern, thus restoring the original data stream. Despite errors in the chip stream, the decoder can still identify the correct 32-chip symbols due to the 8x redundancy presented by the scaling factor.

The spectrum plot at the top right corner of the figure shows that the original green cone has been restored by this de-spreading procedure, while the red cone has been "smeared" with the noise. As a result, SNR is increased, which compensates for the increased noise power experienced by the demodulator due to the high in-air bandwidth.

## 2.2 DSSS: Practical Impacts

As a result of using DSSS, an application is subject to the following considerations:

- Co-channel and adjacent channel selectivity improve by a factor of the coding gain (3 to 8 dB, depending on spreading factor)

- A less accurate (cheaper) crystal can be used for the clock reference

- · Higher TX power can be used in cases where the regulatory limit is defined as maximum allowed power spectral density

- DSSS alone does not technically improve RX sensitivity to in-air signals:

- Receiving a 1 kbps data stream exhibits the same RX sensitivity whether or not the signal content is DSSS-encoded

- DSSS increases the symbol rate and bandwidth of the signal physically present in the air, which actually degrades reception at the RX side, but this consequence is compensated by the DSSS **processing gain** in the receiver

# 2.3 Scaling the 802.15.4 PHY

To leverage the benefits of DSSS and develop robust Long Range options for EFR32 Series 1 devices, Silicon Labs began with the highly optimized 802.15.4 Zigbee PHY, and derived a series of radio configurations to serve a variety of sensitivity and tolerance requirements. Essentially, the data rate (and therefore the occupied bandwidth) has been scaled down, while retaining the same Zigbee coding scheme: OQPSK, DSSS SF=8, and 32-bit symbol length with a 4-bit symbol map. The resulting PHY configurations are available for xG12 / xG13 / xG14 variants of the Series 1 family.

The following table shows one group of PHYs optimized for a lower frequency band, and another group optimized at a higher frequency band. Notably, the stated performance is maintained when setting the carrier frequency to anywhere within each band.

The table indicates the required XO accuracy for the TX and RX side COMBINED. Practically speaking, the value in the table should be SPLIT between TX and RX sides. This presents a cost savings opportunity on nodes manufactured in large quantities vs low volume base stations, where you can asymmetrically distribute the XO accuracy budget to reduce the cost of high volume elements.

<u>Note:</u> The last item, 80 kbps for 915MHz, can be used to pass FCC 15.247 requirements without the need for frequency hopping, as the occupied bandwidth of the signal is > 500 kHz.

Table 1-1. PHY Configuration Options on the Long Range Profile

| Frequency Band<br>[MHz] | Data Rate<br>[kbps] | (TX + RX) XO Accuracy<br>[ppm +/-] |

|-------------------------|---------------------|------------------------------------|

| 434/490                 | 1.2                 | 2.5                                |

| 434/490                 | 2.4                 | 5                                  |

| 434/490                 | 4.8                 | 10                                 |

| 434/490                 | 9.6                 | 20                                 |

| 434/490                 | 19.2                | 40                                 |

| 868/915                 | 1.2                 | 1.25                               |

| 868/915                 | 4.8                 | 5                                  |

| 868/915                 | 9.6                 | 10                                 |

| 868/915                 | 19.2                | 20                                 |

| 868/915                 | 38.4                | 40                                 |

| 868/915                 | 80                  | 40                                 |

#### 2.4 Radio Boards Supporting Long Range PHY Evaluation

Many configurations within the Long Range Profile can be successfully demonstrated on any radio board with a supported EFR32 Series 1 SoC and suitable sub-GHz band support. However, for those users who would like to test the best possible narrow band PHY configurations, radio boards that satisfy the XO requirements in Table 1-1. PHY Configuration Options on the Long Range Profile are also available for purchase. The following table specifies the configurations Silicon Labs currently offers.

Table 1-2. Radio Boards with TCXO

| Ordering Part Number | Board ID | Board Configuration                         |

|----------------------|----------|---------------------------------------------|

| SLWRB4261A           | BRD4261A | EFR32FG14 Dual-Band 2400 / 490 MHz +19.5dBm |

| SLWRB4262A           | BRD4262A | EFR32FG14 Dual-Band 2400 / 915 MHz +19.5dBm |

| SLWRB4262B           | BRD4262B | EFR32FG14 Dual-Band 2400 / 868 MHz +19.5dBm |

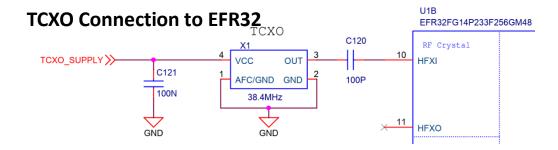

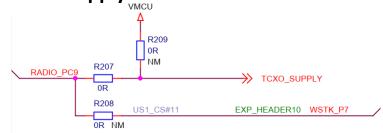

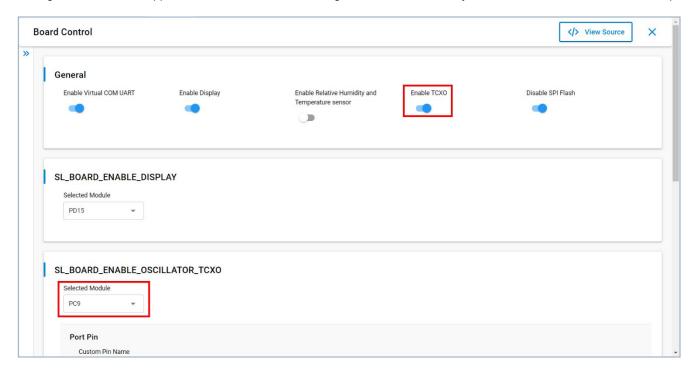

These boards are equipped with a high performance (+/- 0.5 ppm accuracy) TCXO for the HFXO reference, as shown by the schematics in the following figure. The TCXO supply is connected to pin PC9 on the SoC, which enables the EFR32 to shut down the TCXO when not in use to save power. If the customer application needs PC9 for a different purpose, the TCXO power supply can instead be connected directly to the VMCU rail (via the R209 solder dot seen in the following figure).

**TCXO** Power supply

Figure 2-3. TCXO Connection to the SoC and the Power Supply

Figure 2-4. TCXO-based Radio Board and Wireless Starter Kit (WTSK) Board

# 3 Using the Long Range Profile in Simplicity Studio 5

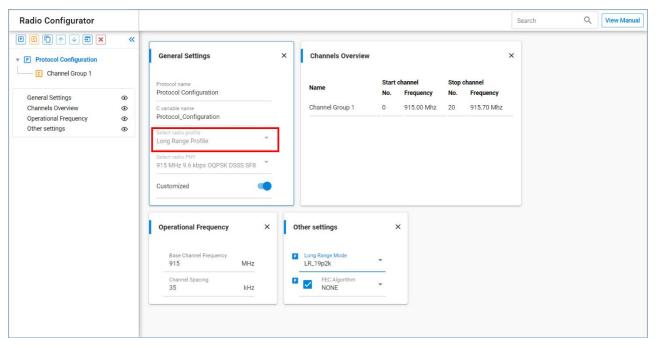

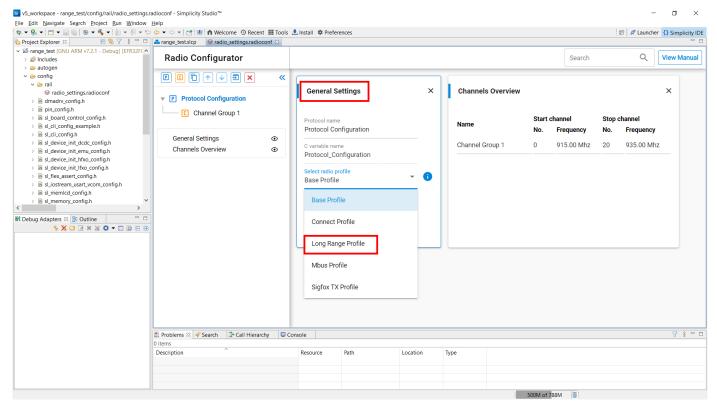

## 3.1 Long Range Profile in the Radio Configurator

Simplicity Studio 5 (SSv5) makes it easy to access Long Range PHY configurations by selecting the new "Long Range" profile in the Radio Configurator interface. If you need a refresher, please see the <u>Simplicity Studio 5 User's Guide</u> and AN1253: EFR32 Radio Configurator Guide for Simplicity Studio 5 for more information on building an example wireless application with the Radio Configurator.

Click the **Select radio profile** drop-down field, and select **Long Range Profile**. Note that PHYs in this profile have reduced configuration options (carrier frequency, and FEC enable), described here:

- Carrier frequency can be set to anywhere within each band baseband performance will be sustained at all frequencies within a given band. However, be aware that external components can exhibit a frequency dependence.

- 425MHz to 525MHz, or 860MHz to 930 MHz

- FEC (Forward Error Correction) can be enabled for any of the PHY configurations:

- FEC in EFR32 Series 1 simply doubles the number of transmitted symbols. Enabling FEC does not automatically adjust the data rate. To maintain the original effective throughput, manually select a data rate that is twice the original rate.

- FEC does not increase sensitivity, but it can protect against missing bits due to interferer signals.

- Silicon Labs Connect does not currently support FEC, so if you plan to use these PHYs with Connect, do not enable FEC.

The next section provides a procedure to construct a complete example application with which to evaluate PHYs in the Long Range Profile using two EFR32 radio boards.

# 3.2 Build a Range Test Example Application

This section describes the steps to build a Range Test application, and is based on <u>UG147: Range Test Demo User's Guide</u>. Additional guidance on using the Range Test application can be found in <u>this article</u>. The procedure assumes that you have downloaded the Flex SDK, and have connected the two boards required for this example, as described in the <u>Simplicity Studio 5 User's Guide</u>.

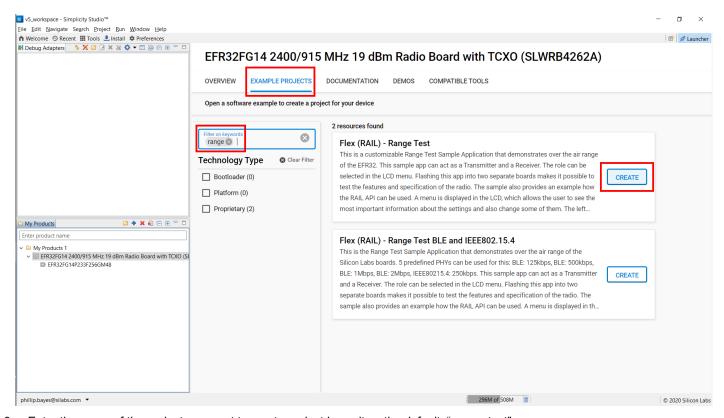

- 1. Click the "Example Projects" tab to see the projects available for the selected target hardware.

- 2. Scroll down or use the example filter to locate the "Flex (RAIL) Range Test" project, then click CREATE.

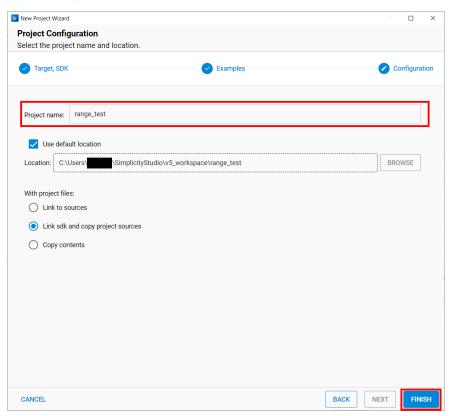

3. Enter the name of the project you want to create, or just leave it as the default, "range\_test"...

Click FINISH to create the new project.

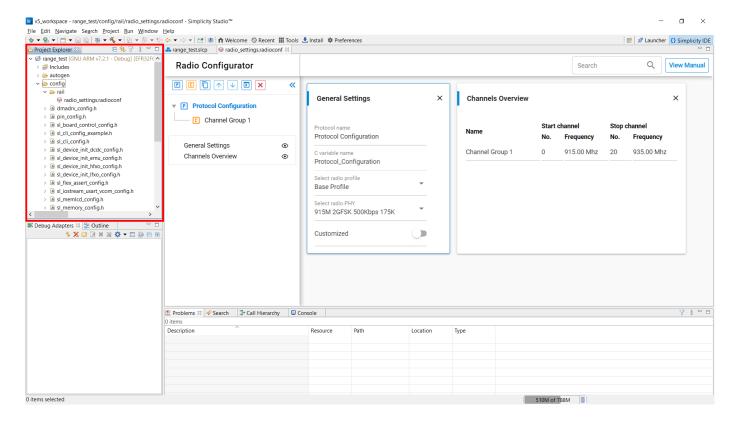

5. Once the project is created, SSv5 opens the Simplicity IDE perspective, and the radio configuration GUI appears. From the Project Explorer view you can see the project files that have been generated.

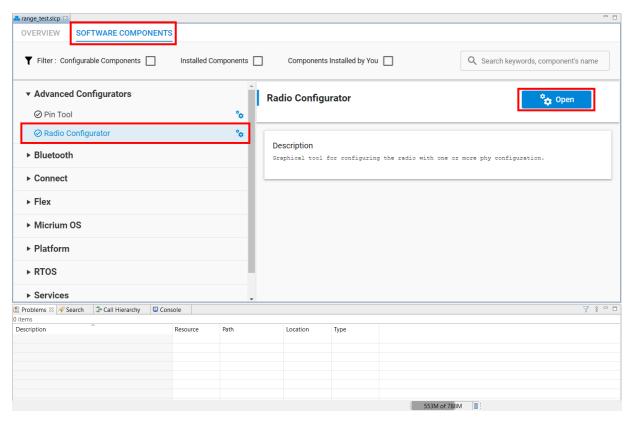

If you close this tab, the Radio Configurator can be accessed again at any time via the Software Components tab. Click the Advanced Configurators item, then Radio Configurator (alternatively, you can simply search for configurator using the search input at the top right of the .slcp frame). Once this Radio Configurator gateway element has been located, simply click **OPEN** to its right and proceed to the next step.

If you have a radio board with a TCXO on it, SSv5 automatically preconfigures your project to support it and adds the code segments enabling the TCXO to the application. For reference, the configuration can be manually overridden via the Board Control component.

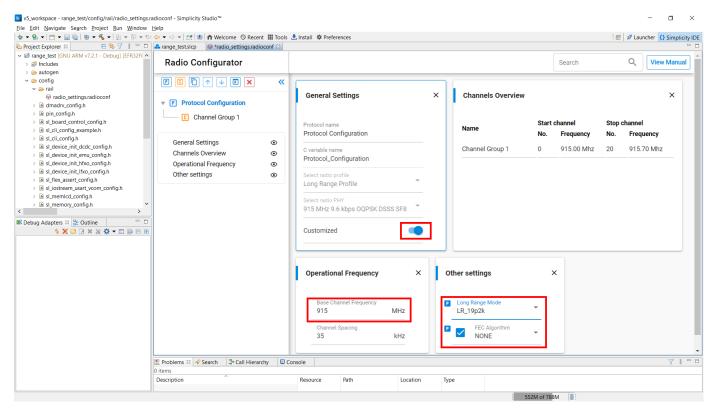

- 6. Before configuring a Long Range PHY, you must adjust the selected radio profile for the project. On the Navigation Panel, click **Protocol Configuration**. You should see the **General Settings** and **Channel Overview** cards open in the editor window on the right.

- 7. On the General Settings card, click the Select radio profile drop-down field, and select Long Range Profile.

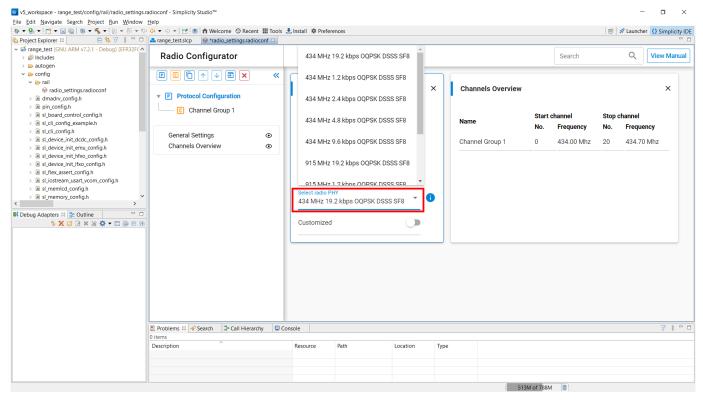

- On the Select radio PHY field, choose one of the predefined long range configurations, keeping the following guidance in mind:

- For 434-490 MHz boards, select a 434 MHz config.

- For 868-915 MHz boards, select a 915 MHz config.

- Please note that Silicon Labs typical radio boards have a +/- 10ppm crystal as a reference. Refer to PHY config XO tolerances in Table 1-1. PHY Configuration Options on the Long Range Profile above to verify support for your preferred PHY using two (2) +/- 10ppm radio boards (+/- 20ppm combined). If your PHY of choice requires tighter tolerance, use the TCXO-equipped radio boards listed in Table 1-2. Radio Boards with TCXO.

- 9. Enable the Customized switch, to allow fine tuning of the selected PHY config.

- 10. On the Operational Frequency card, set the Base Channel Frequency according to your planned operating band.

- 11. On the Other settings card, you have the option to override the data rate selection and/or to enable FEC.

(Note: On an EFR32, enabling FEC doubles the number of transmitted symbols, but does not automatically adjust the data rate. To retain the original (before enabling FEC) effective throughput with FEC, you must manually select a doubled data rate.)

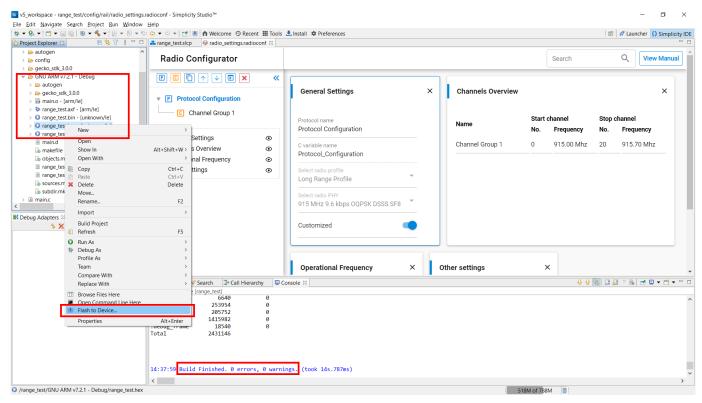

12. Build the project by clicking the hammer toolbar button.

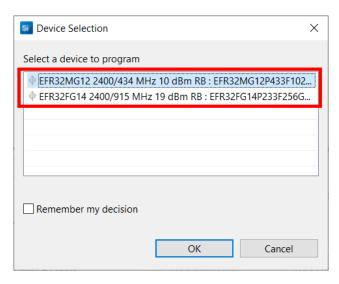

13. Once built, flash the generated hex file to the target by right-clicking the *project name*.hex file in the "GNU ARM v7.2.1 – Debug" folder, and selecting **Flash to Device...**

14. The Flash Programmer will open. Click Program to download the code to the target.

15. Now flash the same .hex file to your second radio board. Select the other WSTK mainboard as the target device, and click Program.

# 4 Measured Performance of the Long Range PHYs

## 4.1 Conducted Testing

The following table presents the following measurement results collected on real silicon with the PHYs available in the LR Profile:

- Receiver sensitivity corresponding to 1% packet error rate (PER)

- Overall required link (Rx+Tx) XO accuracy requirement calculated from frequency offset tolerances

**Table 3-1. LR PHY Parameters**

| Frequency Band<br>[MHz] | Data Rate<br>[kbps] | Measured Sensitivity<br>[dBm] | (TX + RX) XO Accuracy<br>[ppm +/-] |

|-------------------------|---------------------|-------------------------------|------------------------------------|

| 434/490                 | 1.2                 | -128                          | 2.5                                |

| 434/490                 | 2.4                 | -124.5                        | 5                                  |

| 434/490                 | 4.8                 | -122.5                        | 10                                 |

| 434/490                 | 9.6                 | -120.5                        | 20                                 |

| 434/490                 | 19.2                | -117                          | 40                                 |

| 868/915                 | 1.2                 | -128                          | 1.25                               |

| 868/915                 | 4.8                 | -120.5                        | 5                                  |

| 868/915                 | 9.6                 | -118                          | 10                                 |

| 868/915                 | 19.2                | -115                          | 20                                 |

| 868/915                 | 38.4                | -112                          | 40                                 |

| 868/915                 | 80                  | -107.5                        | 80                                 |

Full characterization is ongoing but based on the available results, CW blocking at 2 MHz / 10 MHz - with wanted signal at +3 dB above sensitivity - is expected to be -51 / -36 dBm, respectively, for the high bands and -53 / -37 dBm for the low bands.

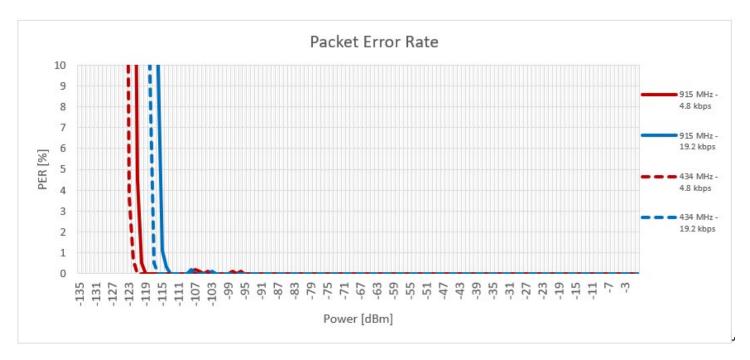

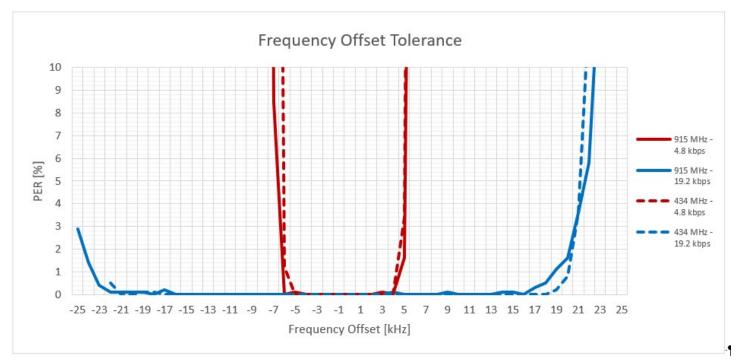

Packet error rate waterfall and frequency offset tolerance curves are provided in the following two figures for the 4.8 and 19.2 kbps PHYs in the 434 and 915 MHz bands.

Figure 4-1. LR PHY Packet Error Rate (PER) Waterfall Curves

Figure 4-2. LR PHY Frequency Offset Tolerance Measurement Results

In the figure above, signal is 3 dB above sensitivity level. TCXO – generator residual frequency offset was not compensated here.

www.silabs.com/loT

SW/HW www.silabs.com/simplicity

Quality www.silabs.com/quality

Support & Community www.silabs.com/community

## Disclaimer

Silicon Labs intends to provide customers with the latest, accurate, and in-depth documentation of all peripherals and modules available for system and software implementers using or intending to use the Silicon Labs products. Characterization data, available modules and peripherals, memory sizes and memory addresses refer to each specific device, and "Typical" parameters provided can and do vary in different applications. Application examples described herein are for illustrative purposes only. Silicon Labs reserves the right to make changes without further notice to the product information, specifications, and descriptions herein, and does not give warranties as to the accuracy or completeness of the included information. Without prior notification, Silicon Labs may update product firmware during the manufacturing process for security or reliability reasons. Such changes will not alter the specifications or the performance of the product. Silicon Labs shall have no liability for the consequences of use of the information supplied in this document. This document does not imply or expressly grant any license to design or fabricate any integrated circuits. The products are not designed or authorized to be used within any FDA Class III devices, applications for which FDA premarket approval is required, or Life Support Systems without the specific written consent of Silicon Labs. A "Life Support System" is any product or system intended to support or sustain life and/or health, which, if it fails, can be reasonably expected to result in significant personal injury or death. Silicon Labs products are not designed or authorized for military applications. Silicon Labs products shall under no circumstances be used in weapons of mass destruction including (but not limited to) nuclear, biological or chemical weapons, or missiles capable of delivering such weapons. Silicon Labs disclaims all express and implied warranties and shall not be responsible or liable for any injuries or damages related to use of a Silicon Labs

#### Trademark Information

Silicon Laboratories Inc.\*, Silicon Laboratories\*, Silicon Labs\*, SiLabs\* and the Silicon Labs logo\*, Bluegiga Logo\*, ClockBuilder\*, CMEMS\*, DSPLL\*, EFM\*, EFM32\*, EFR, Ember\*, Energy Micro, Energy Micro logo and combinations thereof, "the world's most energy friendly microcontrollers", Ember\*, EZLink\*, EZRadio\*, EZRadioPRO\*, Gecko\*, Gecko OS, Gecko OS Studio, ISOmodem\*, Precision32\*, ProSLIC\*, Simplicity Studio\*, SiPHY\*, Telegesis, the Telegesis Logo\*, USBXpress\*, Zentri, the Zentri logo and Zentri DMS, Z-Wave\*, and others are trademarks or registered trademarks of Silicon Labs. ARM, CORTEX, Cortex-M3 and THUMB are trademarks or registered trademarks of ARM Holdings. Keil is a registered trademark of ARM Limited. Wi-Fi is a registered trademark of the Wi-Fi Alliance. All other products or brand names mentioned herein are trademarks of their respective holders.