# UG574: SiWx917 SoC Manufacturing Utility User Guide

Version 1.3

November 2024

# **Table of Contents**

| 1 | Introduction  1.1 Manufacturing Procedure                                                                      | 4              |

|---|----------------------------------------------------------------------------------------------------------------|----------------|

|   | Manufacturing Utility     1.2.1 Simplicity Commander CLI     1.2.2 Manufacturing Utility Commands – Parameters | 6              |

| 2 | Flash Mode Selection – No In-Package Flash OPN                                                                 | 9              |

| 3 | Manufacturing Procedure - Without Security                                                                     | 10             |

|   | 3.1 Common Flash Mode                                                                                          | 10             |

|   | 3.2 Dual Flash Mode                                                                                            |                |

|   | 3.3 Example: SiWG917M111MGTBA (Common Flash Mode)                                                              |                |

| 4 | Security Features                                                                                              |                |

|   | 4.1 Secure Boot                                                                                                |                |

|   | 4.3 Secure Firmware Upgrade                                                                                    |                |

|   | 4.4 Debug Lock                                                                                                 |                |

| 5 | Manufacturing Procedure – With Security                                                                        | 16             |

| 5 | 5.1 Common Flash Mode                                                                                          |                |

|   | 5.2 Dual Flash Mode                                                                                            | 16             |

|   | 5.3 Security Key Programming                                                                                   | 18             |

|   | 5.3.1 Activation Code Generation for PUF                                                                       |                |

|   | 5.3.3 Generate Static Keys from Simplicity Commander                                                           |                |

|   | 5.3.4 Provisioning Static Keys                                                                                 | 19             |

|   | 5.4 MBR Programming to Enable Security Configurations                                                          |                |

|   | 5.4.1 Programmable Fields in MBR                                                                               |                |

|   | 5.4.3 Example JSON file with security parameters of MBR                                                        | 20             |

|   | 5.4.4 Programming MBR with security parameters                                                                 | 21             |

|   | 5.5 Enable Security Configurations in NWP and M4 Firmware Images                                               |                |

|   | 5.5.2 Secure M4 Image                                                                                          | 21             |

|   | 5.6 Example: SiWG917M111MGTBA (Common Flash Mode)                                                              | 22             |

|   | 5.7 Disable Security                                                                                           | 22             |

| 6 | Combined Image (NWP + M4)                                                                                      | 24             |

| 7 | Boot Configurations Update – eFuse                                                                             | 25             |

|   | 7.1 Read eFuse Data                                                                                            |                |

|   | 7.2 Write eFuse Data                                                                                           |                |

|   | 7.3 Possible Boot Configurations                                                                               |                |

| 8 | RF Calibration                                                                                                 |                |

|   | 8.1 Steps for CTUNE Adjustments                                                                                | 30             |

|   | 8.2 Steps for Gain Offset Adjustments                                                                          |                |

|   | 8.2.1 Example: SiWG917M111MGTBA – Gain Offset adjustment steps                                                 | 31             |

|   | 8.3 EVM Offset                                                                                                 | 31             |

| 9 | Manufacturing Utility - Commands                                                                               | 33             |

|   | 9.1 SiWG917 Info                                                                                               |                |

|   | 9.1.1 Manufacturing Info                                                                                       |                |

|   | 9.2 PSRAM Pinset Update                                                                                        |                |

|   | 9.2.1 Write TA MBR                                                                                             | 34             |

|   | 9.2.2 Write M4 MBR                                                                                             |                |

|   | 9.3 User Data – Update                                                                                         |                |

|   | 9.3.2 Read User Data                                                                                           | 34             |

|   | 9.3.3 Write User Data to a Location                                                                            | 34             |

|   | titt a t waaa liaawilada                                                                                       | 25             |

|   | 9.3.4 Erase User Data                                                                                          |                |

|   | 9.4 MAC Address – Update                                                                                       | 35             |

|   | 9.4 MAC Address – Update  9.4.1 Write to Flash  9.4.2 Write to eFuse                                           | 35<br>35<br>35 |

|   | 9.4 MAC Address – Update                                                                                       | 35<br>35<br>35 |

|    | 9.5.1 For Macronix Flash | 36 |

|----|--------------------------|----|

| 10 | Possible Error Codes     | 38 |

| 11 | Revision History         | 39 |

# 1 Introduction

This document describes the manufacturing procedure to be followed when procuring the SiWG917 (SiWx917 SoC) IC, based on the Ordering Part Number (OPN), flash mode, and security specifications.

The SiWG917 comprises two processors: Silicon Labs' Network Wireless Processor (NWP) and an ARM® Cortex® M4 Processor. The NWP subsystem is responsible for executing all networking and wireless stacks on independent threads and functions as the secure processing domain, overseeing secure boot, secure firmware updates, and debug lock. The Cortex-M4 processor is dedicated to peripheral and application-related processing

# 1.1 Manufacturing Procedure

Based on the OPN, the SiWG917 can be equipped with either 4 or 8 MB of "In-package" Quad SPI (QSPI) flash. Additionally, the SiWG917 supports external flash options of up to 16 MB¹. The QSPI serves as the interface for accessing the flash memory.

The SiWG917 operates in the following flash modes:

- · Common Flash A single flash memory is shared between the NWP and M4 processors.

- Dual Flash Independent flash memories are allocated for the NWP and M4 processors.

In case of no in-package flash OPNs, it is necessary to enable the flash mode of your choice, refer to the section Flash Mode Selection – No In-Package Flash OPN for the steps to select the appropriate flash mode.

For OPNs with 4 or 8 MB in-package flash, the default configuration is common flash mode. If you wish to configure the device in dual flash mode, refer to the section <u>Dual Flash Mode</u>.

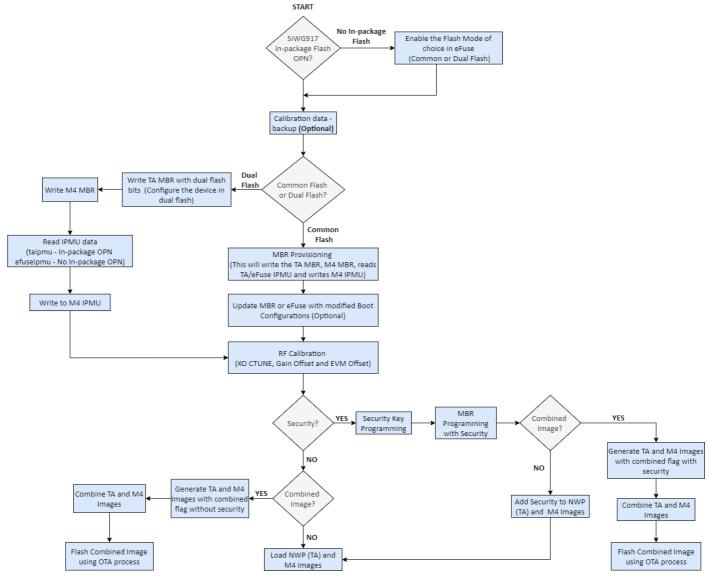

The following flow chart illustrates the SiWG917 manufacturing procedure.

<sup>&</sup>lt;sup>1</sup> External 16MB Flash is not supported by latest available SiWG917 MBR. For information regarding software roadmap features, lists of available features, and profiles, contact Silicon Labs or refer to document related to SiWG917 MBR (Release Notes and Reference Manuals).

Figure 1.1: Manufacturing Procedure Flow of SiWx917

# Verify the Flash Mode

Check whether the SiWG917 is in common Flash mode or Dual Flash mode.

# Master Boot Record (MBR) configuration based on OPN

MBR is stored in flash and contains information such as clock frequencies, offsets of structures like device specific configurations, SPI configurations, external flash details, and so on.

#### Enable security

The security fields in the MBR, PUF activation code, key descriptors, and the keys must be programmed

in the device while enabling the security features.

#### RF Calibration (Frequency and Gain Offset)

The Crystal Oscillator Capacitor tune (XO CTUNE) is used to adjust frequency, gain offset adjustments can be done in burst, continuous and continuous wave mode in the SiWG917 using the manufacturing utility.

# 1.2 Manufacturing Utility

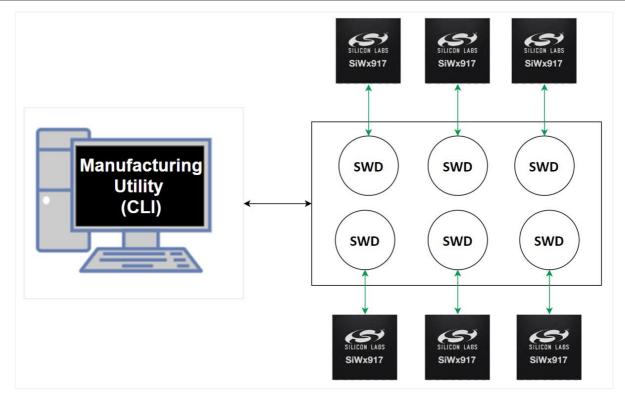

The **Manufacturing Utility** operates in conjunction with Simplicity Commander via Command Line Interface (CLI). The CLI facilitates interaction with the commander to execute the manufacturing procedure. Multiple instances of the commander can support multiple devices, enabling simultaneous programming of production information into the SiWG917.

Figure 1.2: Manufacturing Utility

# 1.2.1 Simplicity Commander CLI

There are two methods to access the Simplicity Commander CLI.

- Simplicity Commander (as part of tools in Simplicity Studio)

- Simplicity Commander (individually installed)

**Note:** When configuring the SiWG917, you must use the latest version of <u>simplicity commander</u>. In contrast not doing so might result the device to act in an unexpected manner.

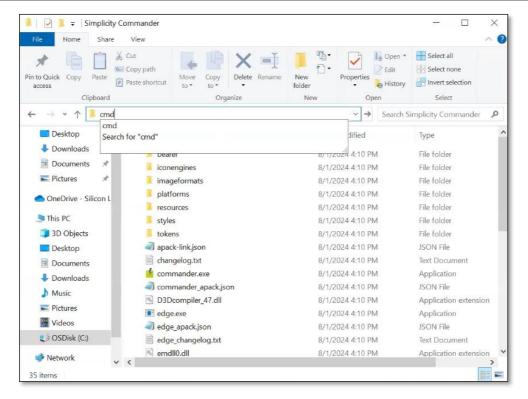

Enter "cmd" in the Simplicity Commander Installed path to open the commander CLI.

Example: For Simplicity Commander (As part of tools in Simplicity Studio) – Go to the path:

\$:\...\SimplicityStudio\v5\developer\adapter\_packs\commander and type 'cmd' in the address bar and press Enter key.

Figure 1.3: Simplicity Commander CLI

# 1.2.2 Manufacturing Utility Commands - Parameters

The following table lists the various parameters that are used by the commands mentioned in the subsequent sections.

| Field                                               | Description                                                                                                                                                                                                                                                                                           |                       |                                               |  |  |

|-----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-----------------------------------------------|--|--|

| provision                                           | Writes TA MBR, M4 MBR, Reads, and Writes M4 IPMU in Common flash mode                                                                                                                                                                                                                                 |                       |                                               |  |  |

| write                                               | Compares the provided MBR file in the command and the MBR file already present inside the device and writes the new changes into the MBR                                                                                                                                                              |                       |                                               |  |  |

| read                                                | Read the conten                                                                                                                                                                                                                                                                                       | nts                   |                                               |  |  |

| init                                                | Generate the ac                                                                                                                                                                                                                                                                                       | tivation code         |                                               |  |  |

| mbr                                                 | Master Boot Red                                                                                                                                                                                                                                                                                       | cord                  |                                               |  |  |

| keys                                                | Security keys                                                                                                                                                                                                                                                                                         |                       |                                               |  |  |

| m4mbrcf                                             | Common flash N                                                                                                                                                                                                                                                                                        | //4 MBR               |                                               |  |  |

| m4mbrdf                                             | Dual flash M4 M                                                                                                                                                                                                                                                                                       | BR                    |                                               |  |  |

| m4ipmucf                                            | M4 IPMU data for common flash configuration                                                                                                                                                                                                                                                           |                       |                                               |  |  |

| m4ipmudf                                            | M4 IPMU data fo                                                                                                                                                                                                                                                                                       | or dual flash cor     | nfiguration                                   |  |  |

| efusecopy                                           | Updating eFuse data to flash for selected region                                                                                                                                                                                                                                                      |                       |                                               |  |  |

| <full opn=""></full>                                | Provide the <b>OPN</b> number. Example: SiWG917M111MGTBA                                                                                                                                                                                                                                              |                       |                                               |  |  |

| <updated-mbr-fields.json></updated-mbr-fields.json> | File in which security level is programmed                                                                                                                                                                                                                                                            |                       |                                               |  |  |

| -d                                                  | Device                                                                                                                                                                                                                                                                                                |                       |                                               |  |  |

| skipload                                            | Skip loading manufacturing firmware (loaded by the commander CLI in the device RAM, when the first command is given from the CLI) when the command is given.  Note: Make sure the first command given to the device using commander CLI does not have theskipload each time the device is powered ON. |                       |                                               |  |  |

| pinset [n]                                          | Should be given mode)  Pinset no [n]  0                                                                                                                                                                                                                                                               | GPIO set  GPIO 0 to 5 | ge flash and in-package flash OPN (dual flash |  |  |

|               | 2                                                                                                            | GPIO 46 to 51                   |     |  |  |

|---------------|--------------------------------------------------------------------------------------------------------------|---------------------------------|-----|--|--|

|               | 3                                                                                                            | GPIO 52 to 57                   |     |  |  |

| start         | Turn on the rad                                                                                              | Turn on the radio transmission  |     |  |  |

| stop          | Turn off the rad                                                                                             | Turn off the radio transmission |     |  |  |

| noburst       | Transmission happens continuously instead of being in bursts                                                 |                                 |     |  |  |

| internalant   | Select virtual internal RF switch. By default, the external antenna RF switch configuration is selected.     |                                 |     |  |  |

| ctuneoverride | It writes the XO CTUNE value into the flash instead of adding the frequency offset to already present value. |                                 |     |  |  |

| store         | Computed values are stored in flash                                                                          |                                 |     |  |  |

| storeinefuse  | Compute value                                                                                                | s are stored in eF              | use |  |  |

**Table 1.1: Manufacturing Utility Commands - Parameters**

# 2 Flash Mode Selection – No In-Package Flash OPN

The following table lists the steps involved in enabling either common flash or dual flash mode in the eFuse (One Time Programmable) in a no in-package flash SiWG917 OPN.

**Note:** Once the Common flash or Dual flash mode is selected in the eFuse by following the processes outlined here, it is irreversible.

| Steps | Description                                                                       |                 | Command (Syntax)                                                                                                                                                 |  |  |

|-------|-----------------------------------------------------------------------------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1     | Read the present contents of the eFuse to an efuse_value.json file                |                 | commander manufacturing read efuseout efuse_value.json -d SiWG917M1xxXGTBA                                                                                       |  |  |

|       | Enable Flash mode<br>(Common or Dual<br>Flash)                                    | Common<br>Flash | Open the efuse_value.json file (created in step 1) "common_flash_enabled" and set to 1                                                                           |  |  |

| 2     |                                                                                   | Dual Flash      | Open the efuse_value.json file (created in step 1) Following are listed:  • "m4_flash_address_width" and set to 2  • "m4_flash_address_width_valid" and set to 1 |  |  |

| 3     | Dry run and check the correct bit is set in the eFuse (Optional, but recommended) |                 | commander manufacturing write efusedata efuse_value.json -d SiWG917M1xxXGTBA -dryrun                                                                             |  |  |

| 4     | Burn the bits in the eFuse                                                        |                 | commander manufacturing write efusedata efuse_value.json -d SiWG917M1xxXGTBA                                                                                     |  |  |

| 5     | Read back the contents of the eFuse                                               |                 | commander manufacturing read efuseproperty m4_and_security_config -d SiWG917M1xxXGTBA                                                                            |  |  |

Table 2.1: Flash Mode Selection (No In-Package Flash OPN)

The preceding steps are for selecting the flash mode only. You must complete the following sections <u>Manufacturing Procedure – Without Security</u>, and <u>Manufacturing Procedure – With Security</u> as per your requirement.

# 3 Manufacturing Procedure – Without Security

This section outlines the sequence for programming devices without security.

Before proceeding with the following steps for Common flash or Dual flash mode, ensure that the flash mode is selected (<u>Flash Mode Selection – No In-Package Flash OPN</u>) for no in-package flash OPN.

**Note:** This section contains two manufacturing sequence of steps for both Common Flash Mode and Dual Flash Mode. Depending on the user's configuration, only one of these sections needs to be followed

# 3.1 Common Flash Mode

The following sequence needs to be followed for manufacturing procedure without security in common flash mode.

| Steps | Description                                    | Command (Syntax)                                                                                                                                                                                                                                               |

|-------|------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | Backup – IPMU Calibration data                 | commander manufacturing read <efuseipmu taipmu>out <filename.bin> -d <opn number=""> [pinset n]</opn></filename.bin></efuseipmu taipmu>                                                                                                                        |

| 2     | MBR Provisioning                               | <pre>commander manufacturing provision -mbr <filename.bin default> -d <opn number=""> [skipload] [ pinset n]</opn></filename.bin default></pre>                                                                                                                |

| 3     | Boot Configurations Update in eFuse (Optional) | Refer to the section Boot Configurations Update – eFuse                                                                                                                                                                                                        |

| 4     | RF (Frequency and Gain<br>Offset) Calibration  | Refer to section RF Calibration for calibration steps.                                                                                                                                                                                                         |

| 5     | Load NWP and M4<br>Firmware Images             | commander rps load <filename.rps> -d <opn number="">  Note: If you want to load a combined image (NWP +M4) instead of individual NWP and M4 images, refer to the section Combined Image (NWP + M4) for combined image related information</opn></filename.rps> |

Table 3.1: Common Flash Mode (Without Security)

# 3.2 Dual Flash Mode

The following sequence must be followed for the manufacturing procedure without security in dual flash mode.

To configure devices with an in-package flash to dual flash mode, user must set the dual flash bits in the TA MBR (see <u>dual\_flash.json</u> file).

#### Note:

- For dual flash mode and no in-package flash devices you must mention the [--pinset n] in the

manufacturing commands.

- Flash pinset is as below for SiWG917

| Flash Pinset no | GPIO set      |

|-----------------|---------------|

| 0               | GPIO 0 to 5   |

| 2               | GPIO 46 to 51 |

| 3               | GPIO 52 to 57 |

| Step                                                                                                        | Description                                                             | Command (Syntax)                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1                                                                                                           | Backup – IPMU Calibration data                                          | <pre>commander manufacturing read <efuseipmu taipmu>out <filename.bin> -d <opn number=""> [pinset n]</opn></filename.bin></efuseipmu taipmu></pre>                                                                                                                                                                                       |  |  |

| 2                                                                                                           | Write NWP MBR with dual flash bits enabled (using dual_flash.json file) | <ol> <li>commander manufacturing write tambr -data <filename.bin> -d <opn number=""> [skipload] [pinset n]</opn></filename.bin></li> <li>commander manufacturing write tambr -data dual flash.json -d <opn number=""> [skipload] [pinset n]</opn></li> </ol>                                                                             |  |  |

| 3                                                                                                           | Write M4 MBR                                                            | commander manufacturing write m4mbrdf –data<br><filename.bin filename.json> -d <opn number=""> [skipload]<br/>[pinset n]</opn></filename.bin filename.json>                                                                                                                                                                              |  |  |

| 4                                                                                                           | Write IPMU calibration data to M4                                       | Read IPMU (taipmu - In-package flash OPN, efuseipmu - No In-package flash OPN)  1. commander manufacturing read <taipmu efuseipmu> out <filename.bin> Write M4 IPMU  2. commander manufacturing write <m4ipmucf m4ipmudf> data <filename.bin> [skipload] [pinset n]</filename.bin></m4ipmucf m4ipmudf></filename.bin></taipmu efuseipmu> |  |  |

| 5                                                                                                           | Boot Configurations Update in eFuse (Optional)                          | Refer to the section <u>Boot Configurations Update – eFuse</u>                                                                                                                                                                                                                                                                           |  |  |

| 6                                                                                                           | RF (Frequency and Gain<br>Offset) Calibration                           | Refer to section RF Calibration for calibration steps.                                                                                                                                                                                                                                                                                   |  |  |

| 7 Load NWP and M4 Firmware Images  Note: If you want to load a combined individual NWP and M4 images, refer |                                                                         | commander rps load <filename.rps> -d <opn number="">  Note: If you want to load a combined image (NWP +M4) instead of individual NWP and M4 images, refer to the section Combined Image (NWP + M4) for combined image related information</opn></filename.rps>                                                                           |  |  |

**Table 3.2: Dual Flash Mode (Without Security)**

# 3.3 Example: SiWG917M111MGTBA (Common Flash Mode)

The manufacturing procedure without security for SiWG917M111MGTBA OPN in common flash mode is as follows.

- 1. Backup IPMU Calibration

- o commander manufacturing read taipmu --out filename.bin -d SiWG917M111MGTBA

- 2. MBR Provisioning

- o commander manufacturing provision -mbr default -d SiWG917M111MGTBA

- 3. RF Calibration refer to section RF Calibration

- 4. Load NWP and M4 Images

- o NWP Image

- commander rps load SiWG917-B.2.12.2.1.0.9.rps -d SiWG917M111MGTBA

- M4 Image commander rps load si91x\_hello\_world.rps -d SiWG917M111MGTBA

Note: If no MBR is present in the device, you will see 0xa0ac error.

# 4 Security Features

The following sections provide information on enabling SiWG917 security features using the manufacturing utility, (Simplicity Commander CLI).

# 4.1 Secure Boot

Secure Boot is a feature designed to ensure that only authenticated code can run on the chip. If a device fails its security check, it is not permitted to run, and program control will typically stall in the validating module. SiWG917 possess two bootloaders: the Security Bootloader, and the Application Bootloader.

The Security Bootloader runs on the NWP, while the Application Bootloader runs on the Cortex M4 processor. **Secure Boot is implemented within the Security Bootloader.**

The Secure Boot process is as follows:

- 1. The Security Bootloader authenticates the MBR in the flash.

- 2. The Security Bootloader validates the integrity and authenticity of the firmware (NWP and M4) in the flash and subsequently invokes the Application Bootloader.

For enabling only Secure Boot or Secure Boot along with other security features, refer to the Security Levels section.

# 4.2 Secure Key Management and Protection

Inject custom public and private keys and other custom secret keys on the chips during manufacturing – safeguard your keys right from the beginning of their lifecycle.

Physically Unclonable Function (PUF) derived intrinsic keys are shown in the following table. These keys are unique per device and are generated randomly when the PUF is initialized.

| Key                         | Description                                                                                                                                                                 |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Master Key                  | This key is used for MIC calculation and wrapping/ unwrapping of TA keys. Keys encrypted using Master Key is done using AES ECB Mode. MIC is calculated using AES CBC mode. |

| Unwrap Key                  | This key is used for MIC calculation and wrapping/ unwrapping of M4 keys. Keys encrypted using Unwrap Key is done using AES ECB Mode. MIC is calculated using AES CBC mode  |

| TA FW key 1,<br>TA FW key 2 | These two keys are being used for encryption and inline decryption of TA firmware in CTR or XTS mode based on configuration from security configs of EFUSE                  |

| M4 FW key 1,<br>M4 FW key 2 | These two keys are being used for encryption and inline decryption of M4 firmware in CTR or XTS mode based on configuration from security configs of EFUSE                  |

Table 4.1: PUF Derived Intrinsic Keys

Keys generated by Simplicity Commander and stored on the device are as follows.

| Key                  | Description                                                                                                                                     |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| OTP Symmetric<br>Key | Used for flash content's (MIC) verification - AES CBC is used for calculation of the MIC value.                                                 |

| OTP Public Key       | Used for flash content's (digital signature) verification (ECDSA-P256). This key is used to verify the signature of MBR                         |

| TA Public Key*       | Used for TA firmware signature verification (ECDSA-P256) – by the security bootloader. This key will be wrapped with PUF derived intrinsic keys |

| TA OTA Key*                | Used for TA firmware image encryption and MIC calculation of TA Firmware. This key will be wrapped with PUF derived intrinsic keys            |

|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| M4 OTA Key*                | Used for M4 firmware image encryption and MIC calculation of M4 firmware. This key will be wrapped with PUF derived intrinsic keys            |

| M4 Public Key*             | Used for M4 firmware signature verification (ECDSA-P256) by the security bootloader. This key will be wrapped with PUF derived intrinsic keys |

| Attestation<br>Private Key | Used for signing secure attestation tokens(ECDSA-P256). This key will be wrapped with PUF derived intrinsic keys                              |

Table 4.2: Keys Generated by Simplicity Commander

For information on how to generate the keys at commander, refer to <u>Generate Static Keys from Simplicity</u> <u>Commander.</u> For PUF activation, refer to <u>Activation Code Generation for PUF</u> and to generate intrinsic keys and load the keys, refer to <u>Provisioning Static Keys</u>.

The following table lists the Key type, Key storage requirements, and Storage type.

|      |                            | Key Storage                                                  | Algorith |                                   |                                                         | Stora | age   |

|------|----------------------------|--------------------------------------------------------------|----------|-----------------------------------|---------------------------------------------------------|-------|-------|

| S.No | Key                        | Requirements                                                 | m        | Operation                         | Modes                                                   | NWP   | NWP   |

|      |                            |                                                              |          |                                   |                                                         | eFuse | Flash |

| 1    | OTP<br>Symmetric<br>Key    | 16 bytes                                                     | AES      | MIC<br>Calculation                | AES-CMAC                                                | >     | _     |

| 2    | OTP Public<br>Key          | 91 bytes - NIST<br>Curve P-256                               | ECDSA    | Sign<br>verification              | _                                                       | >     |       |

| 3    | TA Public<br>Key           | 96 bytes* - NIST<br>Curve P-256                              | ECDSA    | Sign<br>verification              | -                                                       | ı     | ~     |

| 4    | TA OTA Key                 | 32 bytes                                                     | AES      | Encryption,<br>MIC<br>Calculation | Encryption: AES-<br>ECB<br>MIC Calculation:<br>AES-CMAC | 1     | ~     |

| 5    | M4 OTA Key                 | 32 bytes                                                     | AES      | Encryption,<br>MIC<br>Calculation | Encryption: AES-<br>ECB<br>MIC Calculation:<br>AES-CMAC | -     | ~     |

| 6    | M4 Public<br>key           | 96 bytes* - NIST<br>Curve P-256                              | ECDSA    | Sign<br>verification              | _                                                       | -     | ~     |

| 7    | Attestation<br>Private Key | 240 Bytes* - NIST<br>Curve P-256                             | ECDSA    | Sign                              | _                                                       | -     | ~     |

| 8    | Master Key                 | 52 bytes key code<br>used to initialize<br>key in Key Holder | AES      | Encryption,<br>MIC<br>Calculation | Encryption: AES-<br>ECB<br>MIC Calculation:<br>AES-CMAC | -     | ~     |

| 9    | Unwrap Key                 | 52 bytes key code<br>used to initialize<br>key in Key Holder | AES      | Encryption                        | Encryption: AES-<br>ECB<br>MIC Calculation:<br>AES-CMAC | ı     | ~     |

| 10   | TA FW Key<br>(2 keys)      | 52 bytes key code<br>used to initialize<br>key in Key Holder | AES      | Encryption                        | AES CTR, AES XTS                                        | _     | ~     |

| 11   | M4 FW Key<br>(2 keys)      | 52 bytes key code<br>used to initialize<br>key in Key Holder | AES      | Encryption                        | AES CTR, AES XTS                                        | _     | ~     |

Table 4.3: Keys Type, Storage Requirements and Storage Type

<sup>\*</sup> Note: These keys are referred to as "static keys" in this document.

Note: In the preceding table \* signifies:

- For TA and M4 Public key actual key size is 91 bytes, remaining 5 padding bytes added to make key size multiple of 16 for AES encryption.

- For Attestation key also, actual key size is 227 bytes.

- All keys stored in flash will be appended with MIC and other metadata that is not reflected in the table.

# 4.3 Secure Firmware Upgrade

The secure firmware update feature of the bootloader checks the authenticity of the new firmware image along with its integrity. The bootloader updates the image only after successfully validating the authenticity and integrity of the image. It prevents downgrade to a lower version of firmware using the anti-rollback feature if it is enabled.

The bootloader also supports transparent migration to a wirelessly updated image and protection against failures by providing recovery mechanisms.

The security bootloader uses a proprietary format for its upgrade images, called RPS. These files have extension ". rps".

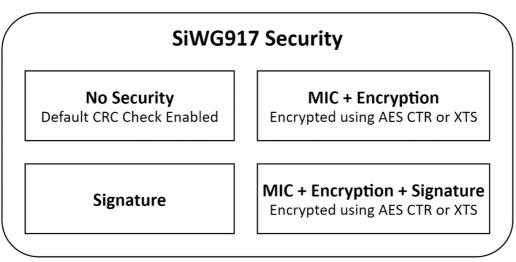

Table 4.1: SiWG917 Firmware Image Security

The firmware image for both NWP and M4 supports the following parameters:

- No Security: Default CRC of the image within the RPS header.

- Message Integrity Check (MIC) + Encryption: The MIC is calculated for the whole plain image and saved within the RPS header. The image is encrypted and appended to the RPS header. The image can be encrypted using AES CTR or XTS mode.

- Signature: The whole RPS file's (RPS Header+ image) signature is calculated and appended to the end of the file.

- MIC + Encryption + Signature: The MIC is calculated for the whole plain image and saved within the RPS header. The image is encrypted and appended to the RPS header. The image can be encrypted using AES CTR or XTS mode. Finally, the whole RPS file's (RPS Header+ image) signature is calculated and appended to the end of the file.

To understand how to select the security level of your choice refer to Security Levels section.

To enable security for NWP and M4 images refer to <u>Enable Security Configurations in NWP and M4 Firmware Images</u>.

# 4.4 Debug Lock

Configure the debug port securely before the chips leave the factory with the Debug Lock Feature (which can be unlocked with a token)

The SiWG917 has a hardware debug solution. This provides high system visibility of the processor and memory through either a traditional JTAG port or a 2-pin Serial Wire Debug (SWD) port that is ideal for microcontrollers and other small package devices. The Secure Lock Feature locks the Debug Port. Any unauthorized access will be restricted.

This will be a one-time update of the MBR, however. This update should happen when the user has completed the development phase and entered the manufacturing phase for their products. Locking the NWP and M4 debug ports is a necessary step in production to prevent unauthorized access to sensitive information. Refer to the <a href="https://example.com/AN1428:">AN1428:</a> SiWx917 Debug Lock for more information on enabling debug lock.

# 5 Manufacturing Procedure – With Security

The following steps show the manufacturing procedure to enable security configurations.

For devices with no in-package flash, ensure the flash mode is selected (<u>Flash Mode Selection – No In-Package Flash OPN</u>) before proceeding with the following steps for common flash or dual flash mode.

**Note:** This section contains two manufacturing sequence of steps for both Common Flash Mode and Dual Flash Mode. Depending on the user's configuration, only one of these sections needs to be followed

## 5.1 Common Flash Mode

The following sequence needs to be followed to enable security configurations in common flash mode during manufacturing.

| Step | Description                                                  | Command (Syntax)                                                                                                                                                                                                                                                |  |  |  |

|------|--------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | Backup – IPMU Calibration data                               | commander manufacturing read <efuseipmu taipmu>out <filename.bin> -d <opn number=""> [pinset n]</opn></filename.bin></efuseipmu taipmu>                                                                                                                         |  |  |  |

| 2    | MBR Provisioning                                             | <pre>commander manufacturing provisionmbr      <filename.bin default> -d <opn number=""> [skipload]      [pinset n]</opn></filename.bin default></pre>                                                                                                          |  |  |  |

| 3    | Security Key Programming                                     | Refer to section Security Key Programming.                                                                                                                                                                                                                      |  |  |  |

| 4    | MBR Programming to Enable Security Configurations            | Refer to section MBR Programming to Enable Security Configurations.                                                                                                                                                                                             |  |  |  |

| 5    | Boot Configurations Update in eFuse (Optional)               | Refer to the section <u>Boot Configurations Update – eFuse.</u>                                                                                                                                                                                                 |  |  |  |

| 6    | RF (Frequency and Gain Offset)<br>Calibration                | Refer to section RF Calibration for calibration steps.                                                                                                                                                                                                          |  |  |  |

| 7    | Enable Security Configurations in NWP and M4 Firmware Images | Refer to section Enable Security Configurations in NWP and M4 Firmware Images.                                                                                                                                                                                  |  |  |  |

| 8    | Load NWP and M4 Firmware Images                              | commander rps load <filename.rps> -d <opn number="">  Note: If you want to load a combined image (NWP +M4) instead of individual NWP and M4 images, refer to the section Combined Image (NWP + M4) for combined image related information.</opn></filename.rps> |  |  |  |

| 9    | Debug Lock (Optional, but<br>Recommended)                    | Refer to the section Debug Lock.                                                                                                                                                                                                                                |  |  |  |

Table 5.1: Common Flash Mode (With Security)

**Note:** The security configurations of firmware images must match the security configurations on the device, that is MIC, signature and encrypted XiP. A mismatch can lead to firmware execution failure.

# 5.2 Dual Flash Mode

To configure devices with an in-package flash to dual flash mode, user must set the dual flash bits in the TA MBR (refer to <a href="mailto:dual\_flash.json">dual\_flash.json</a> file).

#### Note:

- For dual flash mode and no in-package flash devices you must mention the [--pinset n] in the manufacturing commands.

- Following are the Flash pinset for the SiWG917.

| Flash Pinset no | GPIO set      |

|-----------------|---------------|

| 0               | GPIO 0 to 5   |

| 2               | GPIO 46 to 51 |

| 3               | GPIO 52 to 57 |

The following sequence needs to be followed to enable security configurations in dual flash mode during manufacturing.

| Step | Description                                                  | Command (Syntax)                                                                                                                                                                                                                                                                                                                         |  |  |  |

|------|--------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1    | Backup – IPMU Calibration data                               | <pre>commander manufacturing read <efuseipmu taipmu>out <filename.bin> -d <opn number=""> [pinset n]</opn></filename.bin></efuseipmu taipmu></pre>                                                                                                                                                                                       |  |  |  |

| 2    | Write NWP MBR with dual flash bits enabled                   | <ol> <li>commander manufacturing write tambr -data <filename.bin> -d <opn number=""> [skipload] [pinset n]</opn></filename.bin></li> <li>commander manufacturing write tambrdata dual flash.json -d <opn number=""> [skipload] [pinset n]</opn></li> </ol>                                                                               |  |  |  |

| 3    | Write M4 MBR                                                 | commander manufacturing write m4mbrdfdata<br><filename.bin filename.json> -d <opn number=""> [skipload]<br/>[pinset n]</opn></filename.bin filename.json>                                                                                                                                                                                |  |  |  |

| 4    | Write IPMU calibration data to M4                            | Read IPMU (taipmu - In-package flash OPN, efuseipmu - no In-package flash OPN)  1. commander manufacturing read <taipmu efuseipmu> out <filename.bin> Write M4 IPMU  2. commander manufacturing write <m4ipmucf m4ipmudf> data <filename.bin> [skipload] [pinset n]</filename.bin></m4ipmucf m4ipmudf></filename.bin></taipmu efuseipmu> |  |  |  |

| 5    | Security Key Programming                                     | Refer to section Security Key Programming.                                                                                                                                                                                                                                                                                               |  |  |  |

| 6    | MBR Programming to<br>Enable Security<br>Configurations      | Refer to section MBR Programming to Enable Security Configurations.                                                                                                                                                                                                                                                                      |  |  |  |

| 7    | Boot Configurations Update in eFuse (Optional)               | Refer to the section Boot Configurations Update – eFuse.                                                                                                                                                                                                                                                                                 |  |  |  |

| 8    | RF (Frequency and Gain<br>Offset) Calibration                | Refer to section RF Calibration for calibration steps.                                                                                                                                                                                                                                                                                   |  |  |  |

| 9    | Enable Security Configurations in NWP and M4 Firmware Images | Refer to section Enable Security Configurations in NWP and M4 Firmware Images.                                                                                                                                                                                                                                                           |  |  |  |

| 10   | Load NWP and M4<br>Firmware Images                           | commander rps load <filename.rps> -d <opn number="">  Note: If you want to load a combined image (NWP + M4) instead of individual NWP and M4 images, refer to the section Combined Image (NWP + M4) for combined image related information.</opn></filename.rps>                                                                         |  |  |  |

Debug Lock (Optional, but Recommended)

Refer to the section Debug Lock.

Table 5.2: Dual Flash Mode (With Security)

**Note:** The security configurations of firmware images should align with the security configurations on the device, such as MIC, signature, and encrypted XiP. A discrepancy may result in a failure of firmware execution.

# 5.3 Security Key Programming

This part of manufacturing includes generation of static keys, and Physically Unclonable Function (PUF) derived intrinsic keys. This section includes instructions to provision the keys into flash. While programming the static keys, the keys are saved in wrapped format in the flash. There are multiple keys that are generated inside and outside of device. Refer to Secure Key Management and Protection section for information on keys generated by simplicity commander and PUF derived intrinsic keys.

Following is the procedure for provision keys.

- 1. Activation code generation only for PUF

- 2. Power cycle the device to boot again after step 1

- 3. Generate static keys using simplicity commander

- 4. Provisioning static keys

#### 5.3.1 Activation Code Generation for PUF

This command is used to generate an activation code from the PUF module present in SiWG917 device. Once generated, the firmware writes this activation code into NWP flash. The activation code is used as a seed to initialize the PUF.

# Syntax:

commander manufacturing init --mbr <filename.bin|default> -d <full opn> [--skipload] [-pinset n]

#### **Return Code**

- Success 0xa05a

- In case of Failure Refer to <u>Possible Error Codes</u> and try again.

# 5.3.2 Power Cycle the device

You must power cycle the device after the activation code generation and flash completion to successfully initialize the PUF and store the PUF derived intrinsic keys. This is a mandatory step.

# 5.3.3 Generate Static Keys from Simplicity Commander

These keys are generated by simplicity commander. The key generation will produce a json file containing the Static Keys. For asymmetric keys, both public and private keys are written to the JSON file.

#### Syntax:

commander util genkeyconfig --outfile <keys.json> -d <full opn>

# **Return Code**

- Success 0xa05a

- In case of Failure Refer to <u>Possible Error Codes</u> and try again

# 5.3.4 Provisioning Static Keys

This step performs the actual provisioning of the static keys. This command instructs the initialized PUF to derive intrinsic keys and store them in NWP flash as a key code.

#### Syntax:

commander manufacturing provision --keys <keys.json> -d <full opn> [--skipload]

[--pinset n]

Note: keys.json file contains the static keys i.e. TA OTA key, M4 OTA key, TA public key, M4 public key and attestation key.

# 5.4 MBR Programming to Enable Security Configurations

By default, SiWG917 devices does not have security features enabled. The MBR and eFuse configurations of the device have all security features set to disable state. This means the PUF is not enabled, the activation code for the PUF is not programmed, and neither keys nor key descriptors are programmed.

# 5.4.1 Programmable Fields in MBR

The following table lists the relevant features in the MBR which can be programmed. The MBR fields are present in two structures efuse data and mbr within the MBR.

| Feature                                                                 | Structure  | MBR Field                                              |

|-------------------------------------------------------------------------|------------|--------------------------------------------------------|

| To enable TA MIC and encryption                                         | efuse_data | ta_secure_boot_enable = 1;                             |

| To enable M4 MIC and encryption                                         | efuse_data | m4_secure_boot_enable = 1;                             |

| To enable TA Signature                                                  | efuse_data | ta_digital_signature_validation = 1;                   |

| To enable M4 Signature                                                  | efuse_data | m4_digital_signature_validation = 1;                   |

| To enable TA inline encryption                                          | efuse_data | ta_encrypt_firmware = 1; (1 for CTR, 2 for XTS mode)   |

| To enable M4 inline encryption                                          | efuse_data | m4_encrypt_firmware = 1;                               |

| To select M4 firmware encryption mode                                   | efuse_data | m4_fw_encryption_mode = 1; (1 for CTR, 2 for XTS mode) |

| Start address of the sector where the PUF Activation code must be saved | mbr        | puf_activation_code_addr = 0x2000;                     |

# Table 5.3: MBR Fields - Features

- The security fields in MBR, PUF Activation code, Key descriptors, and the Keys are to be programmed in the

device in order to enable the security configurations in the device.

- The preceding features mentioned can also be configured in eFuse, but it will be irreversible. For other boot

configurations that can be configured in MBR, refer to the section <u>Possible Boot Configurations</u>.

## 5.4.2 Security Levels

There are three different security levels available. The levels are defined to make the security configurations easier for the user. It is important to note that these levels are not security configurations in themselves – they are a grouping of available security features to help users decide based on their security requirements.

- 1. Security Level 1 or Low Security Level

- 2. Security Level 2 or Partial Security Level

- 3. Security Level 3 or Full Security Level

#### 5.4.2.1 Security Level 1 (Low Security)

If you want to configure only Message Integrity Check (MIC) while enabling secure boot, the configurations in this level should be considered. This security level enables the bootloader to carry out the MIC of the firmware image

during firmware loading and firmware update. In this configuration, the firmware update process is faster compared to other security levels, the bootup time is faster, and the firmware execution is also faster.

This configuration is selected using the following fields:

```

"efuse_data": {

"ta_secure_boot_enable": 1,

"m4_secure_boot_enable": 1

}

```

# 5.4.2.2 Security Level 2 (Partial Security)

If you want to add signature check of firmware image along with MIC while enabling secure boot, the configurations in this level should be considered. This security level enables the bootloader to carry out the MIC and signature validation of the firmware image during firmware loading and firmware update.

In this level, the firmware update process will be slower than Security Level 1; the bootup time will be relatively slower than the Security Level 1, and the firmware execution speed will be same as Security Level 1.

This configuration is selected using the below fields:

```

"efuse_data": {

"ta_secure_boot_enable": 1,

"ta_digital_signature_validation": 1,

"m4_secure_boot_enable": 1,

"m4_digital_signature_validation": 1

}

```

# 5.4.2.3 Security Level 3 (Full Security)

If you want to enable secure boot with MIC, signature check, and inline encryption, the configurations in this level should be considered. The configurations in this security level enables the bootloader to perform the MIC, signature validation and decryption of the firmware image while loading and updating firmware. Additionally, it enables encrypted execute-in-place(XiP) while saving the firmware in the flash.

In this configuration, the firmware update process is slow, the bootup time is high, and the firmware execution is slow compared to security levels 1 and 2.

This configuration is selected using the following fields:

# 5.4.3 Example JSON file with security parameters of MBR

The following example shows the structure and the available fields:

```

{

"puf_activation_code_addr": 8192,

"efuse_data": {

"m4_digital_signature_validation": 1,

"m4_encrypt_firmware": 1,

"m4_fw_encryption_mode": 1,

"m4_secure_boot_enable": 1,

"ta_digital_signature_validation": 1,

"ta_encrypt_firmware": 1,

"ta_secure_boot_enable": 1

},

}

```

You should create a JSON file using the preceding fields shown and configure it based on their security requirements and by referring to <a href="Security Levels">Security Levels</a> section. The following section refers to this JSON file as <a href="Updated-mbr-fields.json">Updated-mbr-fields.json</a> file

# 5.4.4 Programming MBR with security parameters

The security configurations enabled based on the security level chosen should be placed in a **.json** file. Refer to the example JSON file in the section Example JSON file with security parameters of MBR.

Use the following command to update the MBR with the desired security configurations. Once this command is issued, it updates the existing MBR with updated-mbr-fields.json file parameters

```

Syntax:

commander manufacturing provision --mbr <filename.bin|default> --data <updated-mbr-

fields.json> -d <full opn> [--skipload] [--pinset n]

```

#### **Example**

commander manufacturing provision --mbr ta\_mbr\_SiWG917M111MGTBA.bin --data updated-mbr-fields.json -d SiWG917M111MGTBA

• The updated-mbr-fields.json file provided should be updated by the user with desired security levels as mentioned in Security Levels section

# 5.5 Enable Security Configurations in NWP and M4 Firmware Images

When the security configurations are enabled, the device expects the NWP and the M4 firmware image files also to have the same configurations enabled. If you try to flash the mismatched security configurations, the bootloader returns an error.

The keys generated in the section <u>Generate Static Keys from Simplicity Commander</u> are used here to secure NWP and M4 images

#### 5.5.1 Secure NWP Image

The following command is to secure the NWP firmware image.

```

Syntax:

commander rps convert <filename.rps> --taapp <original non-encrypted TA rps> --mic <keys.json> --encrypt <keys.json> --sign <keys.json>

```

# 5.5.2 Secure M4 Image

The following command is to secure the M4 firmware image.

# Syntax:

commander rps convert <filename.rps> --app <original non-encrypted M4 rps> --mic

<keys.json> --encrypt <keys.json> --sign <keys.json>

# 5.6 Example: SiWG917M111MGTBA (Common Flash Mode)

The manufacturing procedure with security configurations for SiWG917M111MGTBA in Common flash mode is as follows:

# 1. Backup - IPMU Calibration

o commander manufacturing read taipmu --out filename.bin -d SiWG917M111MGTBA

#### 2. MBR Provisioning

commander manufacturing provision --mbr default -d SiWG917M111MGTBA

# 3. Security Key Programming

- Activation Code Generation for PUF (PUF Initialization)

commander manufacturing init --mbr ta\_mbr\_SiWG917M111MGTBA.bin -d SiWG917M111MGTBA

- Power cycle the device

- Generate Keys with Simplicity Commander

commander util genkeyconfig --outfile commanderkeys.json -d SiWG917M111MGTBA

- Provision Static Keys

commander manufacturing provision --keys commanderkeys.json -d SiWG917M111MGTBA

# 4. MBR Programming to Enable Security Configurations

- Security Level 3 enabled in the updated\_mbr\_fields.json file

commander manufacturing provision --mbr ta\_mbr\_SiWG917M111MGTBA.bin --data

updated mbr fields.json -d SiWG917M111MGTBA

- 5. RF Calibration refer to section RF Calibration.

- 6. Convert NWP and M4 images to match Security Level 3

- Security NWP Image:

commander rps convert secured\_SiWG917-B.2.12.2.1.0.9.rps --taapp SiWG917-B.2.12.2.1.0.9.rps --mic commanderkeys.json --encrypt commanderkeys.json --sign commanderkeys.json

- Security M4 Image: commander rps convert secured\_si91x\_hello\_world.rps --app si91x\_hello\_world.rps --mic commanderkeys.json --encrypt commanderkeys.json --sign commanderkeys.json

# 7. Flash NWP and M4 Images

- TA Image: commander rps load secured\_SiWG917-B.2.12.2.1.0.9.rps -d SiWG917M111MGTBA

- M4 Image: commander rps load secured\_si91x\_hello\_world.rps -d SiWG917M111MGTBA

**Note:** If you want to update the boot configurations in eFuse refer to the section <u>Boot Configurations Update – eFuse</u> and for debug lock refer to the section <u>Debug Lock</u>.

# 5.7 Disable Security

The disabling of security does not erase the PUF activation code or erase keys, only re-writes the MBR. If the security configurations are programmed in eFuse, you cannot disable the security.

The following command is to disable the security.

# Syntax:

commander manufacturing provision --mbr default -d <full opn> [--skipload] [--pinset n]

**Note:** If you want to enable security again, you need to give only one command, refer to the section <u>Programming MBR with security parameters</u>.

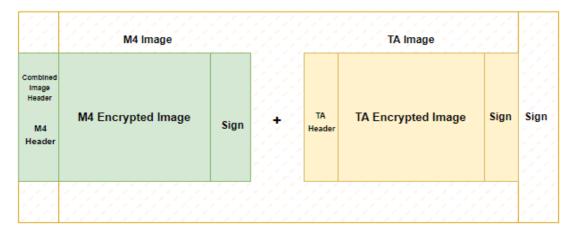

# 6 Combined Image (NWP + M4)

The combined image is a single image which is obtained by combining the TA and M4 images. The process of creating the combined image involves encrypting both the TA and M4 images separately, and then adding a RPS header and signature. In case of non-secure firmware, signature is not added.

- Combined Image RPS header format is same as the M4 RPS header format with few reserved bytes changed.

- · Signature for complete combined image is calculated and appended at the end of image.

- MIC computation and signature maintains the integrity and confidentiality of the combined image.

- Encryption of combined image is discarded as it would add overhead for firmware to decrypt and store into flash location. The TA and M4 images are encrypted individually.

Figure 6.1: Combined Image (NWP + M4)

The following table lists the process to create and flash a combined image for Common Flash and Dual Flash mode devices.

| Steps | Description                 | Security | Command (Syntax)                                                                                                                                                                                                               |

|-------|-----------------------------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | TA Image with combined flag | Disabled | commander rps convert <filename.rps>taapp <original non-encrypted="" rps="" ta="">combinedimage</original></filename.rps>                                                                                                      |

| 1     |                             | Enabled  | commander rps convert <filename.rps>taapp <original non-encrypted="" rps="" ta="">mic <keys.json>encrypt <keys.json>sign <keys.json>combinedimage</keys.json></keys.json></keys.json></original></filename.rps>                |

| 2     | M4 Image with combined flag | Disabled | commander rps convert <filename.rps>app <original m4="" non-encrypted="" rps="">combinedimage</original></filename.rps>                                                                                                        |

|       |                             | Enabled  | <pre>commander rps convert <filename.rps>app <original<br>non-encrypted M4 rps&gt;mic <keys.json>encrypt<br/><keys.json>sign <keys.json>combinedimage</keys.json></keys.json></keys.json></original<br></filename.rps></pre>   |

| 2     | Combine TA and M4 Images    | Disabled | <pre>commander rps convert <combined_image.rps>app <m4_image_combinedflag.rps>taapp <ta_image_combinedflag.rps></ta_image_combinedflag.rps></m4_image_combinedflag.rps></combined_image.rps></pre>                             |

| 3     |                             | Enabled  | <pre>commander rps convert <combined_image.rps>app <m4_image_combinedflag.rps>taapp <ta_image_combinedflag.rps>sign <keys.json></keys.json></ta_image_combinedflag.rps></m4_image_combinedflag.rps></combined_image.rps></pre> |

| 4     | Flash the Combined Image    |          | You can flash the combined image using the OTA process only. Refer to the HTTP OTAF example.                                                                                                                                   |

**Table 6.1: Combined Image Steps**

# 7 Boot Configurations Update - eFuse

This section provides the commands to read and write eFuse data along with the list of the available configurations in eFuse that can be programmed by the user.

Once all the development and testing work is complete, the next step would be to program the eFuses. It is important to note that this is a permanent and one-time operation.

SiWG917 has eFuse memory of 1024 bytes. This memory is divided into four sections with control to enable write locks for each of these sections.

| eFuse section | Byte Range |

|---------------|------------|

| R1            | 0-127      |

| R2            | 128-255    |

| R3            | 256-767    |

| R4            | 768-1024   |

**Note:** You cannot write to eFuse through the M4 application image or through NWP via APIs. You must have an active JTAG connection to write the eFuse bits.

#### 7.1 Read eFuse Data

You can read the eFuse data/contents to an .json (for example, efuse\_value.json) file.

The command to read efuse data is as follows.

#### Syntax:

commander manufacturing read efuse --out efuse\_value.json -d <full opn>

# **Example**

commander manufacturing read efuse -out efuse\_value.json -d SiWG917M111MGTBA

# 7.2 Write eFuse Data

In the case of eFuse (one time programmable) data, simplicity commander CLI first checks whether the requested update is possible (since bits can only be set to 1 and never cleared). Then it will ask for your confirmation.

The possible eFuse configurations are mentioned in the section Possible Boot Configurations.

You can modify the eFuse bits in the efuse\_value.json file which is read in the section Read eFuse Data and use the following command which are used to write efuse data into flash.

#### Syntax:

- commander manufacturing write efuse --data efuse\_value.json -d <OPN Number> [--skipload] [--pinset n] [-s jlinkserialno] [--noprompt] [--dryrun]

- --noprompt: It is possible to skip the confirmation, although users need to note that this is a one-time operation.

- --dryrun: It is possible to check the results of the operation before physically going ahead with the one-time programming.

#### Example

commander manufacturing write efuse --data efuse\_value.json -d SiWG917M111MGTBA skipload --dryrun

# 7.3 Possible Boot Configurations

The following table shows the available user configurable eFuse bits.

**Note:** The following fields can also be configured in MBR, you can modify them during development in the MBR and program in the eFuse once all the development and testing is completed.

| # | Field                           | Description                                                                                                                                                                                                                                                                                                         | Number<br>of bits | Default Setting                                                      | Default<br>value<br>in<br>NWP<br>eFuse |

|---|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------|----------------------------------------|

| 1 | safe_upgrade_frm_host           | When set to 1- upgrade the  NWP and M4 images from backup, instead of overwriting directly  M4 OTA and Public keys from backup, instead of overwriting directly When set to 0, the images or the keys will be directly overwritten to the target locations based on the target address which comes from RPS header. | 1                 | Enabled                                                              | 1                                      |

| 2 | ta_secure_boot_enable           | 1: Secure boot is enabled for NWP 0: Secure boot is disabled in NWP                                                                                                                                                                                                                                                 |                   | Disabled                                                             | 0                                      |

| 3 | ta_anti_roll_back               | 1: Anti roll back check is enabled for NWP firmware (will not allow to update old versions) 0: Anti roll back check is not enabled for NWP firmware                                                                                                                                                                 | 1                 | Anti roll back check is<br>not enabled for NWP<br>firmware           | 0                                      |

| 4 | ta_digital_signature_validation | Digital signature validation is enabled for NWP firmware     Digital signature validation is disabled for NWP firmware                                                                                                                                                                                              | 1                 | Digital signature validation is disabled for NWP firmware            | 0                                      |

| 5 | m4_anti_roll_back               | 1: Anti roll back check is<br>enabled for M4 firmware (will not<br>allow to update old versions)<br>0: Anti roll back check is not<br>enabled for M4 firmware                                                                                                                                                       | 1                 | Disabled                                                             | 0                                      |

| 6 | m4_digital_signature_validation | Digital signature validation is enabled for M4 firmware     Digital signature validation is disabled for M4 firmware                                                                                                                                                                                                | 1                 | Disabled                                                             | 0                                      |